文章目录

-

- 概要

- 整体架构流程

- 技术名词解释

- 技术细节

- 小结

概要

提示:这里可以添加技术概要

锁相环是一种反馈系统,其中电压控制振荡器(VCO) 和相位比较器相互连接,使得振荡器 可以相对于参考信号维持恒定的相位角度。锁相环可用来从固定的低频信号生成稳定的 输出高频信号等

整体架构流程

提示:这里可以添加技术整体架构

PLL 的基本模块为误差检波器(由鉴频鉴相器和电荷泵组成)、环路滤波器、VCO 和反馈分 频器。负反馈强制误差信号 e(s) 在反馈分频器输出和基准频率处于锁相和锁频状态且 FO=NFREF 的点处接近 0。 根据图 ,当系统使用 PLL 来生成高于输入的频率时,VCO 会以角频率ωO 振荡。该信 号的一部分会通过分频器以 1/N 的比率回馈到误差检波器。这种经过分频的频率会馈入误差检 波器的其中一个输入端。本例中,另一路输入为固定参考信号。误差检波器会比较两个输入端 的信号。这两个信号输入的相位和频率相等时,误差为常数,环路则处于“锁定”条件下。

技术名词解释

提示:这里可以添加技术名词解释

锁相环 (phase locked loop)是一种利用相位同步产生的电压,去调谐压控振荡器以产生目标频率的负反馈控制系统。根据自动控制原理,这是一种典型的反馈控制电路,利用外部输入的参考信号控制环路内部振荡信号的频率和相位,实现输出信号频率对输入信号频率的自动跟踪,一般用于闭环跟踪电路。是无线电发射中使频率较为稳定的一种方法,主要有VCO(压控振荡器)和PLL IC (锁相环集成电路),压控振荡器给出一个信号,一部分作为输出,另一部分通过分频与PLL IC所产生的本振信号作相位比较,为了保持频率不变,就要求相位差不发生改变,如果有相位差的变化,则PLL IC的电压输出端的电压发生变化,去控制VCO,直到相位差恢复,达到锁相的目的。能使受控振荡器的频率和相位均与输入信号保持确定关系的闭环电子电路。

技术细节

提示:这里可以添加技术细节

1.相位噪声

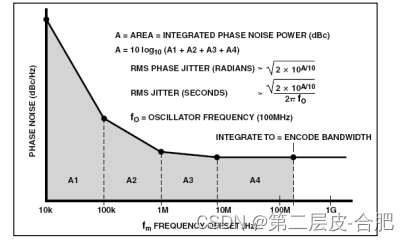

对一个给定载波功率的输出频率来说,相位噪声是载波功率相对于给定的频率偏移处 (频率合成器通常定义 1kHz 频率偏移)1-Hz 的带宽上的功率,单位为 dBc/Hz @ offset frequency。锁相环频率合成器的带内相位噪声主要取决于频率合成器,VCO 的贡献很小。 相位噪声的测量需要频谱分析仪。注意一点,普通频谱分析仪读出的数据需要考虑分 辨带宽的影响,并且频谱仪要具有 Marker Noise 的功能,这样可以直接从频谱仪上得到 Marker Noise(PN)的值,如果没有 Marker Noise 的功能,则需要通过 Marker 在指定偏 移处测量噪声的值,然后再通过公式(MKR Noise = MKR Value - 10logRBW)得出相噪 值。高端的频谱分析仪或相位噪声测试仪往往可以直接给出单边带相位噪声。 相位噪声是信号在频域的度量。在时域,与之对应的是时钟抖动(jitter),它是相位噪声在 时间域里的反映,大的时钟抖动在高速 ADC 应用中会严重恶化采样数据的信噪比,尤其是当 ADC 模拟前端模拟前端信号的频率较高时,更是要求低抖动的时钟。图 2 形象地描述了时钟抖动。

时钟抖动可以通过相位噪声积分得到,具体实现如下:计算从给定的起始频率偏移处到结 束频率(通常定义为两倍输出频率)偏移处的相位噪声和 A,单位为 dBc;对 A 进行取对数操 作;求相位抖动均方值(rms phase jitter),单位为弧度;将弧度值转换成时间单位,秒或者皮秒。

2.参考杂散

锁相环中最常见的杂散信号就是参考杂散。这些杂散信号会由于电荷泵源电流与汇电流的 失配,电荷泵漏电流,以及电源退耦不够而增大。在接收机设计中,杂散信号与其他干扰信号 相混频有可能产生有用信号频率从而降低接收机的灵敏度。锁相环处于锁定状态时,电荷泵会 周期性的(频率等于鉴相频率)产生交替变换(正负)脉冲电流给环路滤波器。环路滤波器对 其进行积分产生稳定的控制电压。

当电荷泵处于三态的时候(绝大部分时间是如此),电荷泵的漏电流是杂散的主要来源。电荷泵 漏电流经过环路滤波器形成控制电压,以调谐 VCO,这样就相当于对 VCO 进行调频(FM), 反映在 VCO 的输出,就会出现杂散信号。电荷泵漏电流越大,鉴相频率越低,这种参考杂散越 大。在鉴相频率相等的条件下,电荷泵的漏电流与电荷泵电流的比值越大,由电荷泵漏电流引 起的参考杂散会越大。ADI 的 PLL 产品漏电流大部分在 1nA 左右的水平上。

3.锁定时间

锁相环从一个指定频率跳变到另一个指定频率(在给定的频率误差范围内)所用的时间就 是锁定时间。频率跳变的步长取决于 PLL 频率合成器工作在限定的系统频带上所能达到的最大 的频率跳变能力。 例如,GSM-900,频率步长最大为 45MHz,而 GSM-1800 为 95MHz。容许的频率误差分 别为 90Hz 和 180Hz。PLL 频率合成器必须在小于 1.5 个时隙(GSM 的一个时隙是 577us)内 达到锁定。 锁定时间还需要另外一个指标来度量,即 PLL 频率合成器输出达到给定相位误差范围所用的时 间。

小结

提示:这里可以添加总结

例如:

本位主要介绍一些PLL的基本概念,以及一些基本指标