1. CPU vs GPU

大家可以简单的将CPU理解为学识渊博的教授,什么都精通;而GPU则是一堆小学生,只会简单的算数运算。可即使教授再神通广大,也不能一秒钟内计算出500次加减法。因此,对简单重复的计算来说,单单一个教授敌不过数量众多的小学生。在进行简单的算数运算这件事上,500个小学生(并发)可以轻而易举打败教授。

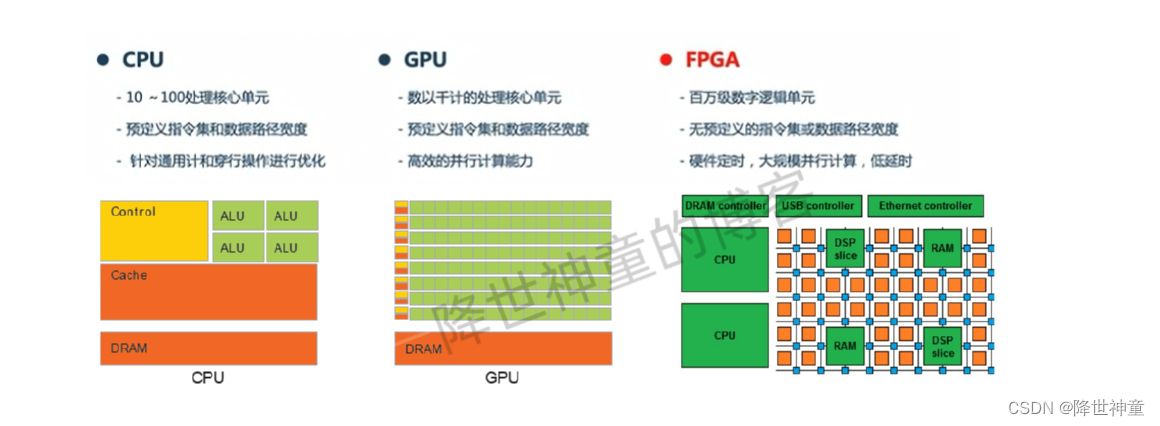

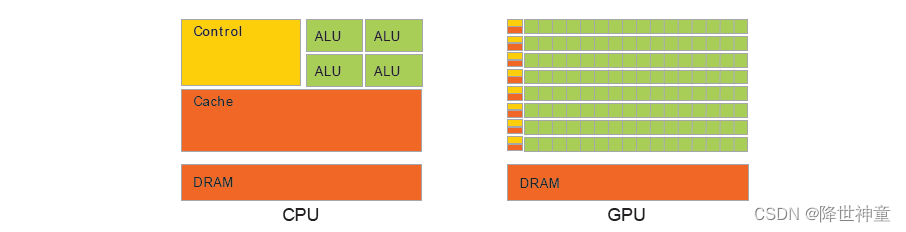

可以看到,CPU和GPU的最大不同在于架构。CPU适用于广泛的应用场景(学识渊博),可以执行任意程序;而GPU则专为多任务而生,并发能力强。

具体来讲,就是多核,一般的CPU有2核、4核、8核等;而GPU则可能会有成百上千核

GPU构造与CPU相似,包含控制单元(control unit)、算术逻辑单元(ALU)、快取(cache)及动态随机存取记忆体(DRAM)等元件。差别在于,GPU的控制单元、ALU及快取设计较为简易,且数量较多,导致GPU擅于处理大量简单的工作(例如渲染图像)

可以看到,CPU内部cache以及控制部分占据了很大一部分片上面积,因此计算单元占比很少。GPU只有很简单的控制单元,剩下的大部分都被计算单元占据,因此CPU的核数有限,而GPU则轻松堆出上千核。只不过CPU中每个核的能力好比教授,而GPU的每个核的能力好比一个小学生。

为什么GPU需要这么多核心?

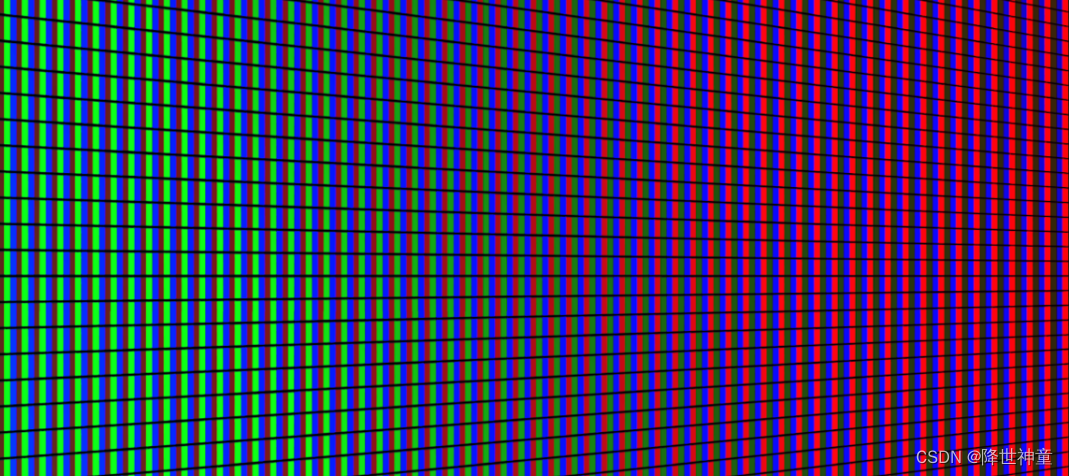

想一想计算机上的一张图是怎么表示的?无非就是屏幕上的一个个像素:

我们需要为每个像素进行计算,而且是相同的运算,就好比刚才例子中的小学生计算计加法一样。

对于屏幕来说一般会有上百万个像素,如果我们要串行的为每一个像素进行运算效率就太低了。因此可以让GPU中的每一个核心去为相应的像素进行计算。由于GPU中有很多核心,因此并行计算可以大幅提高速度。除了GPU的核心数比较多之外,GPU的工作方式也比较奇怪。

GPU的工作方式:

对于CPU来说,不同的核心可以执行不同的机器指令,coreA在运行word线程的同时coreB上可以运行浏览器线程,这就是所谓的多指令多数据,MIMD(Multiple Instruction, Multiple Data)

而GPU则不同,GPU上的这些核心必须整齐划一的运行相同的机器指令,只是可以操作不同的数据,这就好比这些小学生在某个时刻必须都进行加法计算,不同的地方在于有的小学生可能需要计算1+1,有的要计算2+6等等,变化的地方仅在于操作数,这就是所谓的单指令多数据,SIMD(Single Instruction, Multiple Data)

因此,我们可以看到GPU的工作方式和CPU是截然不同的。

除了这种工作方式之外,GPU的指令集还非常简单,不像CPU这种复杂的处理器。如果你去看CPU的编程手册就会发现CPU负责的事情非常多,如中断处理、内存管理、IO等。这些对于GPU来说都是不存在的,可以看到GPU的定位非常简单,就是纯计算,GPU绝不是用来取代CPU的,CPU只是把一些GPU非常擅长的事情交给它,GPU仅仅是用来分担CPU工作的配角。

GPU擅长什么?

比较适合GPU的计算场景是这样的:计算简单、重复计算,因此如果你的计算场景和这里的图像渲染相似那么使用GPU就很合理了。因此对于图形图像计算、天气预报以及神经网络等都适用于GPU

难倒CPU的问题,就是当它被交付大量的琐碎工作,虽然它能够处理,却会浪费太多宝贵时间;大材小用,就像米其林主厨被派去夜市炸鸡排,耽搁了高档餐厅的业务。相较下,GPU的控制单元与ALU设计简单、快取空间较小,拥有大量核心数及比较高的吞吐量,适合快速处理简单的运算,而GPU除了渲染图像之外,GPU在需要密集资料运算的领域也崭露头角,比如在大数据分析、机器学习、AI人工智慧发展等方面,GPU已成为推动电脑科学向前迈进的重要功臣。

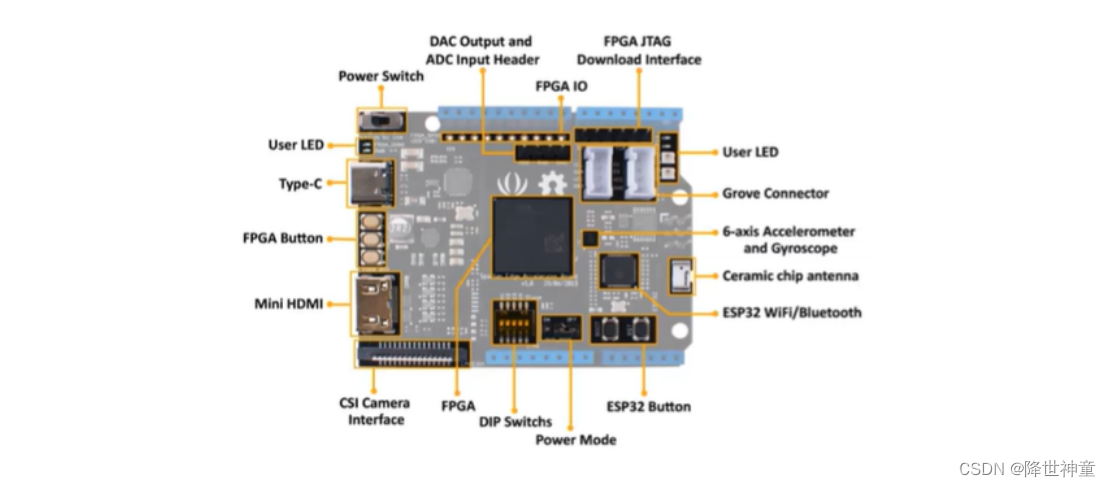

2. FPGA

FPGA是什么呢?

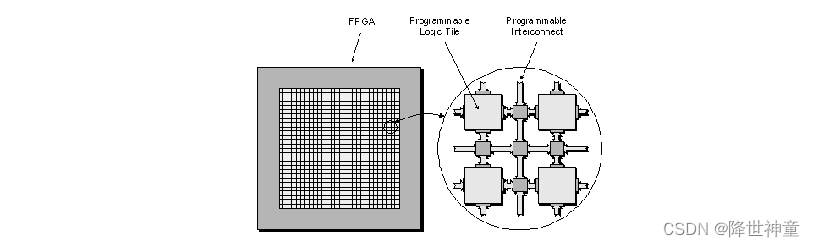

FPGA(Field Programmable Gate Array),即现场可编程门阵列,它可以通过硬件描述语言(Verilog或VHDL)描述一个电路设计,通过配套的EDA工具综合与布局,并烧录至 FPGA来实现设计需要

目前所有的FPGA或eFPGA都包含大量的可编程逻辑单元和可编程布线单元。逻辑单元可以实现一小部分数字逻辑,而布线则连接这些逻辑单元来组成更大的数字电路。

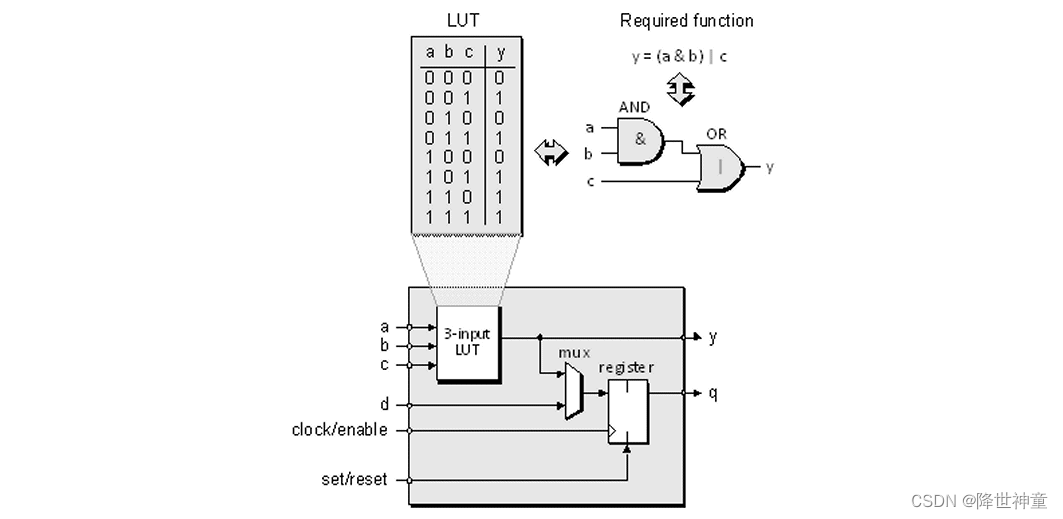

FPGA的基本原理:按照门电路的组合逻辑和时序逻辑,利用查找表(Look-Up-Table,简称LUT),实现快速的数据计算。

可编程逻辑单元:

数字电路可以细分为组合逻辑和时序逻辑。 FPGA中实现组合逻辑的部分就是查找表(LUT),时许逻辑则依靠寄存器。若干个LUT和寄存器相互连接则构成了一个逻辑簇。不同的FPGA公司所定义的逻辑簇的结构也是不同的。 逻辑簇结构有2大好处,第一逻辑簇中的互联速度要快,可以提高FPGA速度; 第二, 逻辑簇的应用可以简化排版布线的复杂度,缩短综合时间。

可编程布线单元:

与定制电路不同, FPGA的布线资源都是预制好的, 因此预制的布线资源能够连接绝大多数的逻辑单元(簇)。 对于用户设计好的项目,通过控制一系列的开关来满足特定单元间的互联。 这也就使得布线资源占据了FPGA的绝大部分面积, 而且复杂的布线网络中控制开关过多的话会大大降低FPGA的运行频率。如果减少布线资源, 则会加大EDA软件算法的难度,而且会导致电路布局布线失败。

因此如何设计逻辑簇和与之配合的布线资源,使其达到速度和面积的均衡,而且还要考虑到EDA软件算法的难度,执行时间以及内存占用, 这是每个FPGA厂商的核心中的核心

CPU的难点是其硬件结构,软件指令集则不是厂家的主要难点。 而FPGA的硬件结构原理并不是主要技术壁垒,但是其EDA软件的核心算法则是每个公司的长期积累的成果

CPU vs GPU vs FPGA: