WM8960简介

WM8960内部 ADC和 DAC都为24

I2S 总线接口

2S 总线用于主控制器和音频CODEC 芯片之间传输音频数据。

I2S 接口需要3 根信号线(如果需要实现收和发,那么就要4根信号线,收和发分别使用一根信号线):

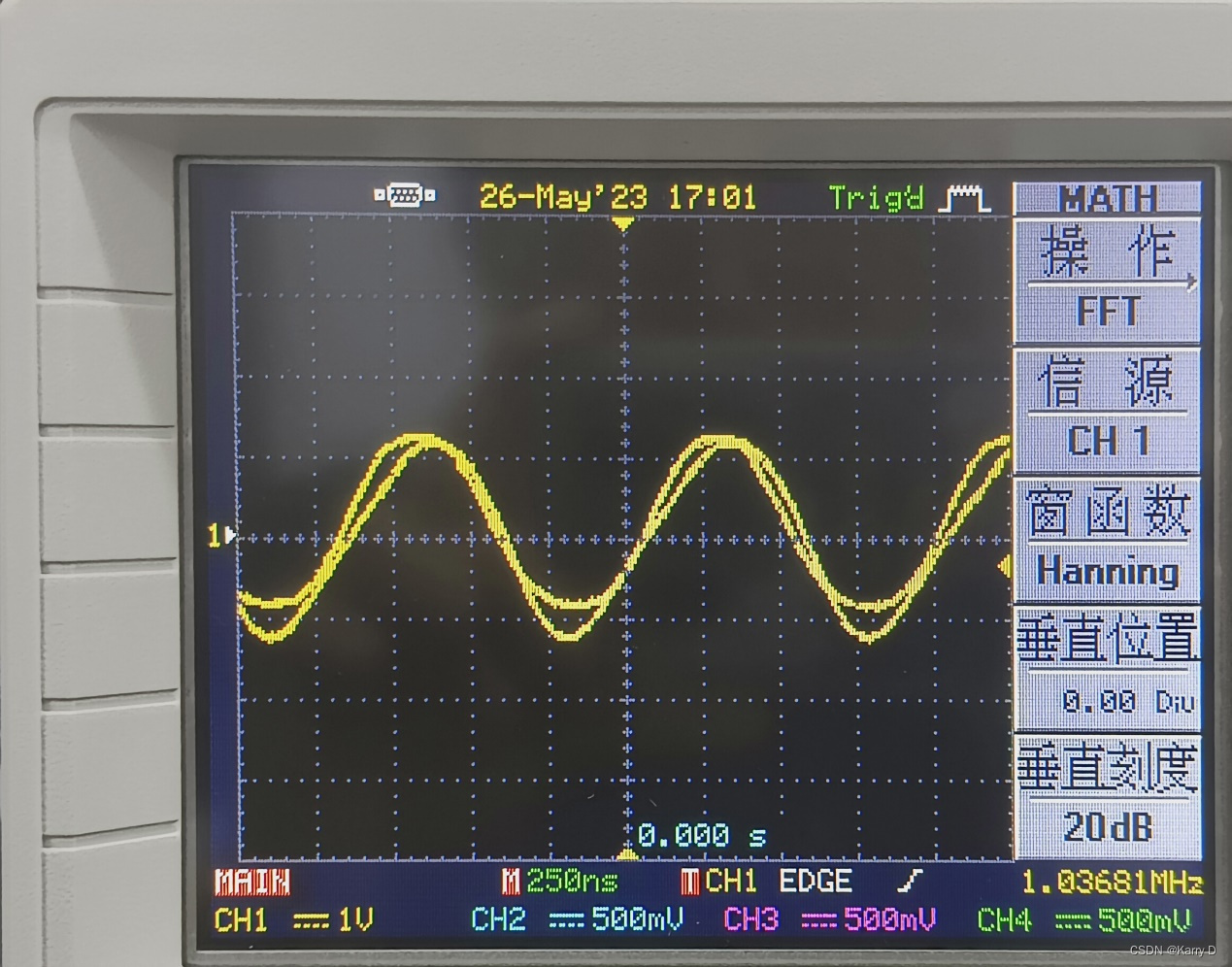

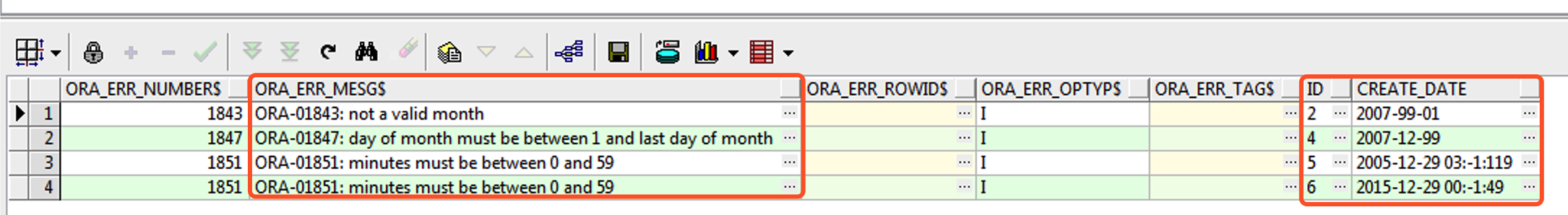

SCK:串行时钟信号,也叫做位时钟(BCLK),音频数据的每一位数据都对应一个SCK,立体声都是双声道的,因此SCK=2×采样率×采样位数。比如采样率为44.1KHz、16 位的立体声音频,那么SCK=2×44100×16=1411200Hz=1.4112MHz。

WS:字段(声道)选择信号,也叫做LRCK,也叫做帧时钟,用于切换左右声道数据,WS 为“1”表示正在传输左声道的数据,WS 为“0”表示正在传输右声道的数据。WS 的频率等于采

样率,比如采样率为44.1KHz 的音频,WS=44.1KHz。

SD:串行数据信号,也就是我们实际的音频数据,如果要同时实现放音和录音,那么就需要2 根数据线,比如WM8960 的ADCDAT 和DACDAT,就是分别用于录音和放音。不管音频

数据是多少位的,数据的最高位都是最先传输的。数据的最高位总是出现在一帧开始后(LRCK变化)的第2 个SCK 脉冲处。

MCLK为了使音频CODEC 芯片与主控制器之间能够更好的同步,会引入另外一个叫做MCLK 的信号,也叫做主时钟或系统时钟,一般是采样率的256 倍或384 倍。

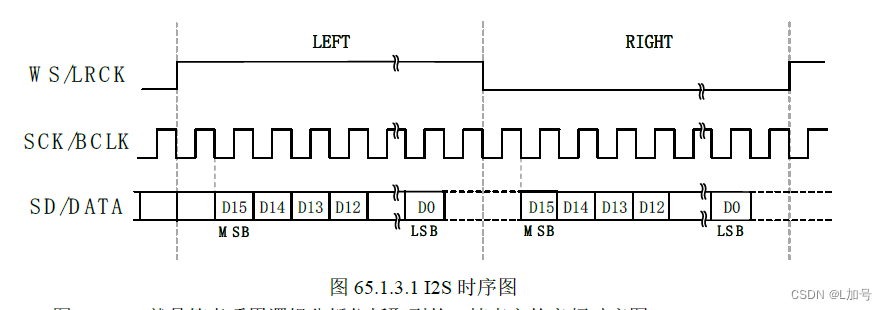

DATA 数据相对于LRCK 和SCLK 位置的不同,出现了Left Justified(左对齐)和Right Justified(右对齐)两种格式

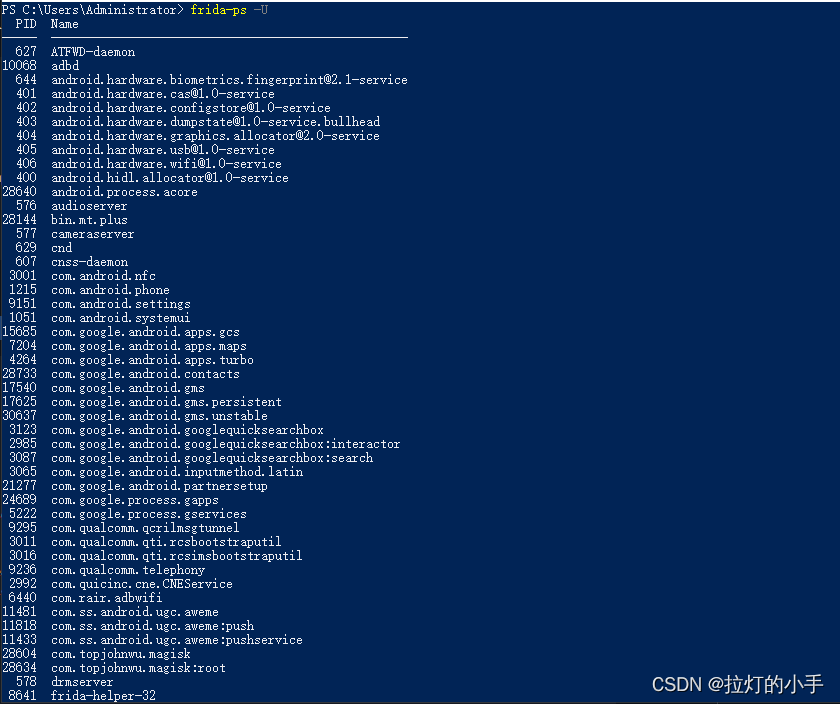

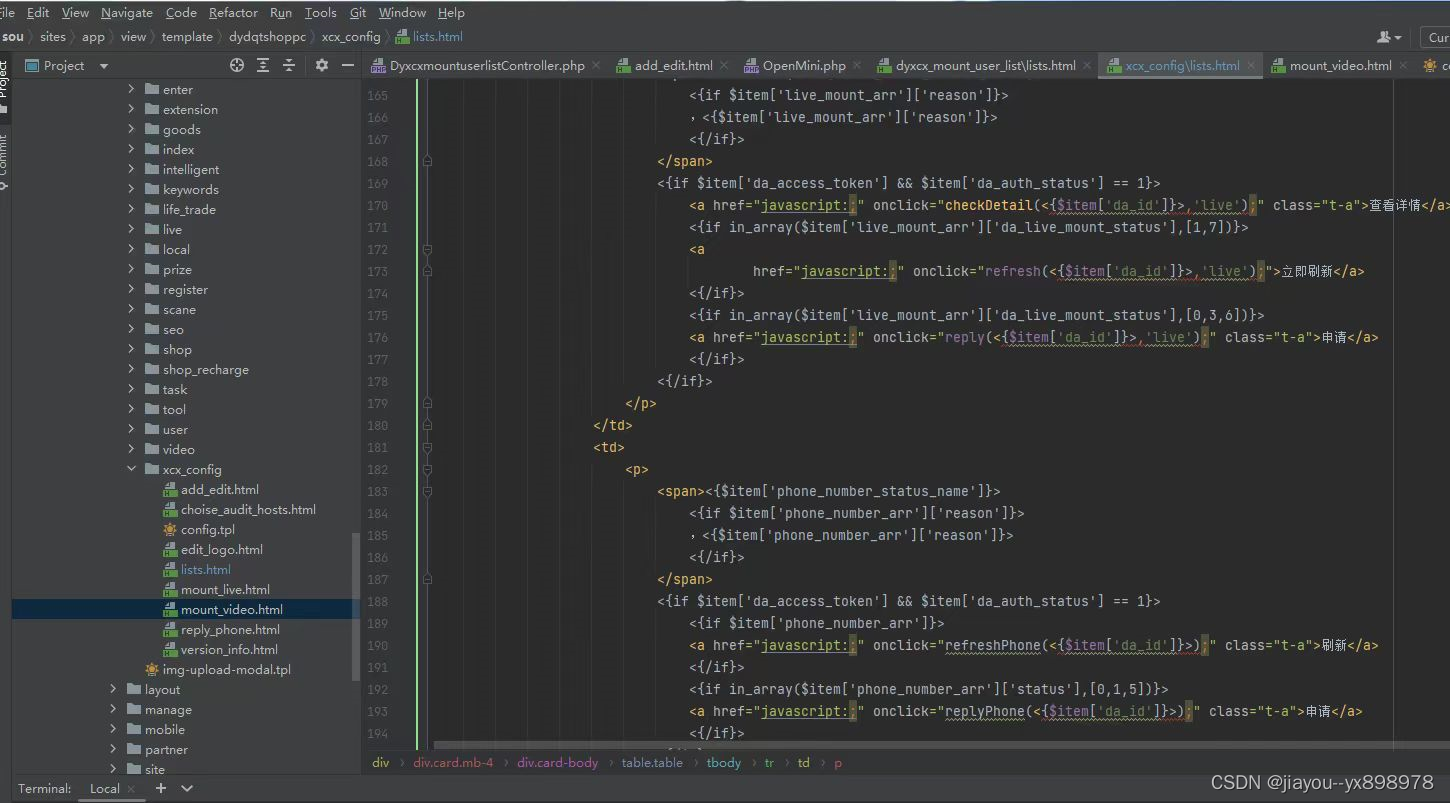

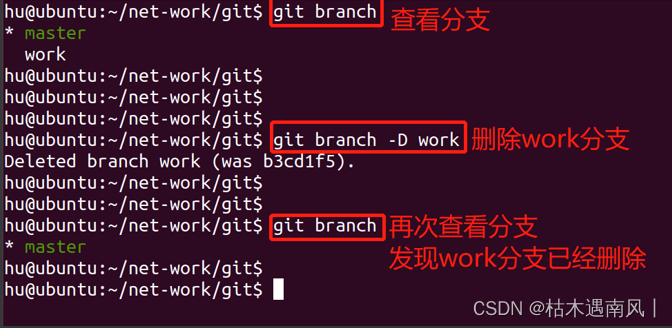

WM8960驱动

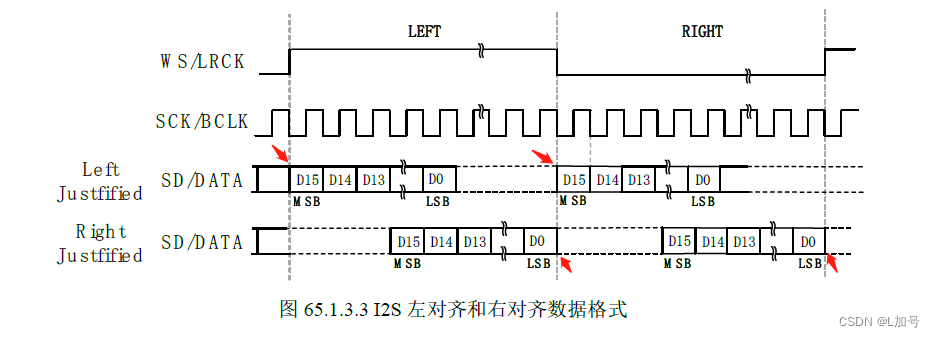

1. 2.4版本I2C1设备接口

codec: wm8960@1a {

compatible = "wlf,wm8960";

reg = <0x1a>;

clocks = <&clks IMX6UL_CLK_SAI2>; //时钟源为SAI2

clock-names = "mclk";

wlf,shared-lrclk;

};

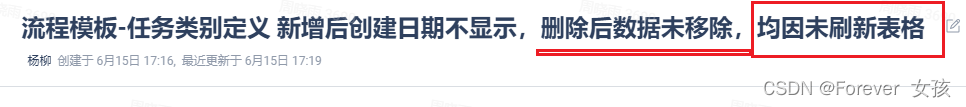

wlf,shared-lrclk 这是一个 bool类型的属性,如果添加了此属性, WM8960的 R24寄存器的 LRCM位 (bit2)就会置 1。当 LRCM为 1的时候只有当 ADC和 DAC全部关闭以后 ADCLRC和 DACLRC时钟才会关闭。

wlf,capless 这也是一个 bool类型的属性, 如果添加了此属性, OUT3引脚将会使能,并且为了响应耳机插入响应事件, HP_L和 HP_R这两个引脚都会关闭。

2. SAI音频接口设备树

NXP原厂编写

&sai2 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_sai2

&pinctrl_sai2_hp_det_b>;

assigned-clocks = <&clks IMX6UL_CLK_SAI2_SEL>,

<&clks IMX6UL_CLK_SAI2>;

assigned-clock-parents = <&clks IMX6UL_CLK_PLL4_AUDIO_DIV>;

assigned-clock-rates = <0>, <12288000>;

status = "okay";

};