2023上半年软考系统分析师科目一整理-03

- 1. 嵌入式

1. 嵌入式

- 嵌入式系统已被广泛应用到各行各业。嵌入式系统是一个内置于设备中,对设备的各种传感器进行管理与控制的系统。通常,根据系统对时间的敏感程度可将嵌入式系统划分为( A )两种,而实时系统又可分为强实时(Hard Real-Time)系统和弱实时(WeakReal-Time)系统;如果从安全性要求看,嵌入式系统还可分为( C )。

A.嵌入式系统和嵌入式实时系统 B.控制系统和业务系统

C.安全攸关系统和非安全攸关系统 D. CPS系统和非CPS系统

A.高可靠系统和高安全系统 B.实时系统和强实时系统

C.安全攸关系统和非安全攸关系统楼 D.网络系统和分布式系统

- 嵌入式软件开发方法与传统软件开发方法存在较大差异,( D )的说法对嵌入式软件开发而言是错误的。

A.嵌入式软件开发的结果通常需要固化在目标系统的存储器或处理器内部存储器资源中

B.嵌入式软件的开发一般需要专门的开发工具,目标系统和测试设备

C.嵌入式软件对安全性和可靠性的要求较高

D.嵌入式软件开发不用考虑代码的规模

- 由于处理器芯片在不同领域应用时,需要考虑对环境的适应性。通常,我们把芯片分为民用级、工业级和军用级。( )分别是民用级、工业级和军用级芯片的标准工作温度范围。

A: -10℃ ~+70℃ 、-40℃~+80℃ 、-50℃~+150℃

B. 0℃~+70℃ 、-30℃~+85℃ 、-60℃~+150℃

C. 0℃~+70℃ 、-40℃~+85℃ 、-55℃~+150℃

D. -0℃+60℃、-40℃+90℃ 、-55℃~+150℃

- 嵌入式实时系统存在许多调度算法。如果调度程序根据任务的紧急程度确定该任务的优先级,任务紧急程度高,被赋予的优先级就高,可被优先执行。这种调度算法称之为( D )。

A.最早截止时间优先(Earliest Deadline First, EDF)算法

B.最低松弛度优先(Least Laxity First, LLF算法

C.单调速率调度(Rate Monotonic Scheduling, RMS)算法

D.抢占式优先级调度(Preemptive Priority Scheduling, PPS)算法

-

RISC-V 是基于精简指令集计算原理建立的开放指令集架构,以下关于 RISC-V 的说法中,不正确的是©。

A.RISC-V 架构不仅短小精悍,而且其不同的部分还能以模块化的方式组织在一 起,从而试图通过一套统一的架构满足各种不同的应用场景

B. RISC-V 基础指令集中只有 40 多条指令,加上其他模块化护展指令总共也就几 十条指令

C. RISC-VISA 可以免费使用,允许任何人设计、制造和销售 RISC-V 芯片和软件 D.RISC-V 也是 X86 架构的一种,它和 ARM 架构之间存在很大区别 -

IEEE-1394 总线采用菊花链的拓扑结构时,可最多支持 63 个节点。当 1394 总线支持 1023 条桥接总线时,最多可以采用菊花链的拓扑结构互连©个节点。

A.1023

B.1086

C.64449

D.645535

以下关于总线的说法中,正确的是(C)。

A.串行总线适合近距离高速数据传输,但线间串扰会导致速率受限

B.并行总线适合长距离数据传输,易提高通信时钟频率来实现高速数据传输

C.单总线结构在一个总线上适应不同种类的设备,设计复杂导致性能降低

D.半双工总线只能在一个方向上传输信息

按照总线中数据线的多少,可分为并行总线和串行总线。并行总线是含有多条双向数据线的总线,它可以实现一个数据的多位同时传输,总线中数据线的数量决定了可传输一个数据的最大位数(一般为8的倍数)。由于可以同时传输数据的各位,所以并行总线具有数据传输速率高的优点。但由于各条数据线的传输特性不可能完全一致,当数据线较长时,数据各位到达接收端时的延迟可能不一致,会造成传输错误,所以并行总线不宜过长,适合近距离连接。大多数的系统总线属于并行总线;串行总线是只含有一条双向数据线或两条单向数据线的总线,可以实现一个数据的各位按照一定的速度和顺序依次传输。由于按位串行传输数据对数据线传输特性的要求不高,在长距离连线情况下仍可以有效地传送数据,所以串行总线的优势在于远距离通信。但由于数据是按位顺序传送的,所以在相同的时钟控制下,数据传输速率低于并行总线。大多数的通信总线属于串行总线。

在单总线结构中计算机的各个部件均与系统总线相连,所以它又称为面向系统的单总线结构。在单总线结构中,CPU与主存之间、CPU与I/O设备之间、I/O设备与主存之间、各种设备之间都通过系统总线交换信息。单总线结构的优点是控制简单方便,扩充方便。但由于所有设备部件均挂在单一总线上,使这种结构只能分时工作,即同一时刻只能在两个设备之间传送数据,这就使系统总体数据传输的效率和速度受到限制,这是单总线结构的主要缺点。

- 在计算机体系结构设计时,通常在CPU 和内存之间设置小容量的 Cache 机制, 以提高CPU数据输入输出速率。通常当 Cache已存满数据后,新数据必须替换(淘汰) Cache 中旧数据。常用的数据替换算法包括(A)。

A. 随机算法、先进先出(FIFO) 和近期最少使用(LRU)

B. 随机算法、先进后出(FILO) 和近期最少使用(LRU)

C. 轮询调度(RRS)、 先进先出(FIFO) 和近期最少使用(LRU)

D. 先进先出(FIFO)、近期最少使用(LRU)和最近最常使用(MRU)

常用的数据替换算法包括随机算法、先进先出(First In and First Out, FIFO)算法、近期最少使用(Least Recently Used, LRU)算法和最不经常使用页置换(Least Frequently Used (LFU))算法。

(1)随机算法。这是最简单的替换算法。随机法完全不管cache块过去、现在及将来的使用情况,简单地根据一个随机数,选择一块替换掉。

(2)先进先出(First In and First Out, FIFO)算法。按调入cache的先后决定淘汰的顺序,即在需要更新时,将最先进入cache的块作为被替换的块。这种方法要求为每块做一记录,记下它们进入cache的先后次序。这种方法容易实现,而且系统开销小。其缺点是可能会把一些需要经常使用的程序块(如循环程序)替换掉。

(3)近期最少使用(Least Recently Used, LRU)算法。LRU算法是把CPU近期最少使用的块作为被替换的块。这种替换方法需要随时记录cache中各块的使用情况,以便确定哪个块是近期最少使用的块。LRU算法相对合理,但实现起来比较复杂,系统开销较大。通常需要对每一块设置一个称为“年龄计数器”的硬件或软件计数器,用以记录其被使用的情况

(4)最不经常使用页置换(Least Frequently Used (LFU))算法,要求在页置换时置换引用计数最小的页,因为经常使用的页应该有一个较大的引用次数。但是有些页在开始时使用次数很多,但以后就不再使用,这类页将会长时间留在内存中,因此可以将引用计数寄存器定时右移一位,形成指数衰减的平均使用次数。LFU的复杂度以及计数器规模都比LRU大,LRU只关注近期访问情况,而LFU会统计累计访问次数作为淘汰的依据。

选项B中的先进后出算法(FILO)是按调入cache的先后决定淘汰的顺序,即在需要更新时,将最后进入cache的块作为被替换的块。不适合Cache替换,它会降低Cache的命中率;选项D的最近最常使用(MRU)算法是把CPU近期最常使用的块作为被替换的块,也不适合Cache替换,且不常用。选项C中的轮询调度(RRS)不是Cache替换算法,适用于服务器调度。

- 雷达设计人员在设计数字信号处理单元时,其处理器普遍采用DSP芯片(比如:TI公司的TMS320C63xx),通常DSP芯片采用哈佛(HarVard)体系结构,以下关于哈佛结构特征的描述,不正确的是( )。

A.程序和数据具有独立的存储空间,允许同时取指令和取操作数,并允许在程序空间或数据空间之间互传数据

B.处理器内部采用多总线结构,保证了在一个机器周期内可以多次访问程序空间和数据空间

C.哈佛体系结构强调的是多功能,适合多种不同的环境和任务,强调兼容性

D.处理器内部采用多处理单元,可以在一个指令周期内同时进行运算

哈佛结构是一种将程序指令存储和数据存储分开的存储器结构。哈佛结构是一种并行体系结构,它的主要特点是将程序和数据存储在不同的存储空间中,即程序存储器和数据存储器是两个独立的存储器,每个存储器独立编址、独立访问。 与两个存储器相对应的是系统的4条总线:程序和数据的数据总线与地址总线。这种分离的程序总线和数据总线可允许在一个机器周期内同时获得指令字(来自程序存储器)和操作数(来自数据存储器),从而提高了执行速度,提高了数据的吞吐率。又由于程序和数据存储在两个分开的物理空间中,因此取址和执行能完全重叠。中央处理器首先到程序指令存储器中读取程序指令内容,解码后得到数据地址,再到相应的数据存储器中读取数据,并进行下一步的操作(通常是执行)。程序指令存储和数据存储分开,可以使指令和数据有不同的数据宽度。 哈佛结构能在一个机器周期内同时获取指令字与操作数,但做不到一个机器周期内多次访问存储器.

- 某16位AD芯片中标注电压范围是-5V~+5V,请问该款AD芯片的分辨率是( C )。

A.10V

B.0.0763mV

C.0.1526mV

D.0.3052mV

2的16次方=65536。 10/65536*1000=0.152588mV

-

以下关于多核处理器的说法中,不正确的是( )。

A.采用多核处理器可以降低计算机系统的功耗和体积

B.SMP、BMP和MP是多核处理器系统通常采用的三种结构,采用哪种结构与应用场景相关,而无须考虑硬件的组成差异

C.在多核处理器中,计算机可以同时执行多个进程,而操作系统中的多个线程也可以并行执行

D.多核处理器是将两个或更多的独立处理器封装在一起,集成在一个电路中. -

多核操作系统的设计方法不同于单核操作系统,一般要突破(D )等方面的关键技术。

A.总线设计、Cache设计、核间通信、任务调度、中断处理、同步互斥

B.核结构、Cache设计、核间通信、可靠性设计、安全性设计、同步互斥

C.核结构、Cache设计、核间通信、任务调度、中断处理、存储器墙设计

D.核结构、Cache设计、核间通信、任务调度、中断处理、同步互斥 -

多核CPU环境下进程的调度算法一般有全局队列调度和局部队列调度两种。( )属于全局队列调度的特征。

A.操作系统为每个CPU维护一个任务等待队列

B.操作系统维护一个任务等待队列

C.任务基本上无需在多个CPU核心间切换,有利于提高Cache命中率

D.当系统中有一个CPU核心空闲时,操作系统便从该核心的任务等待队列中选取适当的任务执行 -

以下关于CPU和GPU的叙述中,错误的是(C)。

A.CPU适合于需要处理各种不同的数据类型、大量的分支跳转及中断等场合

B.CPU利用较高的主频、高速缓存(Cache)和分支预测等技术来执行指令

C.GPU采用MISD(Mutiplc Instuction Single Data)并行计算架构

D.GPU的特点是比CPU包含更多的计算单元和更简单的控制单元

计算机系统中有多种实现数据输入和输出的控制方式,其中占用 CPU 时间最多的是(A)。

A.程序查询方式 B.中断方式 C.DMA 方式 D.缓冲方式

在计算机中,I/O系统可以有5种不同的工作方式,分别是程序控制方式、程序中断方式、DMA工作方式、通道方式、I/O处理机。从程序控制方式到I/O处理机,CPU的介入程度,消耗CPU资源数呈递减的趋势。

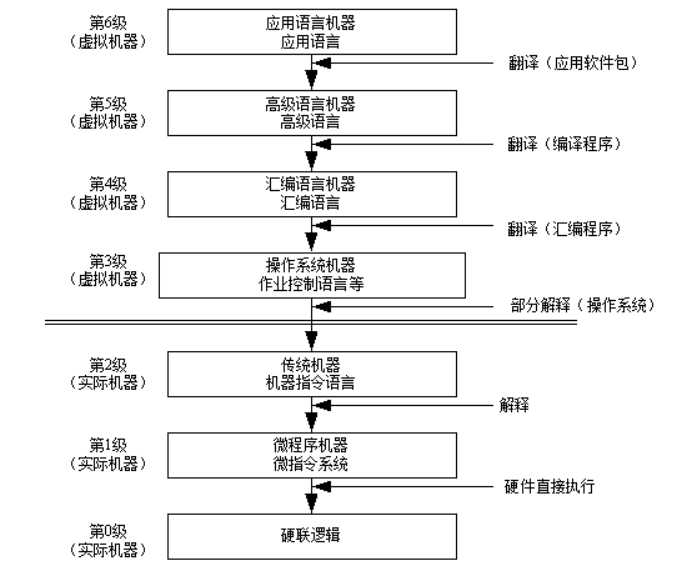

- 计算机系统是一个硬件和软件综合体,位于硬联逻辑层上面的微程序是用微指令编写的。以下叙述中,正确的是,(A)。

A.微程序般由硬件执行

B.微程序一般是由操作系统来调度和执行

C.微程序一般用高级语言构造的编译器期译后来执行

D.微程序一般用高级语言构造的解释器件来解释执行

(1)硬联逻辑级。这是计算机的内核,由门、触发器等逻辑电路组成。

(2)微程序级。这一级的机器语言是微指令集,程序员用微指令编写的微程序一般直接由硬件执行。

(3)传统机器级。这一级的机器语言是该机的指令集,程序员用机器指令编写的程序可以由微程序进行解释。

(4)操作系统级。从操作系统的基本功能来看,一方面它要直接管理传统机器中的软硬件资源,另一方面它又是传统机器的延伸。

(5)汇编语言级。这一级的机器语言是汇编语言,完成汇编语言翻译的程序称为汇编程序。

(6)高级语言级。这一级的机器语言就是各种高级语言,通常用编译程序来完成高级语言翻译的工作。

(7)应用语言级。这一级是为了使计算机满足某种用途而专门设计的,因此,这一级的机器语言就是各种面向问题的应用语言。

-

计算机系统中,(D)方式是根据所访问的内容来决定要访问的存储单元,常用在(B)存储器中。

A.顺序存取 B.直接存取 C.随机存取 D.相联存取

A.DRAM B.Cache C.EEPROM D.CD-ROM -

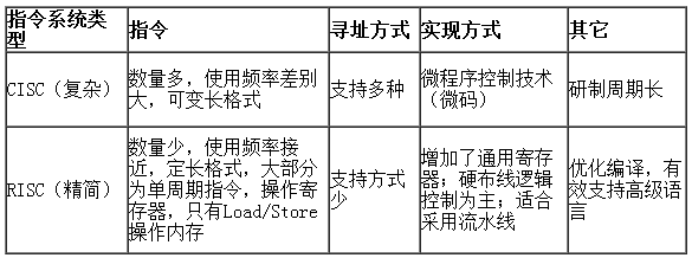

RISC指令系统的特点包括(C)。

①指令数量少

②寻址方式多

③指令格式种类少

④指令长度固定

(18)A.①②③ B.①②④ C.①③④ D.②③④

以 下 关 于 复 杂 指 令 集 计 算 机 (Complex Instruction Set Computer,CISC) 的叙述中,正确的是(D)。

A.只设置使用频度高的一些简单指令,不同指令执行时间差别很小

B.CPU 中设置大量寄存器,利用率低

C.常采用执行速度更快的组合逻辑实现控制器

D.指令长度不固定,指令格式和寻址方式多

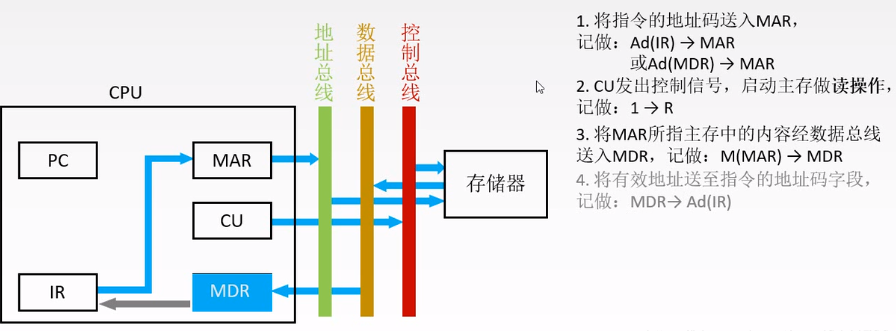

17. 执行 CPU 指令时,在一个指令周期的过程中,首先需从内存读取要执行的指令,此时先要将指令的地址即(C)的内容送到地址总线上。

A.指令寄存器(IR) B. 通用寄存器 (GR) C.程序计数器 (PC) D. 状态寄存器 (PSW)

- 流水线的吞吐率是指流水线在单位时间里所完成的任务数或输出的结果数。设某流水线有 5 段,有 1 段的时间为 2ns ,另外 4 段的每段时间为 lns,利用此流水线完成 100 个任务的吞吐率约为(B)个/s 。

A.500×l06 B.490×l06 C.250×l06 D.167×l06

(2+1+1+1+1)+(100 - 1)*2=204ns

所以每秒吞吐率为:(100/204)109=490106

- 在高速缓存 (Cache) -主存储器构成的存储系统中,(A)。

A.主存地址到 Cache 地址的变换由硬件完成,以提高速度

B.主存地址到 Cache 地址的变换由软件完成,以提高灵活性

C.Cache 的命中率随其容量增大线性地提高

D.Cache 的内容在任意时刻与主存内容完全一致

Cache 的替换算法中,(B)算法计数器位数多,实现困难。

A.FIFO B.LFU C.LRU D.RAND

(1)随机算法。这是最简单的替换算法。随机法完全不管cache块过去、现在及将来的使用情况,简单地根据一个随机数,选择一块替换掉。

(2)先进先出(First In and First Out,FIFO)算法。按调入cache的先后决定淘汰的顺序,即在需要更新时,将最先进入cache的块作为被替换的块。这种方法要求为每块做一记录,记下它们进入cache的先后次序。这种方法容易实现,而且系统开销小。其缺点是可能会把一些需要经常使用的程序块(如循环程序)替换掉。

(3)近期最少使用(Least Recently Used,LRU)算法。LRU算法是把CPU近期最少使用的块作为被替换的块。这种替换方法需要随时记录cache中各块的使用情况,以便确定哪个块是近期最少使用的块。LRU算法相对合理,但实现起来比较复杂,系统开销较大。通常需要对每一块设置一个称为“年龄计数器”的硬件或软件计数器,用以记录其被使用的情况。

(4)最不经常使用页置换(Least Frequently Used (LFU))算法,要求在页置换时置换引用计数最小的页,因为经常使用的页应该有一个较大的引用次数。但是有些页在开始时使用次数很多,但以后就不再使用,这类页将会长时间留在内存中,因此可以将引用计数寄存器定时右移一位,形成指数衰减的平均使用次数。

![[CVPR 2023] Imagic:使用扩散模型进行基于文本的真实图像编辑](https://img-blog.csdnimg.cn/img_convert/5c990ea9f7674e7e1bab2c127615339c.png)