目录

- 一、简介

- 二、数据通信过程

- 2.1 通信总过程总结

- 2.2 具体协议规则

- 2.2.1 时钟极性与时钟相位

- 2.2.2 SPI模式

- 2.2.3 图文实例讲解

- 2.3 SPI协议优缺点总结

- 三、其他相关链接

一、简介

SPI(Serial Peripheral nterface,串行外设接口) 协议是一种高速高效率、全双工的通信总线,允许CPu与低速的外围设备之间进行同步串行数据的传输,主要是用同步的时钟信号对串行的数据同时进行发送和接收操作,从而实现全双工。常用于短距离通讯,主要是在嵌入式系统中。

SPI接口在芯片内部只占用四根线,主要有两条数据线、一根片选线和一根时钟信号线。这四根线分别对应SPI协议传输时的四种信号,分别有主机输出信号MOSI、从机输入信号MISO、片选信号sS n以及输出的时钟信号SCK。

SPI协议里定义了主模式和从模式两种工作方式,在协议里规定工作在主模式下的模块是主机,工作在从模式下的模块是从机。主机和从机之间按照SPI时序要求进行数据交换。

一个典型的SPI系统应包括只能有一个主机、一个或多个从机。

SPI接口只能有一个主机,但可以有一个或多个从机。下图显示了主机和从机之间的SPI连接。

| 名称 | 解释 |

|---|---|

| SCLK | Serial Clock (output from master); master输出至slave的通讯时钟 |

| MOSI | Master Output, Slave Input(output from master); 自master输出至slave的数据线 |

| MISO | SOMI: Master Input, Slave Output(output from slave); 自slave输出至master的数据线 |

| SS | Slave Select (active low, outputfrom master). master对slave的片选信号,自master输出至slave,低有效。 |

多个从机可与单个SPI主机一起使用。从机可以采用常规模式连接,或采用菊花链模式连接。

常规SPI模式

在常规模式下,主机需要为每个从机提供单独的片选信号。一旦主机使能(拉低)片选信号,MOSI/MISO线上的时钟和数据便可用于所选的从机。如果使能多个片选信号,则MISO线上的数据会被破坏,因为主机无法识别哪个从机正在传输数据。

菊花链模式:

在菊花链模式下,所有从机的片选信号连接在一起,数据从一个从机传播到下一个从机。在此配置中,所有从机同时接收同一SPI时钟。来自主机的数据直接送到第一个从机,该从机将数据提供给下一个从机 。

二、数据通信过程

2.1 通信总过程总结

SPI数据通信的流程可以分为以下四步:

1、主设备发起信号,将CS/SS拉低,选择片选,启动通信。

2、主设备通过发送时钟信号,来告诉从设备进行写数据或者读数据操作(采集时机可能是时钟信号的上升沿(从低到高)或下降沿(从高到低),根据spi模式而定),它将立即读取数据线上的信号,这样就得到了一位数据(1bit)。

3、主机(Master)将要发送的数据写到发送数据缓存区(Memory),缓存区经过移位寄存器(缓存长度不一定,看单片机配置),串行移位寄存器通过MOSI信号线将字节一位一位的移出去传送给从机,同时MISO接口接收到的数据经过移位寄存器一位一位的移到接收缓存区。

4、从机(Slave)也将自己的串行移位寄存器(缓存长度不一定,看单片机配置)中的内容通过MISO信号线返回给主机。同时通过MOSI信号线接收主机发送的数据,这样,两个移位寄存器中的内容就被交换。

当MASTER片选一个SLAVE时,每向SLAVE发送一个周期的SCLK信号,都会有1bit的数据从MOSI发送至slave,与此同时,slave每收到一个周期的SCLK信号,都会从MISO向master发送1bit的数据。这种全双工通讯,是由硬件保证的(MASTER与HOST中各有一个移位寄存器作为收发数据的缓存)。

2.2 具体协议规则

SPI总线上的数据传输由串行时钟SCK进行同步处理,串行时钟SCK由SPI主机产生,每个时钟周期仅发送1bit数据。,SPI有四种操作模式——SPI0、SPI1、SPI2和SPI3,它们的区别是定义了在时钟脉冲的哪条边沿转换(toggles)输出信号,哪条边沿采样输入信号,还有时钟脉冲的稳定电平值(就是时钟信号无效时是高还是低)。每种模式由一对参数刻画,它们称为时钟极性(clock polarity)CPOL与时钟相位(clock phase)CPHA。

2.2.1 时钟极性与时钟相位

CPOL表示SCK的空闲状态的有效电平;

CPOL = 0表示SCK的空闲状态是低电平,CPOL = 1表示SCK的空闲状态是高电平;

CPHA规定了数据的采样时间;

CPHA = 0表示在SCK的有效电平的第一个跳变边沿进行数据采样,CPHA = 1表示在SCK的有效电平的第二个跳边沿进行数据采样;

2.2.2 SPI模式

SPI0: 时钟极性和时钟相位均为0。

SCK空闲状态为低电平,SCK由低电平到高电平的跳变,所以数据采样是在上升沿,数据发送是在下降沿。主机数据在第一个跳变沿被从机采样。

SPI1: 时钟极性为0,时钟相位为1。

SPI2: 时钟极性为1,时钟相位为0。

SPI3: 时钟极性和时钟相位均为1。

SCK空闲状态为高电平,SCK由高电平到低电平的跳变,所以数据采集是在上升沿,数据发送是在下降沿。主机数据在第二个跳变沿被从机采样,数据发送在第1个边沿。

这四种传输模式,使用最广泛的是SPI0和SPI3模式。在使用SPI系统的时候,可根据数据传输的要求,通过对时钟极性和时钟相位寄存器位的配置就可以得到所需的传输模式。不同模式下的时序客参考SPI协议详解。

此外,SPI数据传输方式还有MSB传输和LSB传输两种。MSB传输表明主机和从机首先传输数据的最高位,LSB恰恰相反,主机和从机首先传输数据的最低位。在SPI系统寄存器里需要设置相应的寄存器位,通过配置寄存器来决定数据传输的方式。

2.2.3 图文实例讲解

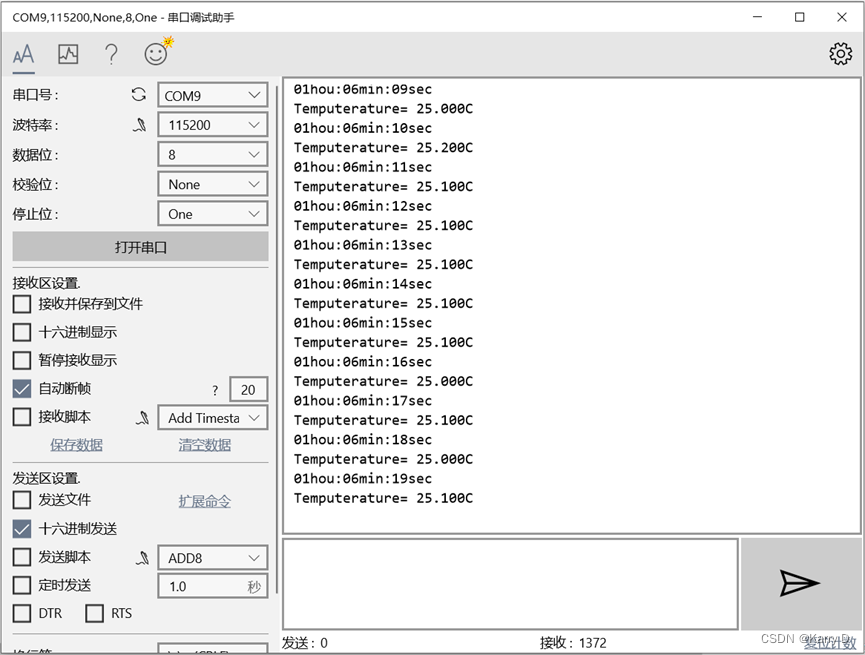

下图示例中简单模拟SPI通信流程,主机拉低NSS片选信号,启动通信,并且产生时钟信号,上升沿触发边沿信号,主机在MOSI线路一位一位发送数据0X53,在MISO线路一位一位接收数据0X46,如下图所示,本例中主从设备只进行单写和单读方式,其实是同时可以读写,如下MOSI中主机发送数据0x53,但是忽略从机发的数据:

注意:

最开始第一个时钟周期片选信号拉低之后数据传输过程:

以spi0(SCK空闲状态为低电平,数据采样是在上升沿)举例 :

我们来关注SCK的第一个时钟周期,在时钟的前沿采样数据(上升沿,第一个时钟沿),在时钟的后沿输出数据(下降沿,第二个时钟沿)。首先来看主器件,主器件的输出口(MOSI)输出的数据bit1,在时钟的前沿被从器件采样,那主器件是在何时刻输出bit1的呢?bit1的输出时刻实际上在SCK信号有效以前,比SCK的上升沿还要早半个时钟周期。bit1的输出时刻与SSEL信号没有关系。再来看从器件,从器件的输入口MISO同样是在时钟的前沿采样从器件输出的bit1的,那从器件又是在何时刻输出bit1的呢。从器件是在SSEL信号有效后,立即输出bit1,尽管此时SCK信号还没有起效,记住关键,spi是全双工,在发数据的同时,也会进行数据的采集,主从设备采集数据的时钟相位一致,本例中都是上升沿采样。

2.3 SPI协议优缺点总结

优点

无起始位和停止位,因此数据位可以连续传输而不会被中断;

没有像I2C这样复杂的从设备寻址系统;

数据传输速率比I2C更高(几乎快两倍);

分离的MISO和MOSI信号线,因此可以同时发送和接收数据;

极其灵活的数据传输,不限于8位,它可以是任意大小的字;

非常简单的硬件结构。从站不需要唯一地址(与I2C不同)。从机使用主机时钟,不需要精密时钟振荡器/晶振(与UART不同)。不需要收发器(与CAN不同)。

缺点

使用四根信号线(I2C和UART使用两根信号线);

无法确认是否已成功接收数据(I2C拥有此功能);

没有任何形式的错误检查,如UART中的奇偶校验位;

只允许一个主设备;

没有硬件从机应答信号(主机可能在不知情的情况下无处发送);

没有定义硬件级别的错误检查协议;

与RS-232和CAN总线相比,只能支持非常短的距离;

三、其他相关链接

Linux下spi网卡dm9051驱动移植及驱动调试分析总结