目录

- 1 概述

- 2 IP功能

- 3 IP端口

- 4 收发数据时序

- 4.1 Uart_tx接口

- 4.2 Uart_rx接口

- 5 获取IP地址

1 概述

本文用于讲解yueyin IP 的uart ip(串口/rs422/rs485/rs232)的功能,以及使用说明,方便使用者快速上手。

版本:V1.0.0

编制:月隐

2 IP功能

yueyin_ip_uart是月隐编写的串口IP,实现串口的底层收发时序,可灵活设置奇偶校验位,数据位的位宽等参数,收发指示信号明显好用。

串口的协议为:1bit起始位,data W(8) bit 数据位,1bit停止位。

具体的串口协议时序这里不做详细介绍,若需了解请自行查找资料。

3 IP端口

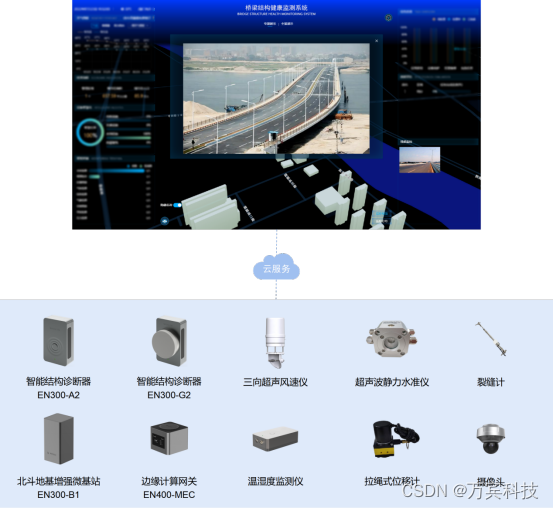

图 1 IP 端口截图

Uart ip的端口如上图所示,说明如下表所示:

表 1 端口说明表

序号 端口名 功能说明 备注

-

BPS_SET 波特率设置,单位bps,例如9600bps -

clk 时钟,建议是波特率的10倍以上 -

rst_n 复位,低电平有效 -

uart_rx 串口的rx端口 -

uart_tx 串口的tx端口 -

uart_tx_data 发送的串口数据 -

uart_tx_data_vld 发送的串口数据有效指示信号 -

uart_tx_data_rdy 发送的串口数据接收准备好信号 -

uart_rx_data 接收的串口信号 -

uart_rx_data_vld 接收的串口信号有效指示信号 -

parity_error 奇偶校验错误的指示信号,为1时有误,为0时无误 PARITY_EN为1时才有效

表 2 常数设置说明

序号 常数名 功能说明 备注

-

CLK_Fre Clk的时钟频率,单位HZ,例如100_000_000 HZ -

DATA_W 串口时序协议中的数据位的位宽,可设置5,6,7,8bit,最常用的为8 -

parity_en 奇偶校验位使能,1使能,0不使能 -

parity_mode 校验模式,0偶校验(even),1奇校验(odd)

4 收发数据时序

4.1 Uart_tx接口

uart_tx_data_vld与uart_tx_data_rdy同时为高时,uart_tx_data有效,如下图所示发送的有效数据,FE,09处的波形。

图 2 TX时序

4.2 Uart_rx接口

uart_rx_data_vld为高时,代表uart_rx_data有效,如下图所示接收到数据fe,09时的波形时序。

图 3 rx时序

5 获取IP地址

yueyin uart ip