一、文件说明

- 工艺库

1、

.db格式:二进制工艺库文件;. lib格式:可读工艺库文件(包含 operating _ conditions ).

二、. synopsys _ dc . setup

- 搜索路径定义

1、

set_search _ path [ list ./ home xxx(路径)]

2、多个地址可用\符号换行

- 设计环境( PVT :工艺角、电压和温度)

1、库设置

1). 目标工艺库(标准单元综合库):

set target_library {/home/xxx/PDK/typical.db}

2). 符号库:set symbol _ library {/ home / xxx/ PDK / typical . sdb}

3). 设置 IP 库:set synthetic_library [list dw_foundation.sldb]

4). 链接库(上一层调用底层已综合模块时的链接库,可以与 target library 相同,包含所有用到的库):set link_library {* ./home/xxx/PDK/typical.db}

5). 其他环境设置(不在link library内):set_min_library {slow.db} -min_version {fast.db}

6). 设置不同工作条件下对应库:set_operating_conditions -analysis_type on_chip_variation -max ss_v1p08_125c -min ff_v1p32_-40c1)). ss_v1p08_125c和 ff_v1p32_-40c为最差和最好工作条件名,在 lib 中查找;

2)). slow 和 fast 分别为最差和最好 lib 名,在 search_path 中设置。2、设置线负载模型、模式

1).

set_wire_load_model -name ForQA1)). model名在 lib 中查找

2)). slope:斜率(长度/扇出)2).

set_wire_load_mode toptop 顶层模式:适合扁平化设计、 enclosed 包围模式、 segmented 分段模式:

3、系统接口特性

1).

set_drive XXX [list XXX]用于输入端口输入电阻设置(单位与工艺库中一致,典型为0.05),端口列表可为"[ all _ inputs ]“或”{分别列举}"。

2).

set_driving_cell -lib_cell XXX -pin XXX -no_design_rule [get_ports XXX]设置端口驱动单元

3).

set_input_transition XXX [get_ports XXXX ]设置端口固定转换时间(单位与工艺库中一致)

- 命名规则

1、 大写字母替换小写字母:

define_name_rules BORG -restricted "A-Z" -replacement_char "a-z"

三、 TCL

- 路径设置

1、

set REPORT "../report":使用时用 “$REPORT” 代替 “…/report”

- 读取设计

1、读入 design:

analyze -format verilog ./WORK/temp.v

2、建立 design,后面跟 module 名:elaborate temp一般最顶层模块最后读入,作为Current Design

- 设计规则约束

1、设置最大转换时间:

set_max_transition XXX [XXX]一般设置为周期的10%;all_inputs / all_outputs / find design

2、设置最大扇出负载(通过插入 buffer 以符合约束):

set_max_fanout XXX [XXX]

- 设计优化约束

1、时钟约束

1).时钟约束:

create_clock -name CLK -period 5 -waveform {0 2.5} [get_ports CLK ]

2).时钟抖动:set_clock_uncertainty -setup xxx [get_clocks CLK]

/set_clock_uncertainty -hold xxx [get_clocks CLK]【可以设置为10% ClockPeriod】

3).内部产生时钟约束:create_generated_clock -name CLKdiv2 -edges{2 4 6} -source CLK [get_pins Udiv/Q]

4).对于时钟禁止加入缓冲,时钟树在布局布线时加入:set_dont_touch_network [get_clocks CLK]

5).输入端口驱动:set_drive 0 [get_clocks CLK]【设置驱动阻抗】参考:时钟的约束方法

2、复位信号约束

1).

set_dont_touch_network [get_ports reset]:【不加buffer】

2).set_dont_touch_network [get_pins -hierarchical reset_ int]:【不加buffer】

3).set_drive 0 [get_ports reset]

4).set_ideal_network [get_nets -hierarchical reset_int] -no_propagate:【不做时序分析】3、输入输出延迟

1).

set_input_delay:【可以设置为40% ClockPeriod 】

2).set_output_delay:【同步设计寄存器输出可以不加】4、时序例外

1).

set_false_path -from [get_ports reset]

2).set_false_path -from [get_clocks CLK1] -to [get_clocks CLK2]5、面积约束

set_max_area 0【获得最小面积】

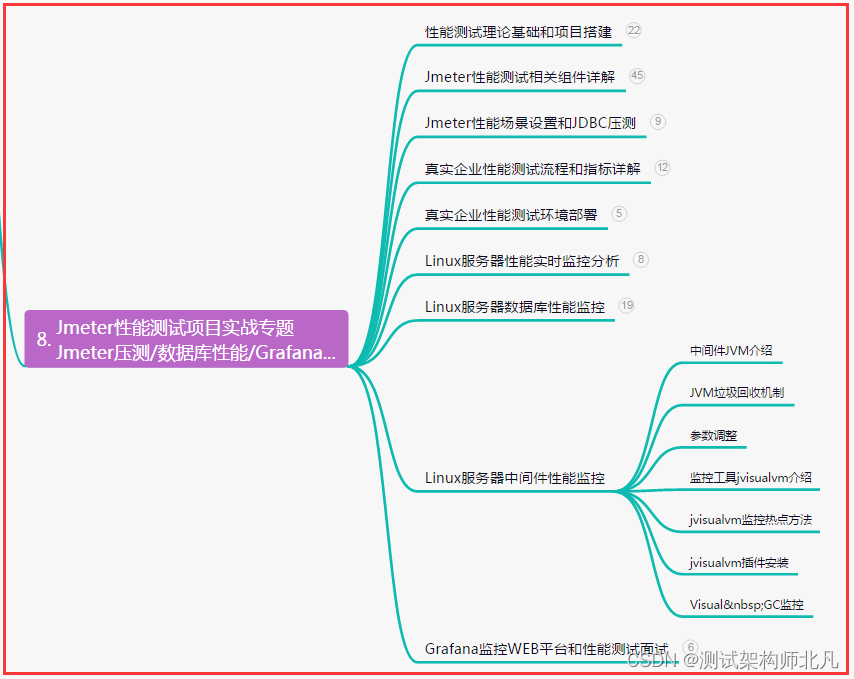

- 编译(映射+优化)

1、compile -no_autoungroup

2、compile ultra参考:DC学习综合与优化

- 返回报告、保存结果

1、输出综合后网表文件:

write_file -f verilog -hierarchy -output /home/working_design.v

2、输出延迟文件:write_sdf -version 1.0 /home/working_design.sdf

3、输出面积报告:report_area -hierarchy > /home/area_hier.rpt

4、输出时序违例文件:report_constraints -all_violators -verbose > /home/constraints.rpt

微信公众号:通信随笔XIDIAN