在前面介绍了静态互补CMOS逻辑,这里主要说明有比逻辑和动态CMOS逻辑。

CMOS组合逻辑_vtc曲线_沧海一升的博客-CSDN博客介绍了静态互补CMOS逻辑https://blog.csdn.net/qq_21842097/article/details/107456036

一、有比逻辑

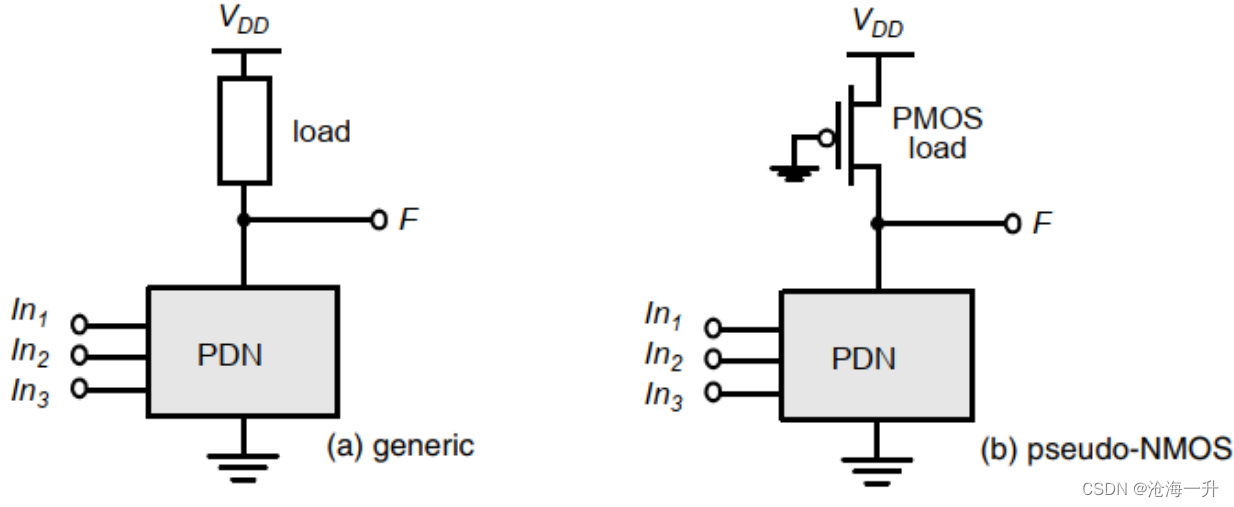

1、伪NMOS

因为互补CMOS优点是全轨输出,静态功耗低,但是代价是稳定输出的时候,有一半的管子属于冗余的。如果当资源(如面积)有限时,我们需要另外一种静态CMOS的设计方法来减少MOS管的数目。因此有了有比逻辑这种设计方法,当扇入是N时,它仅需N+1个MOS管;但于此同时它需要以降低稳定性和额外的静态功耗作为代价。

额定低电压不是0,因为存在PDN和伪NMOS的通路。这降低了噪声容限,并且引起了静态功耗。

之所以称之为有比逻辑,是因为输出电平和功能取决于NMOS和PMOS的尺寸比。不同于无比逻辑,无比逻辑高低电平与尺寸无关。

其做法为将PUN替换为一个无条件负载器件。通常为一个栅极接地的PMOS负载(伪NMOS门)。

虽然静态功耗限制了伪NMOS的应用,但是当面积是最重要的因素时,伪NMOS还是可以使用的,因此还是可以看到伪NMOS有时应用在大扇入的电路中。

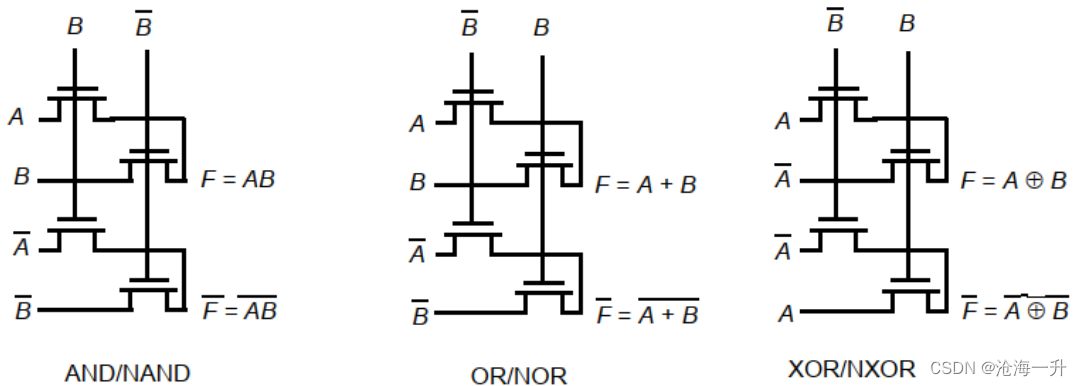

2、差分串联电压开关逻辑(DCVSL)

差分级联电压开关逻辑,目的在于完全消除静态电流并提供轨到轨的电压摆幅的有比逻辑。用两个PMOS和两个对偶的互斥输入的NMOS实现逻辑功能,其原理为差分逻辑和正反馈:

- 差分门要求每个输入都具有互补形式,同时也产生互补输出。

- 反馈机制保证不需要负载时将其关断

优点在于:

- 消除静态电流,提供轨到轨输出

- 同时产生了输出和其反信号,节省了额外的反相器,避免使用反相器引起的时差问题。这实际上受益于差分逻辑。

这就是DCVSL的结构,下面的两个N网络输出为互斥的信号,通过上面两个PMOS的加强实现输出的稳定。基本原理是下面两个N网络总会有一个导通,输出L0,L0使得上面两个PMOS中一个导通,抬高另外一个PMOS的输入使其关闭,实现信号的稳定。实现稳态的过程为有比电路,存在稳定延时。如XOR-XNOR门:

当然,DCVSL也存在一定缺陷:

- 在翻转期间PMOS和PDN会同时导通一段时间,产生短路通路,造成渡越电流。(不同于静态电流,静态电流在PDN导通时一直存在)

- 在实际布线时导线数量加倍,使得电路复杂

- 动态功耗较高

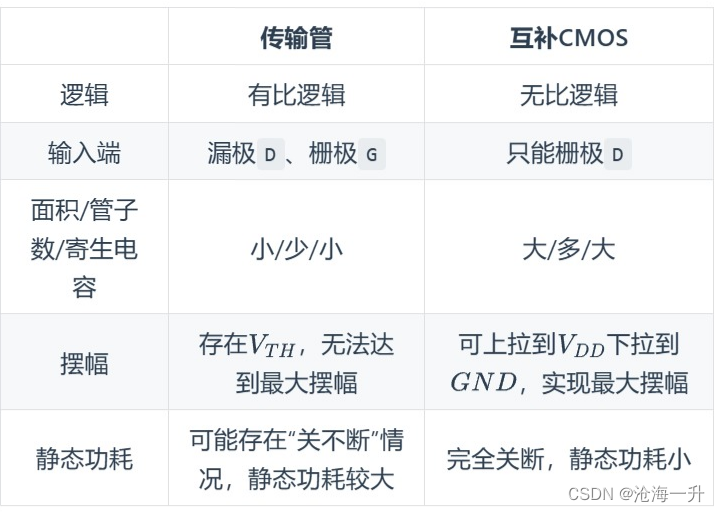

3、传输管逻辑

传输管逻辑主要目的在于减少晶体管数,利用输入驱动栅极和源漏端来减少逻辑需要的晶体管数。

与只允许驱动栅极的CMOS不同。

传输管的缺点在于存在阈值损失。并且由于体效应这种情况更加严重。此外,应该避免传输管驱动另一个栅极,这样会导致阈值损失传递。

1)差分传输管逻辑CPL

高性能设计中通常使用差分传输管逻辑,称为CPL或DPL.

- CPL属于静态门,输出节点通过低阻路径连到VDD或地。

- 互补输入输出

- 具有模块化特点,门单元库设计简单。

缺点在于因为存在VTH,高电平时充电充不到VDD,只能充到VDD-VTH。

2)解决阈值损失和静态功耗

正如上面所说由于传输管在高电平无法充电到VDD,少了一个VT,所以在驱动后级的反相器时反相器会有静态功耗。因此,常用以下方案设计稳定有效的传输管

a、电平恢复器

一种简单的方法是使用一个PMOS连到反馈环路中:

通过上拉的PMOS将高电平充到VDD,消除了后级反相器的静态功耗,传输管和恢复器中也没有静态电流路径。但电平恢复器也有以下缺陷:

- 是有比逻辑,增加了复杂性。在节点从高到低的过程中,传输管试图拉低节点,而电平恢复器却要上拉到高,因此传输管的下拉能力必须大于恢复器的上拉能力。这就要求仔细设计各个管的尺寸。

- 电平恢复器对器件切换速度有影响。增加恢复器增加了内部节点X的电容,减慢了门的速度。

b、多阈值晶体管

使用零阈值的NMOS传输管可以消除大部分阈值损失。所有非传输管都用高阈值器件实现。

同样也存在缺陷:

- 需要对器件的注入准确控制才能达到0阈值,并且由于体效应,难以真的达到全摆幅

- 用零阈值对功耗有不利影响。这是因为即使器件关断,也会有亚阈值电流流过传输管

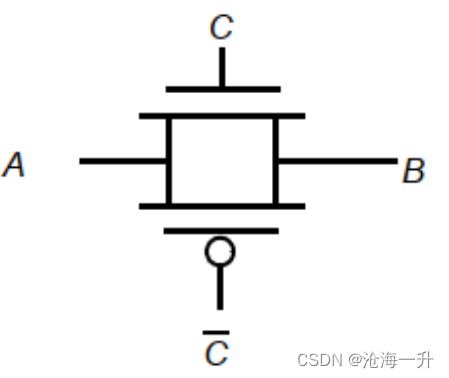

c、传输门逻辑

最广泛采用的是传输门逻辑,利用NMOS和PMOS的互补特性。

两个管子并联,控制信号相反,任何时候两者都导通。通常消耗更少的管子。例如实现下面的逻辑:

采用CMOS逻辑需要8管,而传输门逻辑只需要6管。(不包括反向输入信号的生成):

这种传输门本身没有驱动能力,需要靠前一级的驱动能力,或在这个传输门前后各增加一级反相器,共增加两级反相器,同时保证有驱动能力,和信号极性保持不变。

应用场景有,在常见的MUX多路选择电路中,在DFF和latch中时钟采样信号。在前者MUX多路选择电路中,选择信号是一些低速信号,甚至有可能是寄存器(register)。而在后者DFF和latch中,选择信号就是时钟信号,是高速信号。

非理想选择信号造成的影响,主要是指选择信号变化时,SEL和SELB在切换过程有交叠,存在一个管子本该关断,但是还没有关断,或者存在一个管子本该开启,却还没有开启。在MUX多路选择电路中,正是因为选择信号是一些低速信号,少有切换过程,故影响不大。而在DFF和Latch中,时钟信号不断地翻转,不断有切换过程,当时钟信号有交叠时,是会直接影响输出信号的好坏。

二、动态CMOS逻辑

1、基本介绍

静态CMOS是指稳态时,通过低阻路径连接GND或VDD:

- 互补CMOS:上下网络互补,上拉到VDD,下拉到GND。管子数为2N

- 传输管逻辑:上拉网络用其他代替,有比逻辑,存在VTH。管子数为N+1

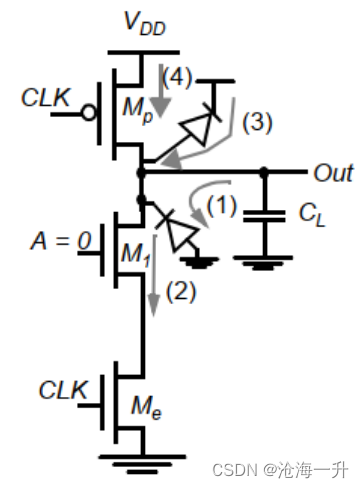

动态CMOS:依靠高阻抗上的电容存储临时的信号,管子数为N+2。

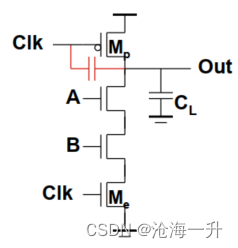

其结构如下:

工作分为两个阶段:

- 预充电:CLK=0,Mp导通,对CL充电。输出节点Out被PMOS管预充电至VDD。此期间NMOS求值管Me关断,所以下拉不工作。求值管消除了预充电期间的任何静态功耗。

- 求值:CLK=1,Me导通,OUT和GND之间存在低阻通路。预充电管Mp关断,输出根据下拉拓扑结构有条件地放电。

特点:

- 全电压摆幅

- 无比逻辑(同互补CMOS,异传输管逻辑)

- 噪声容限低。因为out在预充电阶段已经充电到vdd,即Vds已经满足>Vov,于只要Vin>VTH,管子就会导通。

- 需要预充电和求值的时钟。

- 较快的开关速度。原因如下,

- 相对互补CMOS,缺少了上拉网络的一个门,相对负载是互补CMOS,负载是动态门的CL比较小

- 动态门没有短路电流(同一个时刻,只能一个M导通),由下拉网络提供的所有电流都用于CL电容的放电

- 如果IN=0,则不存在输出延时(预充电完输出即为1);如果IN=1,则需要CL放电

- 晶体管重复利用,减小面积(多输出多米诺)

优点:

- 提高速度

- 减小面积(多输出多米诺;N+2个管子)

- 没有短路功耗

- 没有毛刺(因为一次只能翻转一次,CL放电完只能等效下一次预充电才能回到1)

缺点:

- 动态逻辑的时钟功耗可以很大

- 当增加抗漏电器件时可能会有短路功耗

- 由于周期性的预充和放电,动态逻辑会有较高的开关活动性。

2、存在的问题——信号完整性

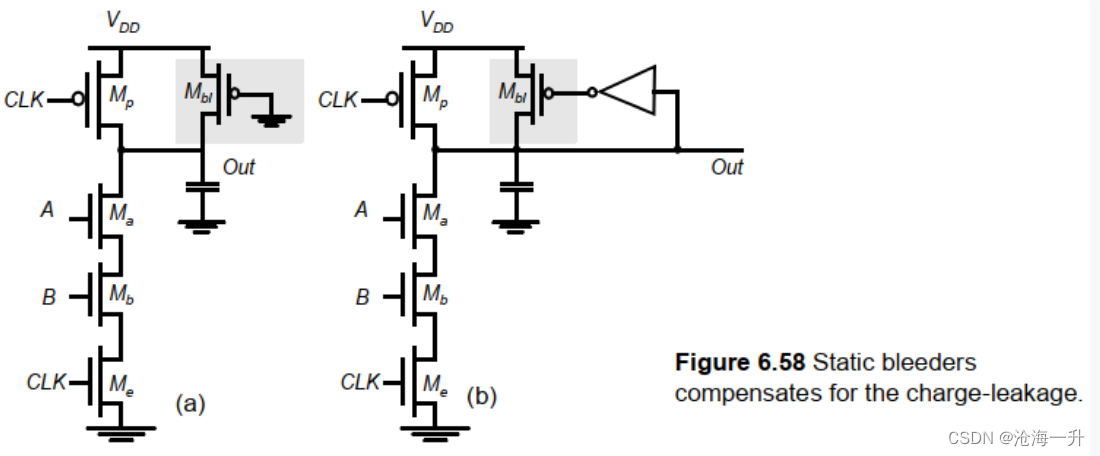

1)电荷泄漏

预充电到高后,电容上将保持高电平,但总是会有泄露电流导致电荷漏掉。

可见存储在CL上的电荷将通过漏电左图的几个漏电渠道漏掉,因此动态电路有一个最低的频率要求,一般为几KHZ。

电荷泄露的解决通常通过增加伪NMOS上拉以及反馈来补偿:

通过反馈来控制上拉管可以降低静态功耗。通常泄露器的尺寸比较小(电阻比较大),以保证下拉网络可以下拉。

2)电荷分享

下图展示了电荷分享。在求值期间,假设B=0,A置高后Ma导通,CL上的电容会在CL和Ca之间重新分配,导致输出电平的降低。

解决方案为使用上拉管对关键的内部节点预充电:

代价是面积和功耗。

3)电路耦合

输出节点较高的阻抗使得电路对串扰很敏感。使得Vout略有下降。

4)时钟馈通

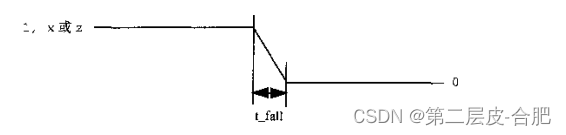

时钟输入和动态节点输出之间的耦合电容引起。耦合电容由预充器件的栅漏电容组成。其次,快速上升和下降的时钟边沿会耦合到信号节点上。

时钟反转过快,则当CLK0→1时,动态节点输出>Vdd;则当CLK 1→0时,动态节点输出<0 。时钟馈通危险在于可能使正常情况下反偏二极管变为正向偏置,导致出错。

3、动态门的串联

动态门的串联会遇到延时的问题,例如下面的电路:

当Out1开始放电时,此时Out2应该维持不变,但是out1放电需要时间,导致out2也开始放电,产生错误。 但是如果每一级动态门在预充电后输出都为0,则不会由这样的问题。这也是动态门串联的条件。

1)多米诺逻辑

动态逻辑后加一个反相器,再级联其他多米诺逻辑。反相器可以保证动态逻辑再预充电后输出为0,避免1->0的翻转。目的就是保证预充电时,输入均为0;求值时,输入只做0→1的翻转。

初始状态均为0,求值的时候根据前一级输出确定下一级输入,从而求下一级输出。

特点:

- 求值层层传播,如多米诺骨牌

- 求值阶段的时间取决于逻辑深度(因为求值时候的特性,见上)

- 只能实现非反向逻辑

- 无比逻辑

- 节点需要在预充电充完电,求值的过程中,输入需要特别稳定。

- 速度非常快(因为当上一级的输入都是0时,下一级相当于无延迟传播)

- 输入电容小(和互补CMOS比,只有一个管子)

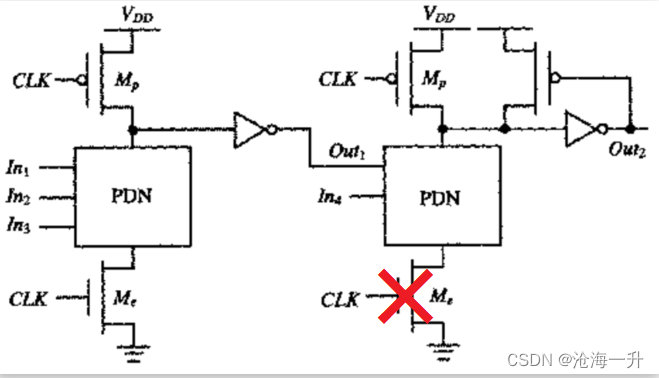

2)去掉下拉时钟网络

如下图所示

优点:

- 只需要第一级的下拉时钟负载,后面的不用。减少时钟负载。

- 速度和性能可以得到大大提升

缺点:

- 去掉下拉时钟网络,需要满足该动态门CLK=0时,该动态门输入均为0,否则可能导致短路

- 为了达到上文的目标,需要精确把控时钟。

3)多米诺逻辑的性能优化

-

调整反相器的晶体管尺寸

分析可知,

预充电过程中,主要经过两个门的延迟:

- Vdd通过上拉时钟PMOS管对CL进行充电

- 本级动态门输出逻辑1经过反相器(INV的PMOS管)输出逻辑0,作为下一级输入

求值过程中,如果存在该动态门输入存在从0→1跳变,主要经过两部分延迟:

- 本级动态门下拉网络对CL进行放电

- 本级动态门输出逻辑0经过反相器(INV的PMOS管)输出输出逻辑1,作为下一级的求值输入

可根据情况进行反相器尺寸的调整(一般为了减低求值时间,会增大INV的PMOS尺寸

-

面积优化

-

采用多输出多米诺逻辑,见下文。

多输出多米诺逻辑中,动态逻辑门可以实现多种逻辑,可以重复利用一些晶体管,使得晶体管数目减小。

-

或者使用组合多米诺逻辑,见下文。

组合多米诺逻辑,并不需要在每个动态门之后加反相器,而是借助一个复合互补CMOS门将多个动态门组合起来。

-

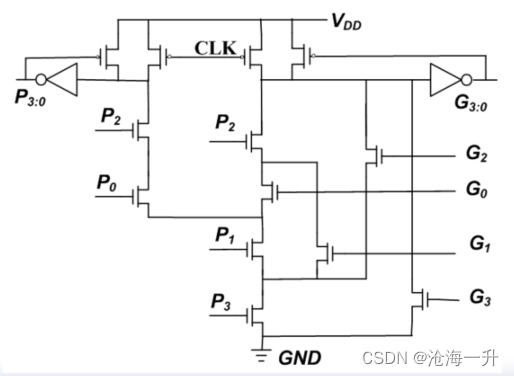

4)多输出多米诺

多输出多米诺可以重复利用一些晶体管,一个复合逻辑门里面可以实现多种逻辑,减小了晶体管数量,大大减小面积。

5)组合逻辑多米诺

组合多米诺逻辑,并不需要在每个动态门之后加反相器,而是借助一个复合互补CMOS门将多个动态门组合起来。

如上图,动态门组成逻辑:;经过静态互补CMOS门,组成逻辑

,注意,Y2结果并不需要经过反相器。