目标

- 完成以cpu的设计,三级流水线结构。取指(if), 译码(id), 执行(ex)

- cpu中断系统的设计

- 以cpu为核心的SOC设计,完成rom,ram,time的外设的设计

- 用uvm对cpu进行验证(system verilog)

理论

数字逻辑电路

数字信号:用二进制表示的信号,即信号用0, 1 来表示。

数字编码

原码,反码,补码在正数的时候不变。在表示负数时如:-1

原码: 符号位为1,其他位置: 001 —> 1001

反码: 符号位不变,其他位置取反: 110 —> 1110

补码: 在反码的基础上 + 1 —> 1111

Note: 计算机中以补码的方式存储

常见的编码: 2421BCD、5421BCD、8421BCD码

2. CPU基本模块

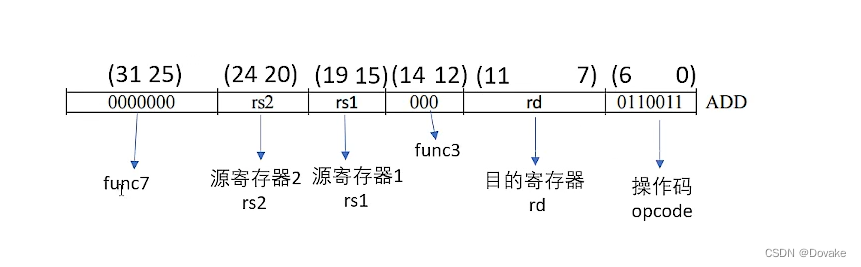

2.1 32 位risc-v 处理器指令格式

- 0~6 : 操作码 opcode

- 7~11: 目的寄存器 rd

- 12~14: func3

- 15~19: rst1 源寄存器1

- 20~24:rst2 源寄存器2

- 25~31: func7

汇编指令示例:

ADD rd, rs2, rs1

rst1寄存器的值 + rst2寄存器的值 ——> rd 寄存器的值