文章目录

- 1.1 突发传输简介

- 1.1.1 AXI4 突发传输控制信号

- 1.1.1.1 AxLEN 突发传输长度

- 1.1.1.2 AxSIZE 突发传输宽度

- 1.1.1.3 AxBURST 突发传输类型

- 1.1.2 AXI 传输实例

1.1 突发传输简介

在地址总线上进行一次地址传输后,进行多次数据传输( data transfer),第一次地址传输中的地址作为起始地址,根据突发传输类型的不同,后续数据的存储地址在起始地址的基础上递增(INCR 模式);或者首先递增,到达上限地址后回到起始地址,继续递增(WRAP 模式);又或者后续数据都将不断写入起始地址,刷新起始地址上的数据(FIXED 模式)。

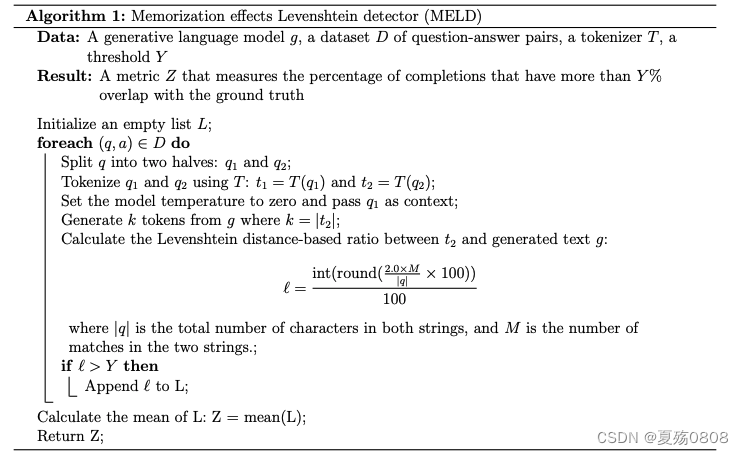

1.1.1 AXI4 突发传输控制信号

突发传输的控制信息在地址通道上,随着第一次地址传输时写入,控制信息包括:

1.1.1.1 AxLEN 突发传输长度

Burst length: ARLEN[7:0]和AWLEN[7:0] 突发传输长度是指在一次突发传输中所进行的传输(data transfer)次数,在传输完初始地址后,进行的数据传输次数就是突发传输长度。在 AXI4 中:

- INCR 类型最大支持长度为 256;

- 其他类型(见1.1.1.3节)最大长度为 16。

突发长度最少为 1,不然也就没有传输发生了。协议中的 burst length 从零开始,实际的长度值为长度字段加 1;

- 一个 burst 内部是不可以被打断的, 所以 data valid一旦高起来就要把一个burst 传完再拉低;

- slave 的 ready 信号可以中断,但是最终还是要高起来传完一个burst;

- 对于 master 来说,一旦开始传数,一个 burst 之间的 valid 应该是不会低的。

1.1.1.2 AxSIZE 突发传输宽度

Burst size: 指的是一个 data transfer 里面有多少 bytes. ARSIZE[2:0]和AWSIZE[2:0] 就是用于设置这个属性的。

为什么只有 3bit 呢?

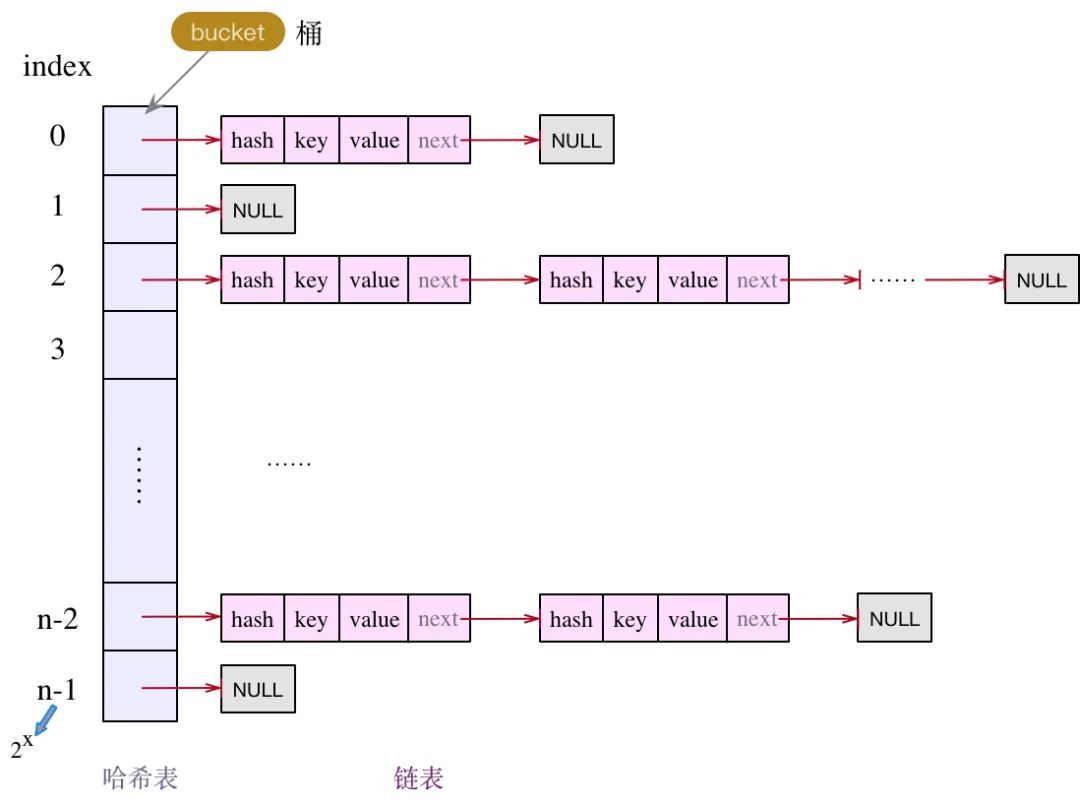

如上图所示:只有 8 种情况。一般来说, 总线位宽和 burst size一致的, 比如总线 64bit, 那么 burst size 是8 byte。

1.1.1.3 AxBURST 突发传输类型

Burst type: 有三种:

- FIXED: 类型适合对某个固定地址进行数据更新,比如向一个 almost full 的 fifo 更新数据;

- INCR: 类型最为常用,后续的数据的存储地址在初始地址的基础上,以突发传输宽度进行递增,适合对于 RAM 等 mapped memory 存储介质进行读写操作;

- WRAP: 模式比较特殊,除了初始地址外,还有最高地址的界限。在最大地址以下,WRAP 与 INCR 类型完全相同,地址递增,但达到最高地址后,地址直接回到起始地址,再进行递增,就这样循环往复。数据手册上表示,WRAP 适合对 cache 的访问。

其他信号包括和内存原子操作有关的 AxLOCK,AxCACHE,AxPROT 以及用于用户自定义的 AxUSER 信号,

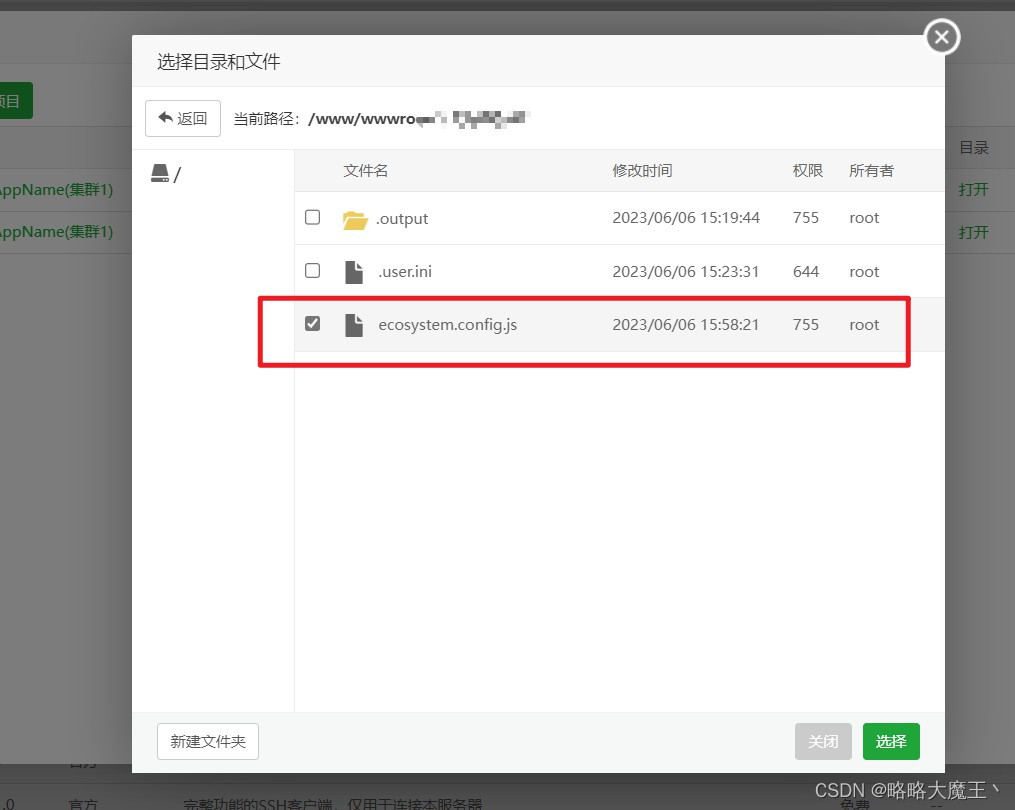

1.1.2 AXI 传输实例

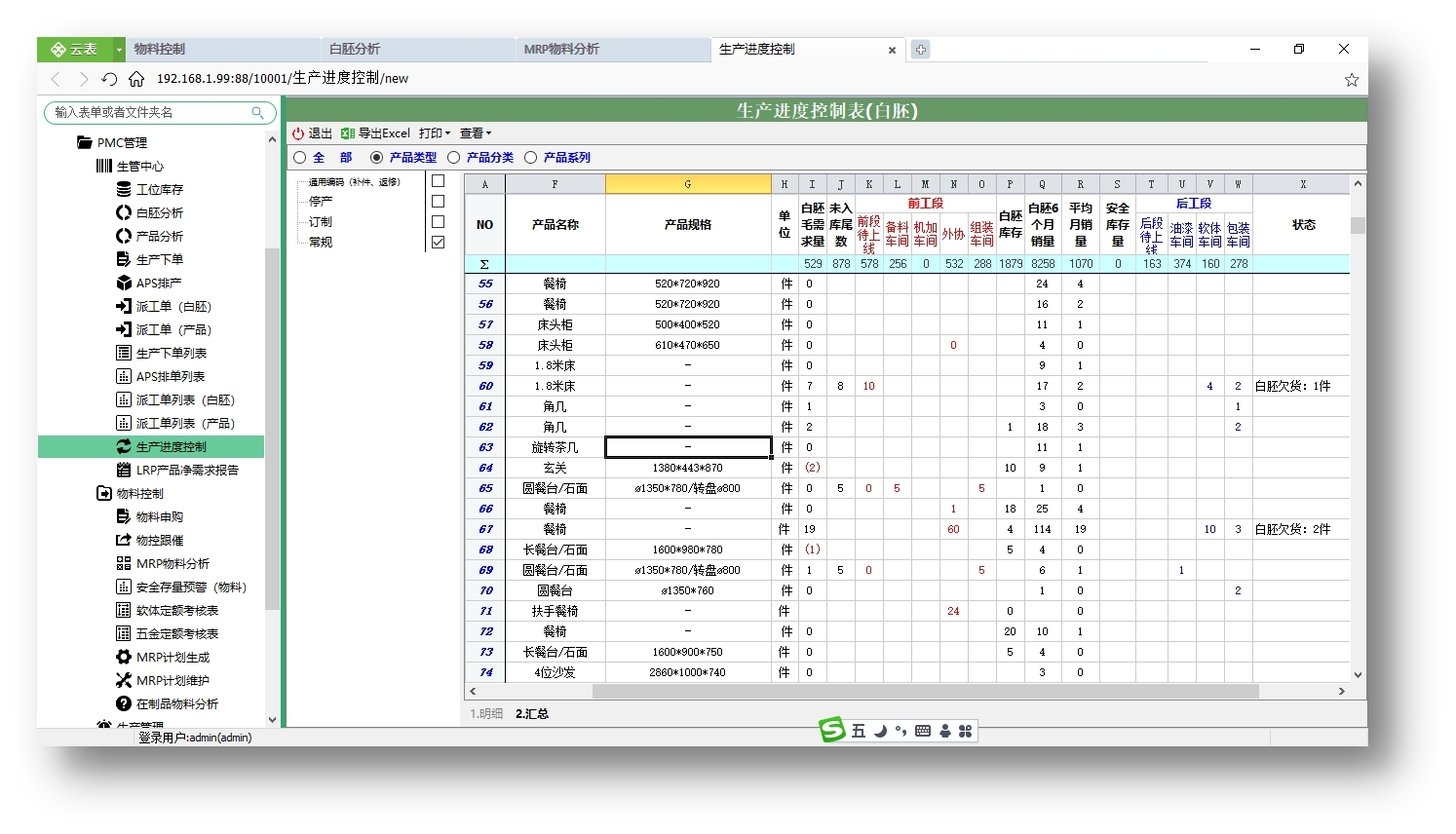

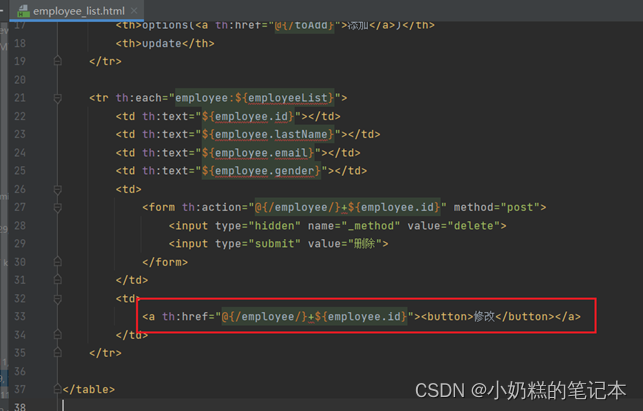

接下来举一个突发写操作讲解 AXI4 突发传输机制,AXI数据总线宽度为 128 bits

上图为主机从0x0地址开始写数据,每次写 64bytes,可以看到地址信号 awaddr_m[39:0] 变化为 0x0->0x40->0x80->0xc0...,图中AXI写数据通道为128bit,见 wdata_m[127:0], 通过将图片放大来看,可以看到 1 burst 中进行了4 次 data transfer(位宽为128bits), 所以正好 64bytes x 8bits = 128bits x 4。

从上图中同时可以看到 :

awsize_m[2:0]的值为0x4(0b100),根据1.1.1.2 节内容可以看到是每一次 data transfer 为16bytes(128bits),正好匹配上axi写数据通道位宽(128bits);awlen_m[7:0]的值为0x3, 根据 1.1.1.1 节的计算公式可知 该burst 传输的次数为0x3 + 1 = 0x4,正好匹配上图中1 个 burst 中包含的的 4 次 data transfer;awburst[1:0]的值为0x1, 根据1.1.1.3节的内容知道 burst 类型为 INCR;- 在

awvalid_m为高时地址有效; - 在

wavlid_m为高时数据有效。