普通的SR锁存器没有任何抗干扰能力

我们要加控制信号,来抵抗干扰

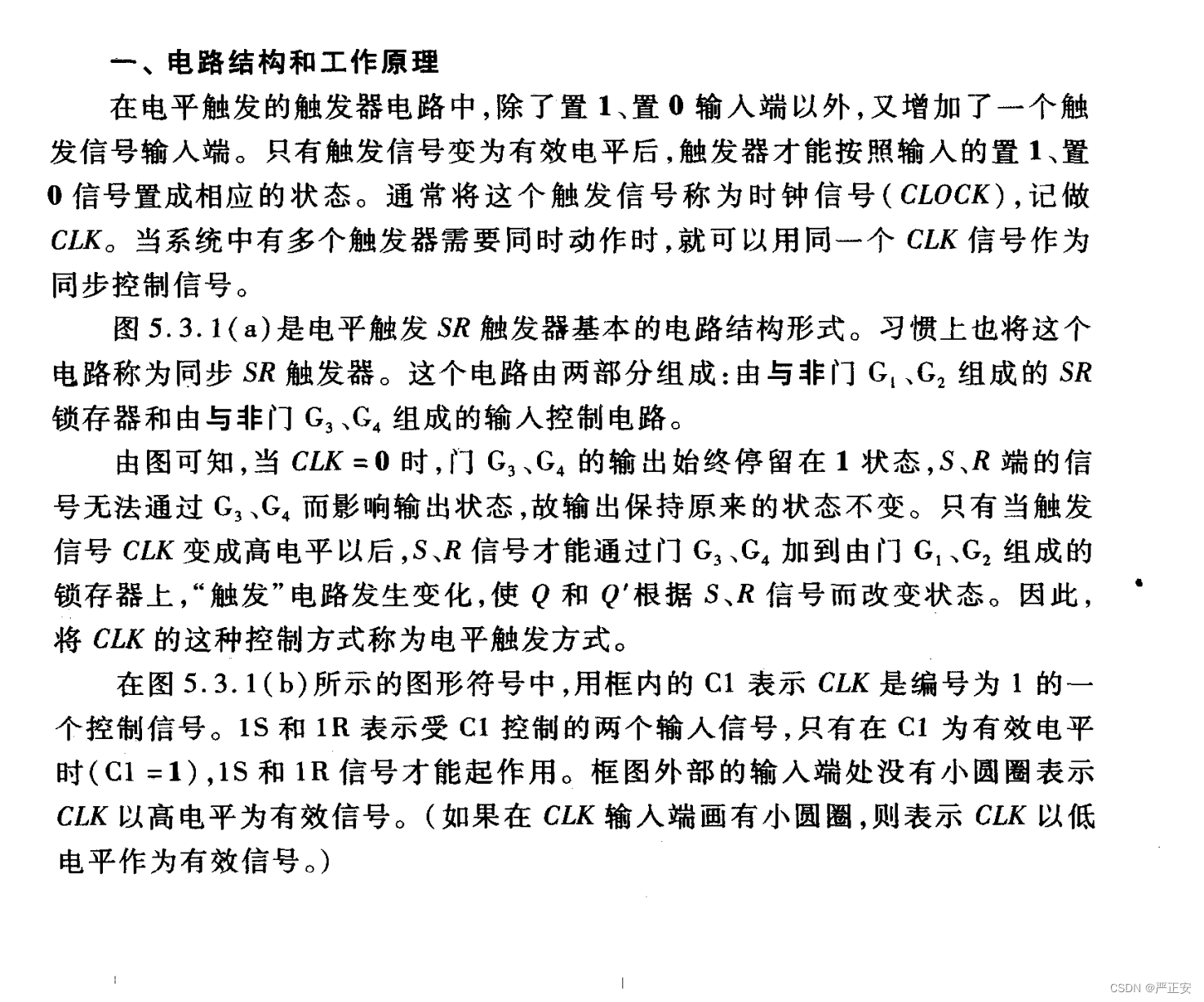

比如说我们不把信号直接加在门上,我们可以再加一级门电路,让这个输出和输入不在同一个门上,我们希望加入一个控制信号,来控制电路工作的时刻

对电路结构做这样的调整,我们认为有问题的地方,就可以来进行改进,这种结构称为电平触发的触发器

在控制信号的电平控制下,分析输入输出关系

我们简单来说一下时钟信号

CLK 我们称之为时钟信号(Clock 信号),我们有时也可以称之为时钟脉冲信号

时钟脉冲信号缩写为CP (Clock Pulse)

这个信号是一个周期性的方波信号

这个信号对于我们电路的工作来说非常重要

时序电路的时序靠时钟信号来控制,时序电路单单靠时钟信号就可以让他工作

清楚的看到,由高低电平构成

我们不单会考虑01,我们还会考虑触发点

从0到1,我们称之为上升沿,正边沿

从1到0,我们称之为下降沿,负边沿

每一种电路结构,时钟信号对他的控制是不一样的

我们来分析

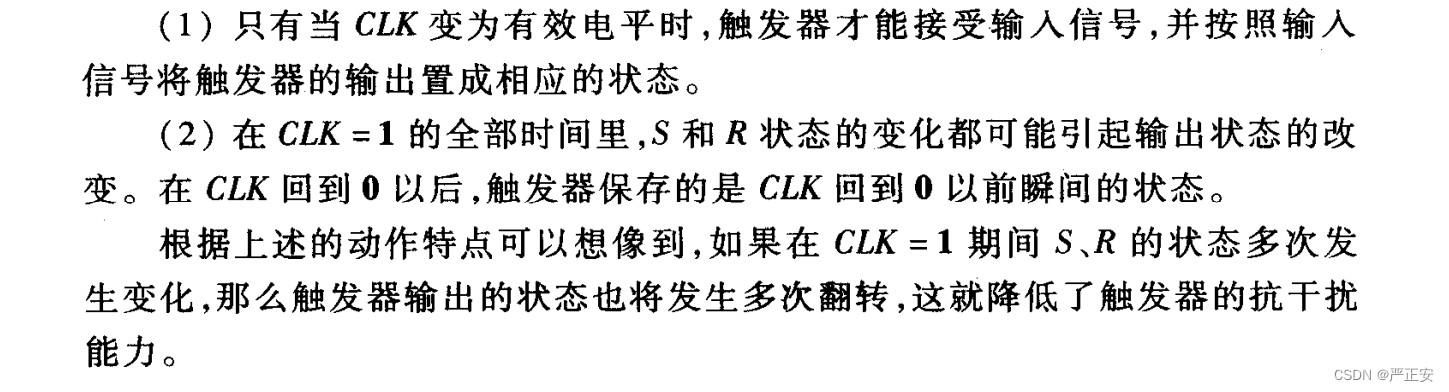

同步SR触发器的工作原理

时钟信号的状态作为前提条件

分为两种情况

1.时钟信号等于0期间

对于与非门来说,处在保持不变状态

2.时钟信号等于1期间,SR的锁存器,时钟信号是控制信号,有SR两个输入端

不定的含义有两种: 1.突然变成低电平 2.时钟信号突然变成低电平,两个信号变化均能产生不定状态

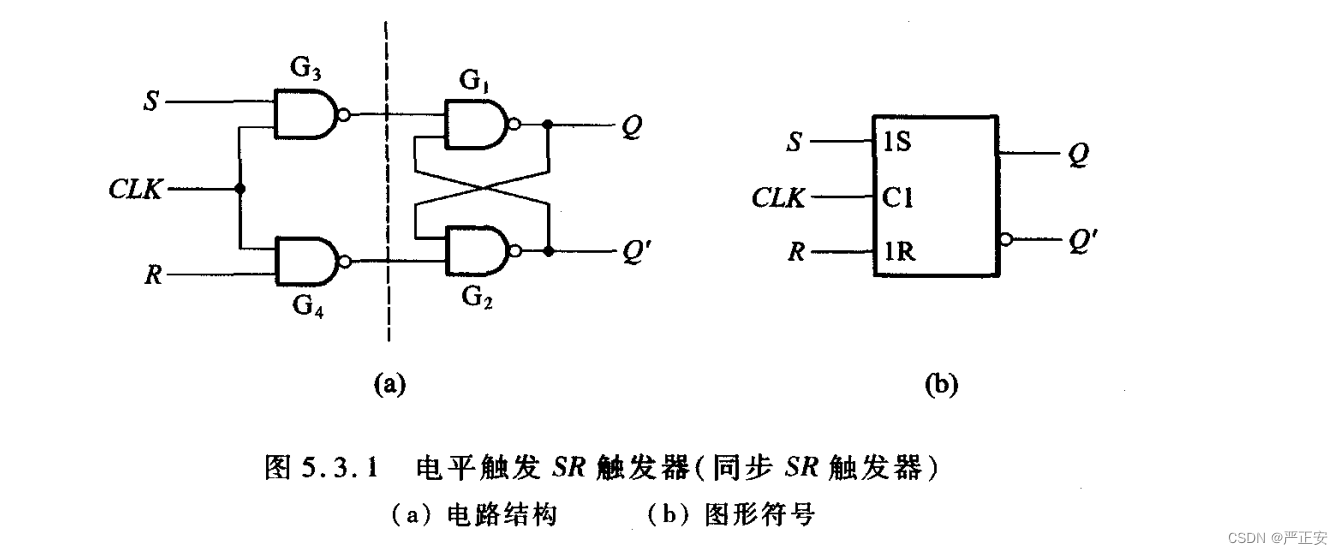

电路的工作我们需要设置初始状态,所以我们往往做成集成电路的时候,我们要考虑这个实际当中的应用,我们会在输入端上增加两个控制端

表明这里加了直接的置1端,可以方便的设置初始状态,以后我们再用触发器的时候用符号来表示逻辑功能

总结

现在触发器里面还有不定状态的存在,如果要出现这样的问题,电路工作还是要受到影响

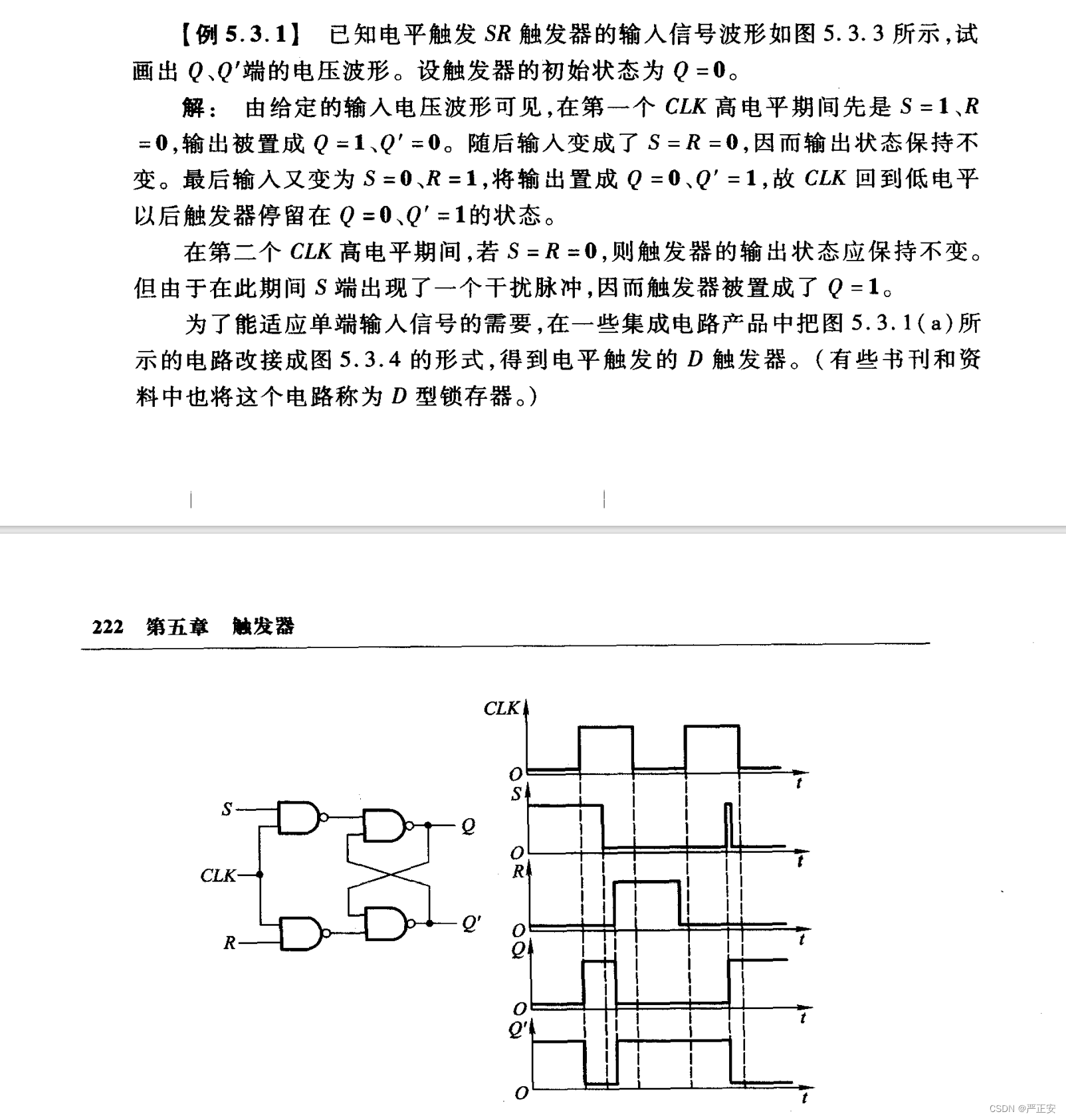

电平触发的D触发器(D锁存器)

![[附源码]计算机毕业设计网上鲜花购物系统Springboot程序](https://img-blog.csdnimg.cn/daa309c783fe45439d301c5cefa1c0ee.png)

![[附源码]计算机毕业设计基于SpringBoot的党务管理系统](https://img-blog.csdnimg.cn/ecb6f2d98eb74baf80dc334ede819a74.png)