目录

前言

重点一览

指令集系统结构(ISA)的分类

分类依据

存储结构

区别

图示

通用寄存器系统结构分类

存储器寻址

概述

寻址方式

MIPS寻址模式

小结

操作数类型 指令操作 与指令编码

常用操作数类型

常用指令系统的操作

常用指令系统编码方式

MIPS系统结构

概述

MIPS寄存器

MIPS的数据类型

MIPS数据传输的寻址方式

MIPS的指令格式

MIPS操作

了解:谬误与易犯的错误

本章小结

前言

本复习笔记基于叶老师的课堂PPT,供自己期末复习与学弟学妹参考用。

重点一览

指令集系统结构(ISA)的分类

分类依据

处理器内部数据的存储结构

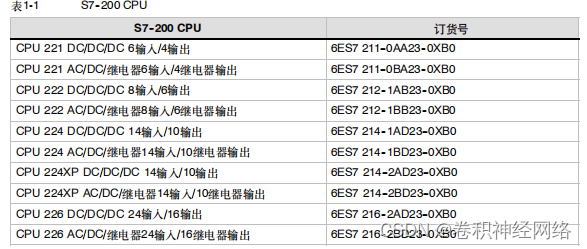

存储结构

堆栈、累加器、通用寄存器

区别

- 堆栈系统结构中操作数隐含的位于栈顶

- 累加器系统结构中的一个隐含操作数就是累加器

- 通用寄存器结构系统中只能明确的指定操作数,不是寄存器就是存储器地址

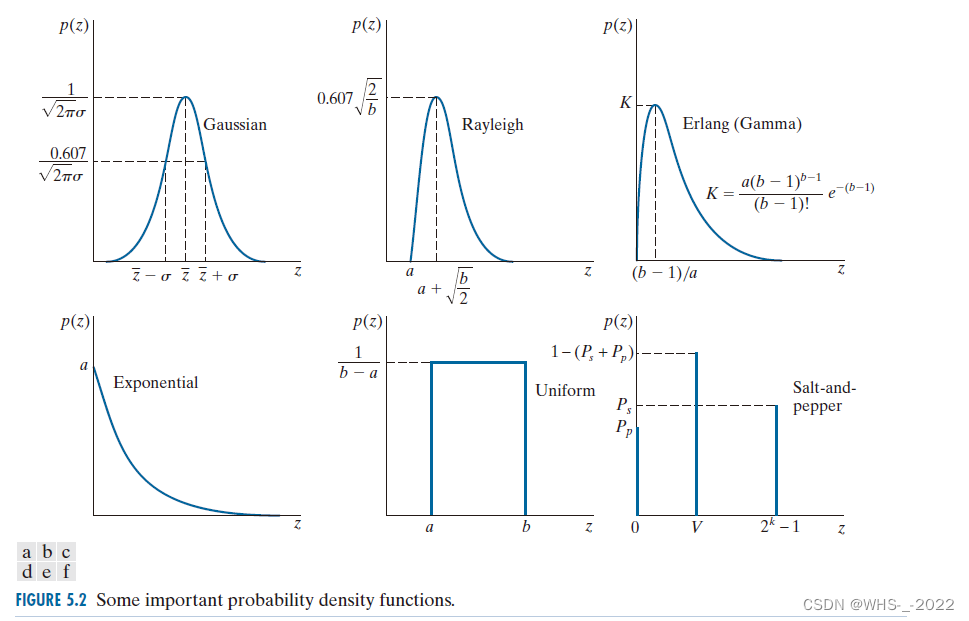

图示

- (a)中,栈顶寄存器(TOS)指向堆栈顶部的输入操作数。第一个操作数被从堆栈中删除,运算结果存放在第二个操作数的位置,同时栈顶寄存器指向运算结果。 所有的操作数都是寄存器,只能通过push或pop指令传输到存储器中

- (b)中, 累加器既是隐含的输入操作数也是运算结果。

- (c)中,一个操作数在寄存器中, 另一个在存储器中, 运算结果存放在寄存器中。

- (d)中, 所有的操作数都是寄存器,与堆栈结构(a)类似, 也只能通过一些单独的指令(load或store)传输到存储器中,属于MIPS结构

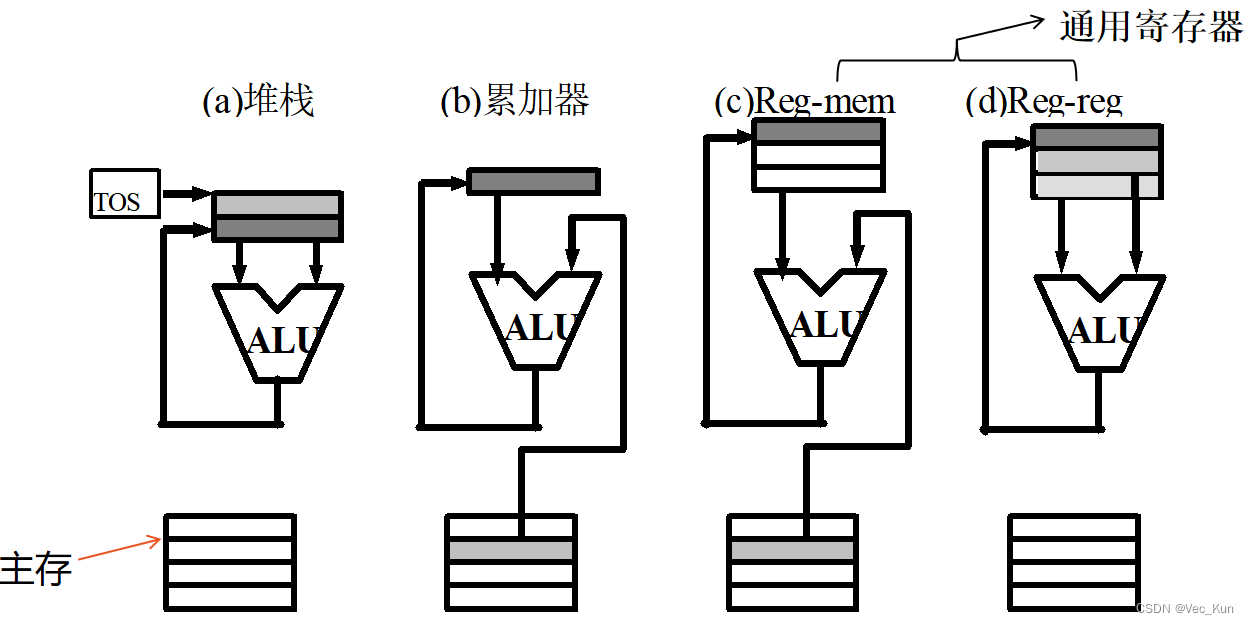

通用寄存器系统结构分类

(1)register-memory系统结构,一般指令都可以访问存储器。如上图C,Reg-Mem结构

(2)register-register或 load-store系统结构,只能通过load和store指令来访问内存 。如上图D,Reg-Reg结构

(3)教材提到的纯 memory-memory系统结构,现实中不存在的结构,把所有的数据都保存在存储器中。

存储器寻址

概述

我们讨论的所有指令系统都是字节寻址的,都提供了字节(8位)、半字(16位)和字(32位)寻址,大多数的计算机还提供了双字(64位)寻址。

Intel的一个字是2个字节;MIPS的一个字是4个字节

将数据从存储器拷贝到寄存器的指令,叫取数指令(lw 指令:load word);将数据从寄存器拷贝到存储器的指令,叫存数指令(sw 指令:store word)

小端模式:低地址存低字节,如04030201H;大端模式:低地址存高字节,如01020304H

MIPS的一个字是4个字节。在MIPS中,字的起始地址必须是4的倍数,称为对齐限制。 这样可以简化硬件实现的复杂性,提高对齐访问的程序运行速度

寻址方式

寻址方式:寻找操作数或操作数地址的方式

| 寻址方式 | 指令举例 | 含义 | 何时使用 |

| 寄存器寻址 | Add R4,R3 | Regs[R4]←Regs[R4]+Regs[R3] | 数值在寄存器中 |

| 立即数寻址 | Add R4,#3 | Regs[R4]←Regs[R4]+3 | 数值是常量 |

| 位移量寻址 | Add R4,100(R1) | Regs[R4]←Regs[R4] +Mem[100+Regs[R1]] | 存取局部变量(+模拟寄存器 间接、直接寻址) |

| 寄存器间接寻址 | Add R4,(R1) | Regs[R4]←Regs[R4]+Mem[Regs[R1]] | 使用指针或者计算出的地址 进行寻址 |

| 间接寻址 | Add R3,[R1+R2] | Regs[R3]←Regs[R3] +Mem[Regs[R1]+[Regs[R2]] | 有时用在数组寻址中 |

| 索引寻址 | Add R1,(1001) | Regs[R1]←Regs[R1] +Mem[1001] | R1是数组的基址,R2是索引 值用来存取静态数据;地址 常量可能需要很大 |

| 存储器间接寻址 | Add R1,@(R3) | Regs[R1]←Regs[R1] +Mem[Mem[Regs[R3]]] | 如果R3是指针p的地址,那么 就得到*p |

| 自动递增寻址 | Add R1,(R2)+ | Regs[R1]←Regs[R1]+Mem[Regs[R2]] Regs[R2]←Regs[R2]+d | 用在循环中递增变量,R2是 数组的起始地址,每次增加d |

| 自动递减寻址 | Add R1,-(R2) | Regs[R2]←Regs[R2]-d Regs[R1]←Regs[R1]+Mem[Regs[R2]] | 和自动递增类似,自动递增/ 递减用来实现类似堆栈的 push/pop功能 |

| 比例寻址 | Add R1,100(R2)[R3] | Regs[R1]←Regs[R1] +Mem[100+Regs[R2]+Regs[R3]*d] | 用来对数组寻址。一些计算 机可以用任意的索引(间接) 寻址方式 |

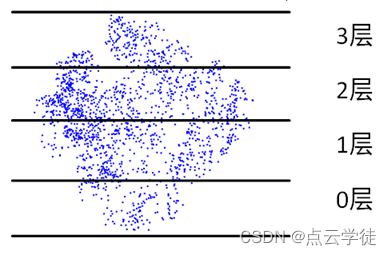

MIPS寻址模式

立即数寻址:操作数是指令中的常数

![]()

寄存器寻址:操作数是寄存器

基址寻址:操作数在内存中,地址是指令中基址寄存器和常数的和

PC相对寻址:操作数在内存中,地址是PC和指令中常数的和

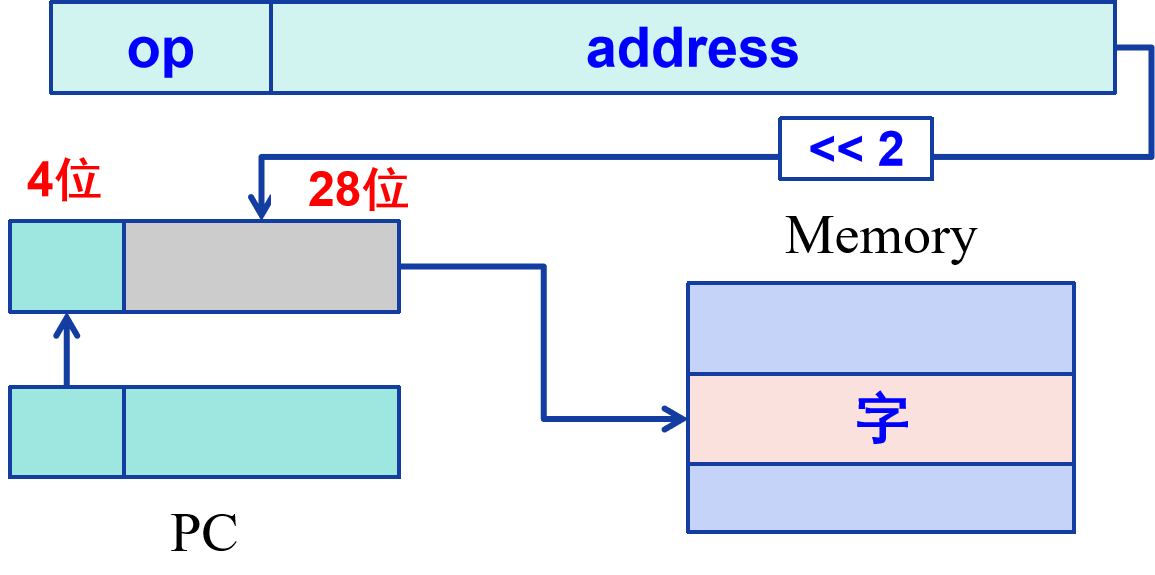

伪直接寻址:跳转地址是指令中26位字段和PC高位相连而成

小结

一般ISA支持的基本寻址方式:立即数寻址、位移量寻址、寄存器间址。

立即数为8~16位;位移量为13~16位。

操作数类型 指令操作 与指令编码

常用操作数类型

常见的操作数类型:

常用指令系统的操作

大多数指令集系统结构支持的操作:

| 操作类型 | 举例 |

| 算术和逻辑运算 | 定点算术和逻辑操作:加、减、与、或、乘、除 |

| 数据传输 | Load-store指令(在REG-MEN结构计算机上是传送指令) |

| 控制 | 条件转移、跳转、过程调用和返回、陷阱 |

| 系统 | 操作系统调用、虚拟存储器管理指令 |

| 浮点 | 浮点操作:加、减、乘、除、比较 |

| 十进制 | 十进制加、十进制乘、十进制到字符的转换 |

| 字符串 | 字符串传送、字符串比较、字符串匹配 |

| 图像 | 像素、顶点操作、压缩/解压缩操作 |

使用最多的是一些简单指令。一般所有的计算机都提供前三类指令。指令集对后四类指令的支持数量可能为0,也可能包含大量特殊指令。

控制流指令分类:条件转移,跳转,过程调用,过程返回

MIPS控制流指令:

| 指令举例 | 指令名称 | 含义 |

| J name | 跳转 | PC0..27←name |

| JAL name | 跳转并链接 | Regs[R31]←PC+4;PC0..27←name; ((PC+4)-227)≤name<((PC+4)+227) |

| JALR R2 | 寄存器跳转并链接 | Regs[R31]←PC+4;PC←Regs[R2] |

| JR R3 | 寄存器跳转 | PC←Regs[R3]; |

| BEQZ R1,name | 等于零时分支 | If(Regs[R1]==0) PC←name; ((PC+4)-217)≤name<((PC+4)+217) |

| BNE R3,R4,name | 不等于时分支 | If(Regs[R3]!=(Regs[R4]) PC←name; ((PC+4)-217)≤name<((PC+4)+217) |

| MOVZ R1,R2,R3 | 等于零时传送 | If(Regs[R3]==0) Regs[R1]←Regs[R2] |

分支的目标地址=16位带符号位移量左移2位 +(PC+4)

控制流指令的寻址方式

PC相对寻址,即使用基于程序计数器(PC)的位移量来指定目标地址。

* PC相对寻址指令的优点:

目标与当前指令离得不远;使用相对偏移地址可以缩减指令长度。

使用相对寻址的程序可以载入到主存任何位置(位置无关),对执行时才链接的程序可减少工作量

寄存器间接跳转,编译时不知道目标位置,为了实现返回和间接跳转,需要使用寄存器间接跳转:给出包含目标地址的寄存器名称。通常在寄存器间接跳转之前,才把地址从存储器载入到寄存器中

常用指令系统编码方式

指令编码包括:操作、寄存器地址、寻址方式编码;决定了处理器实现和编译后程序大小

对指令编码,需要在以下因素之间找到一个最佳平衡点:

- 尽可能多的寄存器和寻址方式。

- 寄存器字段、寻址方式字段尽量少,以缩短指令长度。

- 指令长度易于流水线处理。

三种常见编码方式

- 变长编码:允许所有的操作使用所有的寻址方式,适合寻址方式和操作比较多的情形。最少的位数表示程序,译码复杂,不适合流水线。

- 定长编码:把操作和寻址方式组合在操作码里,通常所有的指令长度都相同。这种方式适合于寻址方式和操作比较少的情况。译码简单,适合流水线,代码量大。

- 混合编码:减少过多的指令,以减轻多种结构的指令带来的工作负担,但仍提供多种指令长度以减少代码长度。

总之:*关注代码量大小,选择变长编码;*关注程序的执行性能,选择定长编码;*折中可以选择混合编码。

MIPS系统结构

概述

- 一种简单64位load-store系统结构

- 固定长度指令编码,译码简单,有利于实现高效率流水线。

- 使编译器更容易产生高效的目标代码。

MIPS寄存器

- 32个64位通用寄存器(GPR),名称为R0,R1,…,R31,也称为寄存器。

- 32个浮点寄存器(FPR),名称为F0,F1, …,F31,即可以作为32个32位单精度寄存器来使用,也可以作为32个64位双精度寄存器来使用。

- R0的值永远是0

MIPS的数据类型

- 定点数据类型有8位字节、16位半字、32位字和64位双字。

- 浮点数有32位单精度和64位双精度浮点数。

- 操作面向64位定点以及32位或64位浮点数的。字节、半字或者字在调入64位寄存器中时,用零或者符号来填充64位寄存器的剩余部分。

MIPS数据传输的寻址方式

- 16位立即数 16位位移量方式(基址寻址),即操作数地址是一个存放在寄存器中的基地址与相对该基址的一个16位移量相加获得。

- 位移量为0---寄存器间接寻址;R0作为基址寄存器---16位绝对寻址

- MIPS存储器是用64位地址字节寻址的。

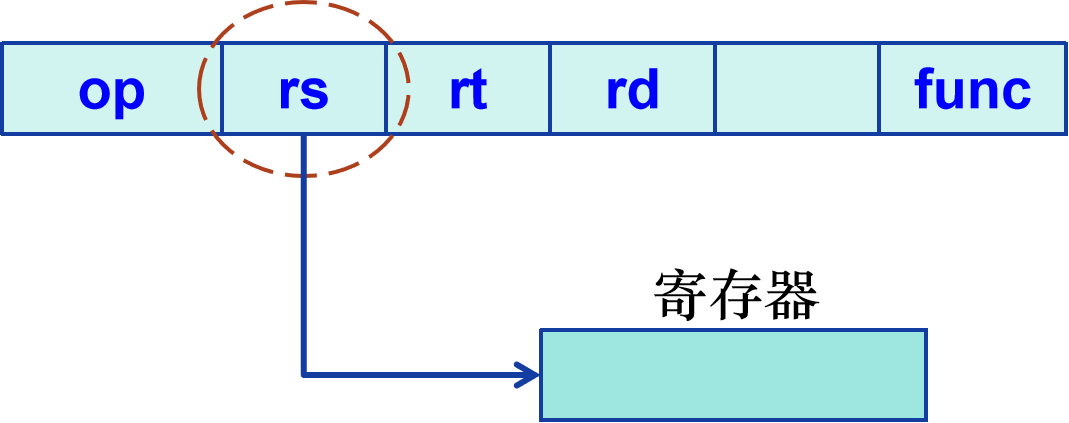

MIPS的指令格式

- 指令长度:32位,其中6位是基本操作码。可以使机器更容易进行流水线操作和译码。

- 两种存储器寻址方式:编码到操作码中。

MIPS操作

- 大致分为四类:载入和存储、ALU操作、分支与跳转、浮点操作。

- 所有通用寄存器与浮点数寄存器都可以被载入或存储,唯一的例外是载入R0无效

载入与存储操作举例

| 指令举例 | 指令名称 | 含义 |

| LD R1,30(R2) | 载入双字 | Regs[R1]←64Mem[30+Regs[R2]] |

| LD R1,1000(R0) | 载入双字 | Regs[R1]←64Mem[1000+0] |

| LW R1,60(R2) | 载入字 | Regs[R1]←64(Mem[60+Regs[R2]]0)32##Mem[60+Regs[R2]] |

| LB R1,40(R3) | 载入字节 | Regs[R1]←64(Mem[40+Regs[R3]]0)56##Mem[40+Regs[R3]] |

| LBU R1,40(R3) | 载入无符号字节 | Regs[R1]←64056##Mem[40+Regs[R3]] |

| LH R1,40(R3) | 载入半字 | Regs[R1]←64(Mem[40+Regs[R3]]0)48## Mem[40+Regs[R3]]##Mem[41+Regs[R3]] |

| L.S F0,50(R3) | 载入单精度浮点数 | Regs[F0]←64Mem[50+Regs[R3]]##032 |

| L.D F0,50(R2) | 载入双精度浮点数 | Regs[F0]←64Mem[50+Regs[R2]] |

| SD R3,500(R4) | 存储双字 | Mem[500+Regs[R4]]←64Regs[R3] |

| SW R3,500(R4) | 存储字 | Mem[500+Regs[R3]]←32Regs[R3]32..63 |

| S.S F0,40(R3) | 存储单精度浮点数 | Mem[40+Regs[R3]]←32Regs[F0]0..31 |

| S.D F0,40(R2) | 存储双精度浮点数 | Mem[40+Regs[R3]]←64Regs[F0] |

| SH R3,502(R2) | 存储半字 | Mem[502+Regs[R2]]←16Regs[R31]48..63 |

| SB R2,41(R3) | 存储字节 | Mem[41+Regs[R3]]←32Regs[F0]56..63 |

注意

- 当被传送的数据长度不确切时,在符号←上附加一个下标,表示传送n位。

- 下标用于标识字段中特定的位。位从以0开始的最高位开始标注。

- 变量Mem用来表示主存储器(内存),按字节编址,可以传输任意字节的数据。

- 上标用来表示对字段进行复制。

- 符号##用来链接两个字段并且可以出现在数据传送的任何一边。

ALU指令举例

| 指令举例 | 指令名称 | 含义 |

| DADDU R1,R2,R3 | 无符号加 | Regs[R1]←Regs[R2]+Regs[R3] |

| DADDIU R1,R2,#3 | 加无符号立即数 | Regs[R1]←Regs[R2]+3 |

| LUI R1,#42 | 载入立即数到高位 | Regs[R1]←032##42##016 |

| DSLL R1,R2,#5 | 逻辑左移立即数 | Regs[R1]←Regs[R2]<<5 |

| DSLT R1,R2,R3 | 置小于 | If(Regs[R2]<Regs[R3]) Regs[R1]←1 else Regs[R1]←0 |

分支与跳转(控制流)指令举例

| 指令举例 | 指令名称 | 含义 |

| J name | 跳转 | PC0..27←name |

| JAL name | 跳转并链接 | Regs[R31]←PC+4;PC0..27←name; ((PC+4)-227)≤name<((PC+4)+227) |

| JALR R2 | 寄存器跳转并链接 | Regs[R31]←PC+4;PC←Regs[R2] |

| JR R3 | 寄存器跳转 | PC←Regs[R3]; |

| BEQZ R1,name | 等于零时分支 | If(Regs[R1]==0) PC←name; ((PC+4)-217)≤name<((PC+4)+217) |

| BNE R3,R4,name | 不等于时分支 | If(Regs[R3]!=(Regs[R4]) PC←name; ((PC+4)-217)≤name<((PC+4)+217) |

| MOVZ R1,R2,R3 | 等于零时传送 | If(Regs[R3]==0) Regs[R1]←Regs[R2] |

分支的目标地址=16位带符号位移量左移2位 +(PC+4) MIPS指令是32位,4个字节长

MIPS的浮点操作

- MOV.S和MOV.D分别把一个单/双精度浮点数寄存器的值复制到另一个同类型的寄存器中。 MFC1、MTC1、DMFC1和DMTC1在一个单精度或双精度浮点数寄存器和一个定点寄存器之间传送数据。

- 浮点操作:加、减、乘、除。后缀S表示单精度浮点数,而后缀D表示双精度浮点数。

- 为提高图形处理性能,MIPS64提供了在一个64位浮点数寄存器两半部分中分别进行两个32位浮点数的操作。

了解:谬误与易犯的错误

(下面五条是正确说法)

- 不能设计专门支持高级语言结构的“高级”指令功能。

- 不存在一种典型的程序。

- 不可以不考虑编译器而改进指令系统以缩减代码大小。

- 有缺陷的系统结构有可能是一种成功的系统结构。

- 不可以设计一个没有缺陷的系统结构。

本章小结

掌握(重点):指令系统结构分类,存储器寻址,操作数的大小与类型,MIPS系统结构。

理解:指令系统的操作,控制流指令,指令系统的编码。

了解:编译技术与计算机系统结构的相互影响

![[激光原理与应用-69]:激光焊接的10大常见缺陷及解决方法](https://img-blog.csdnimg.cn/img_convert/e6729b60670d0f3ec1c4e4531bb348f3.jpeg)

![[架构之路-203] - 对系统需求类型的进一步澄清](https://img-blog.csdnimg.cn/3b12bffe074b41c480a0733e5f2854d5.png)