我们这里通过debug抓一个普通led工程的部分信号

下面是代码,输入差分200M

1.整体代码

`timescale 1ns / 1ps

module led_test(

//Differential system clocks

sys_clk_p,//200M

sys_clk_n,

rst_n, //S1

led

);

input sys_clk_p;

input sys_clk_n;

input rst_n;

output [1:0] led;

wire sys_clk;

reg [31:0] count;

reg [1:0] led_cnt;

GTP_INBUFGDS GTP_INBUFGDS_inst

(

.O (sys_clk ),

.I (sys_clk_p),

.IB (sys_clk_n)

);

//1s

always@(posedge sys_clk or negedge rst_n)begin

if(!rst_n)

count <= 32'd0;

else if(count == 32'd99000000)

count <= 32'd0;

else

count <= count + 1'b1;

end

always@(posedge sys_clk or negedge rst_n)begin

if(!rst_n)

led_cnt <= 2'd0;

else if(count == 32'd99000000)

led_cnt <= led_cnt + 1'b1;

end

assign led = led_cnt;

endmodule2.工程编译

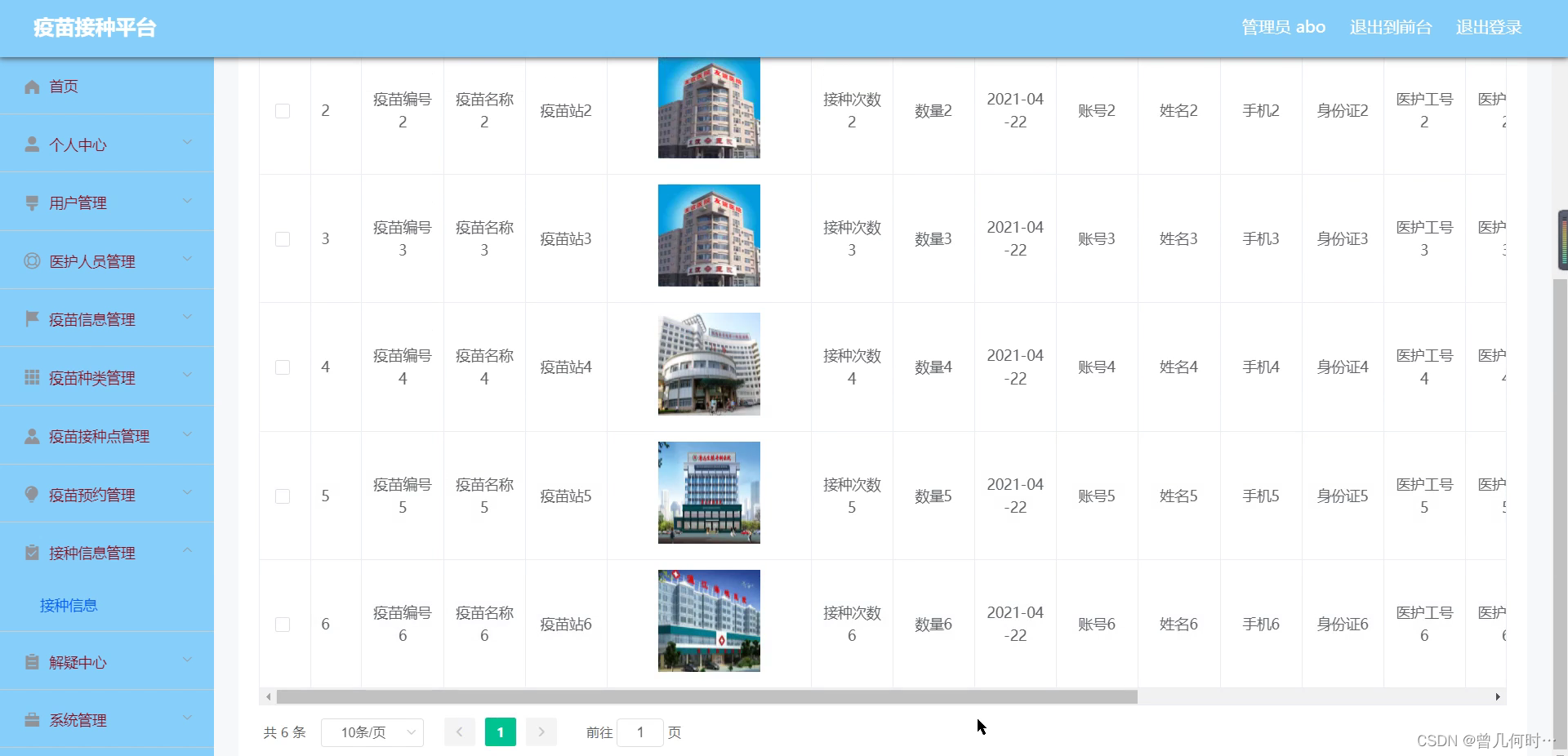

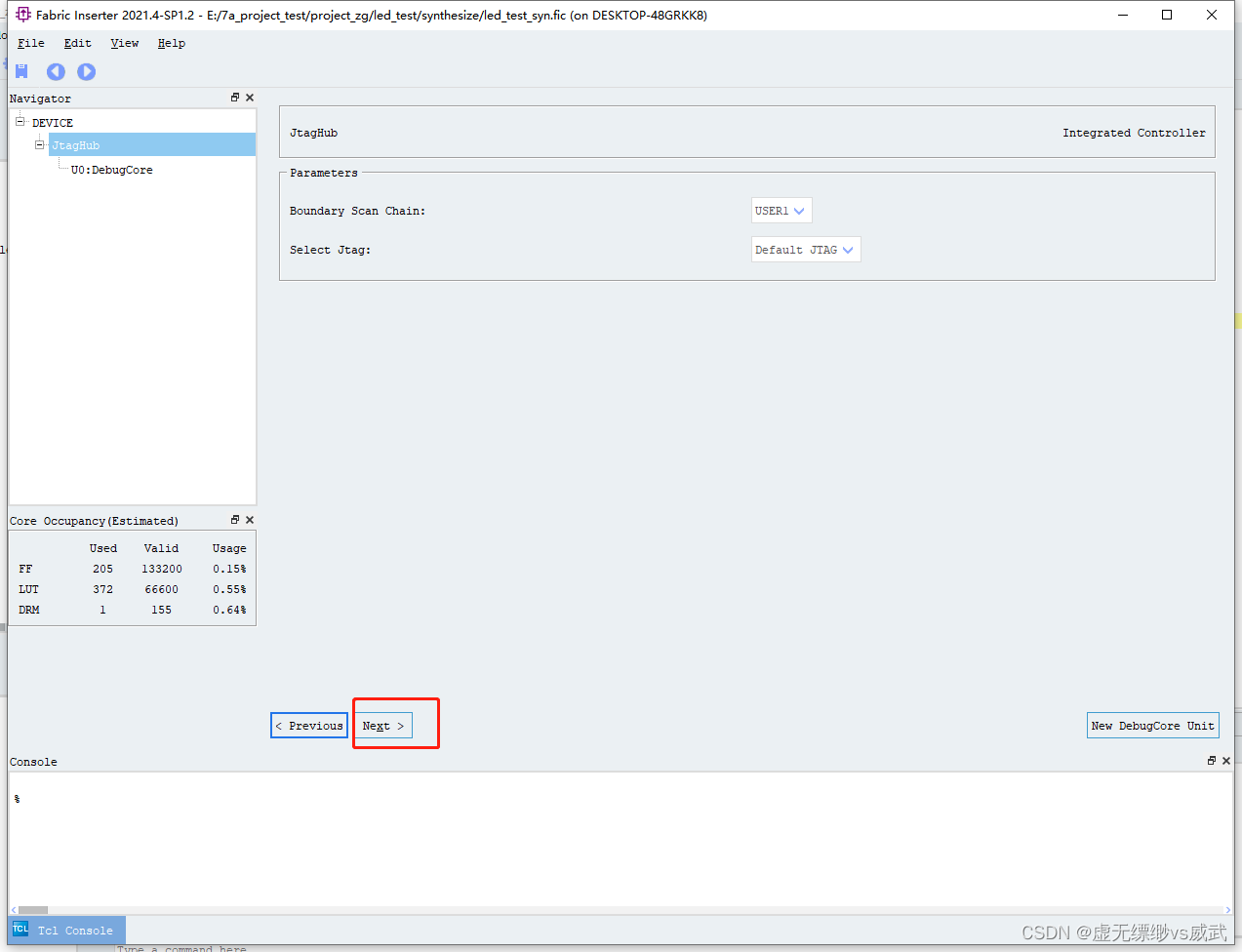

3.添加debug和测试管脚

选择Tools-->Inserter

点击Next

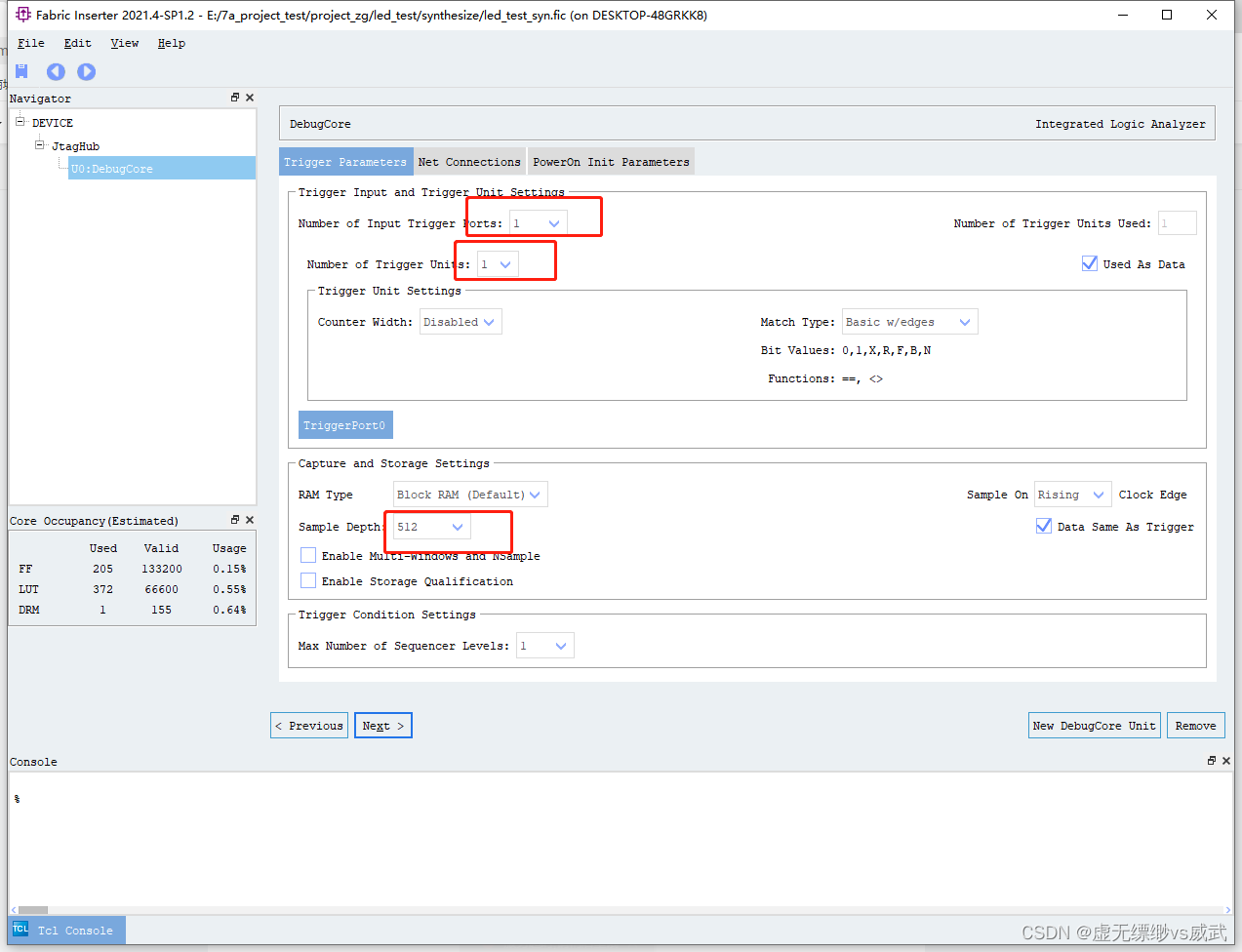

这里简单设置通道数和抓取深度

点击Next

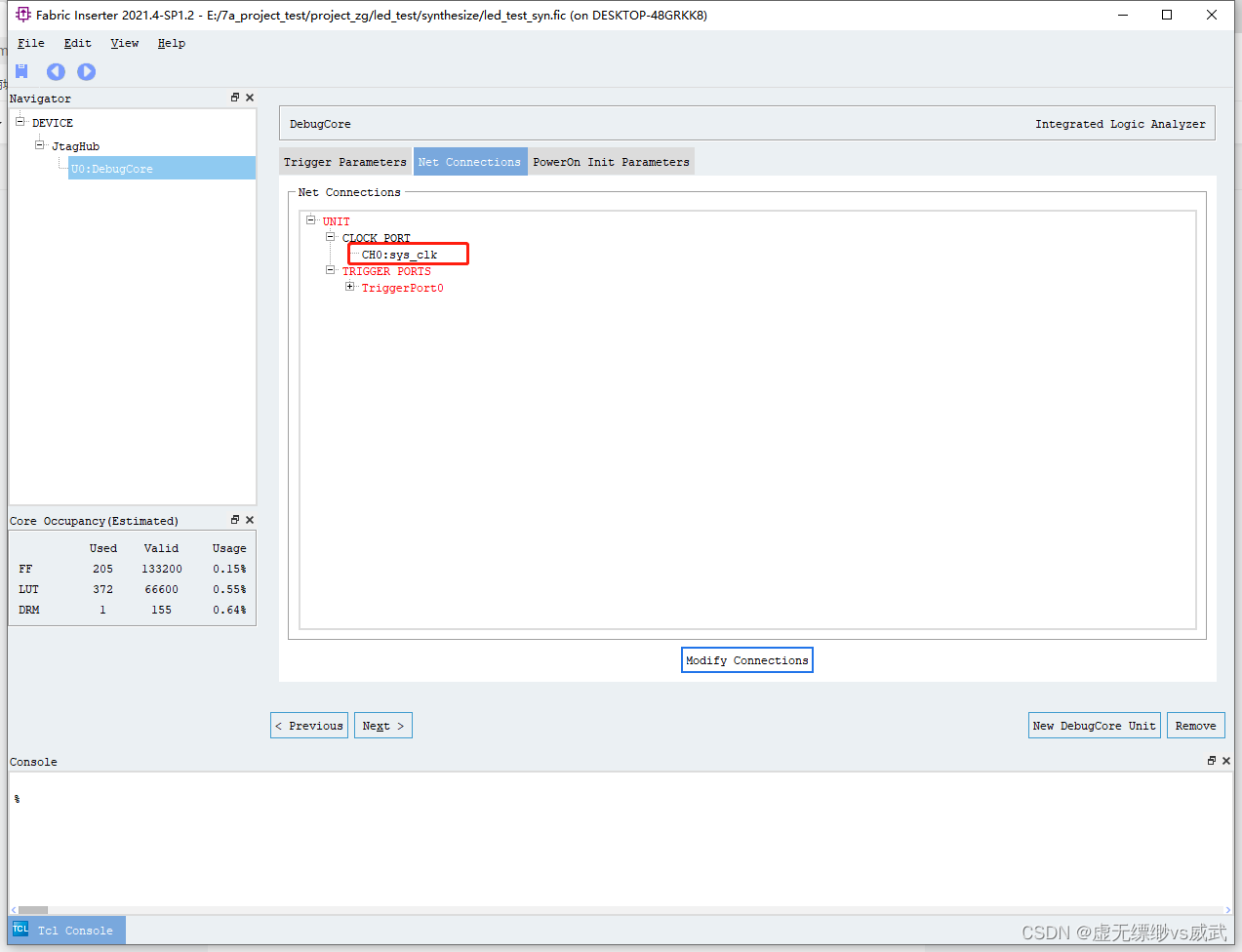

第一步点击CH0,第二步点击Modify

在弹出的对话框中选择采集时钟sys_clk

按住鼠标将sys_clk拖到clock下,然后点击OK

可以看到采集时钟已经加进来了

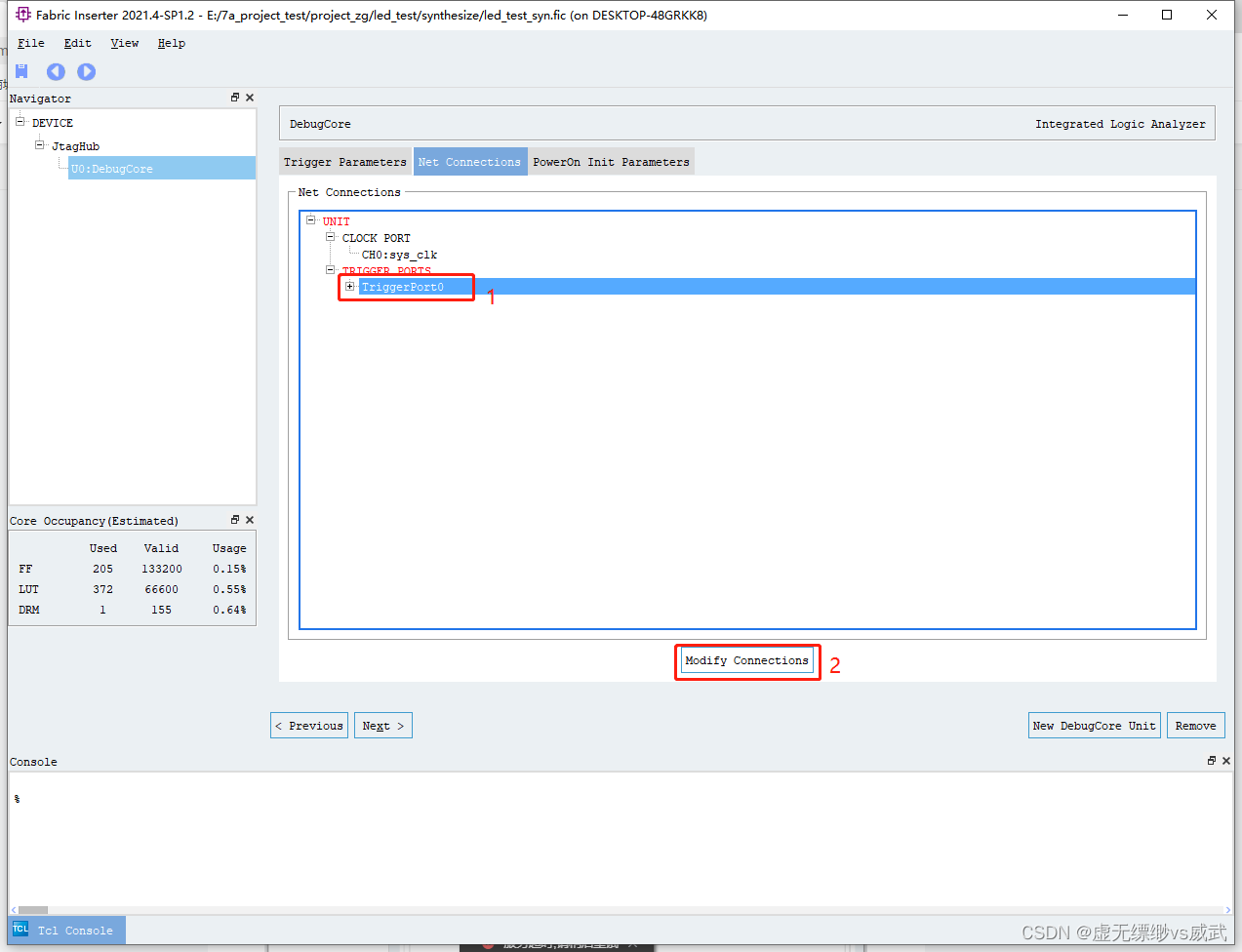

选中红框1的位置,然后点击菜单2

将测试管脚拖到右边位置

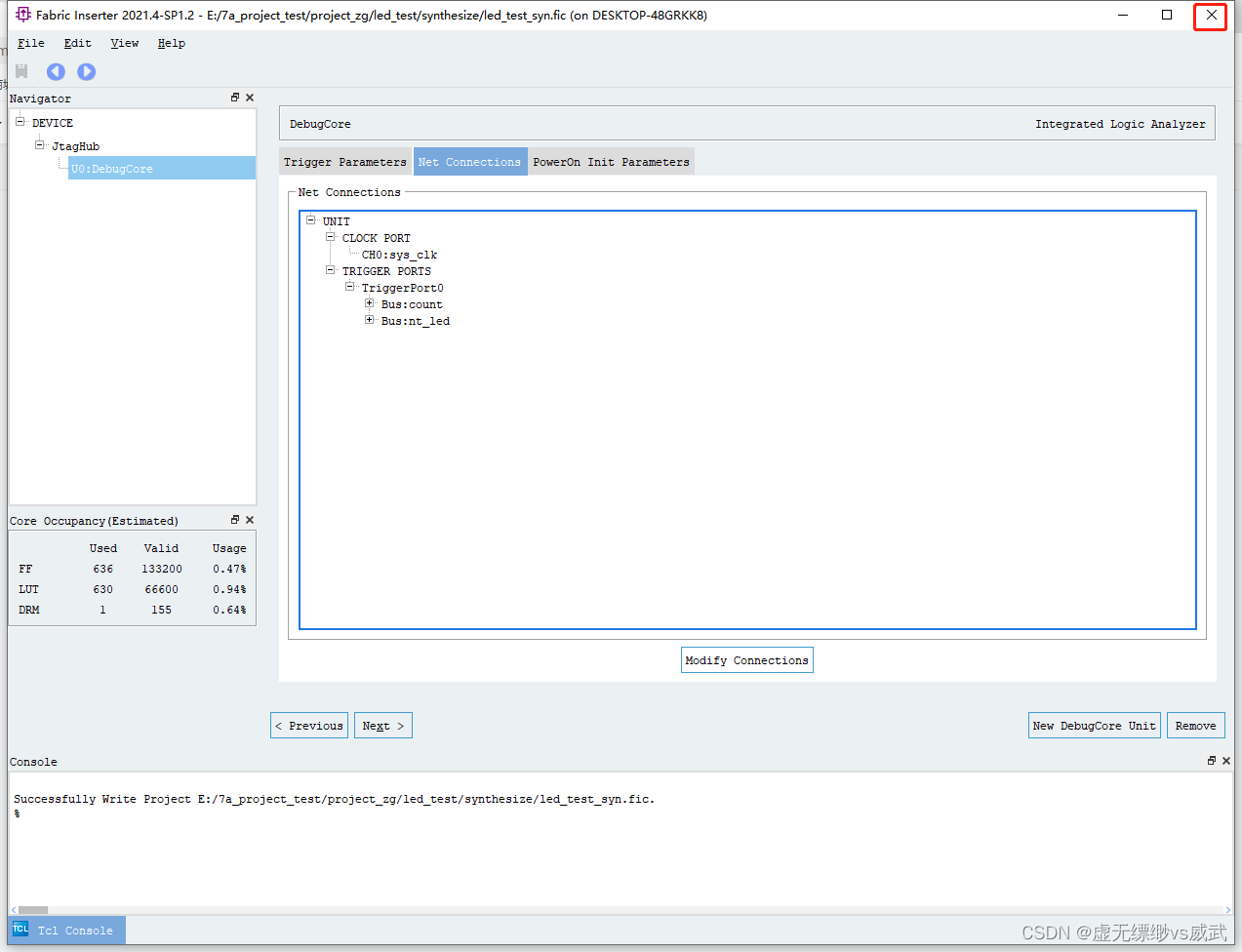

可以看到测试的管脚已经加入进来了

点击保存图标

点击右上角X关闭对话框

4.编译工程

在Generate Bitstream上右击选择Rerun All编译工程

工程编译完成

工程编译完成

5.下载工程文件

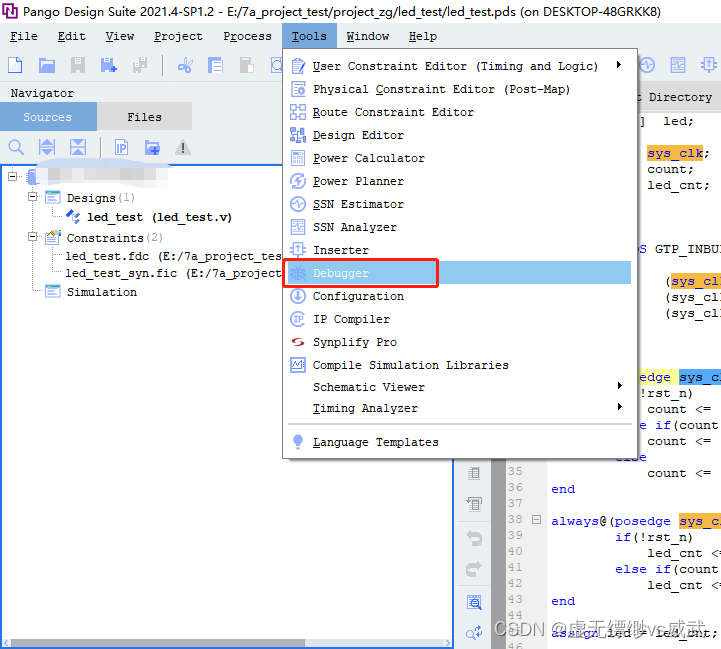

选择Tools-->Debugger

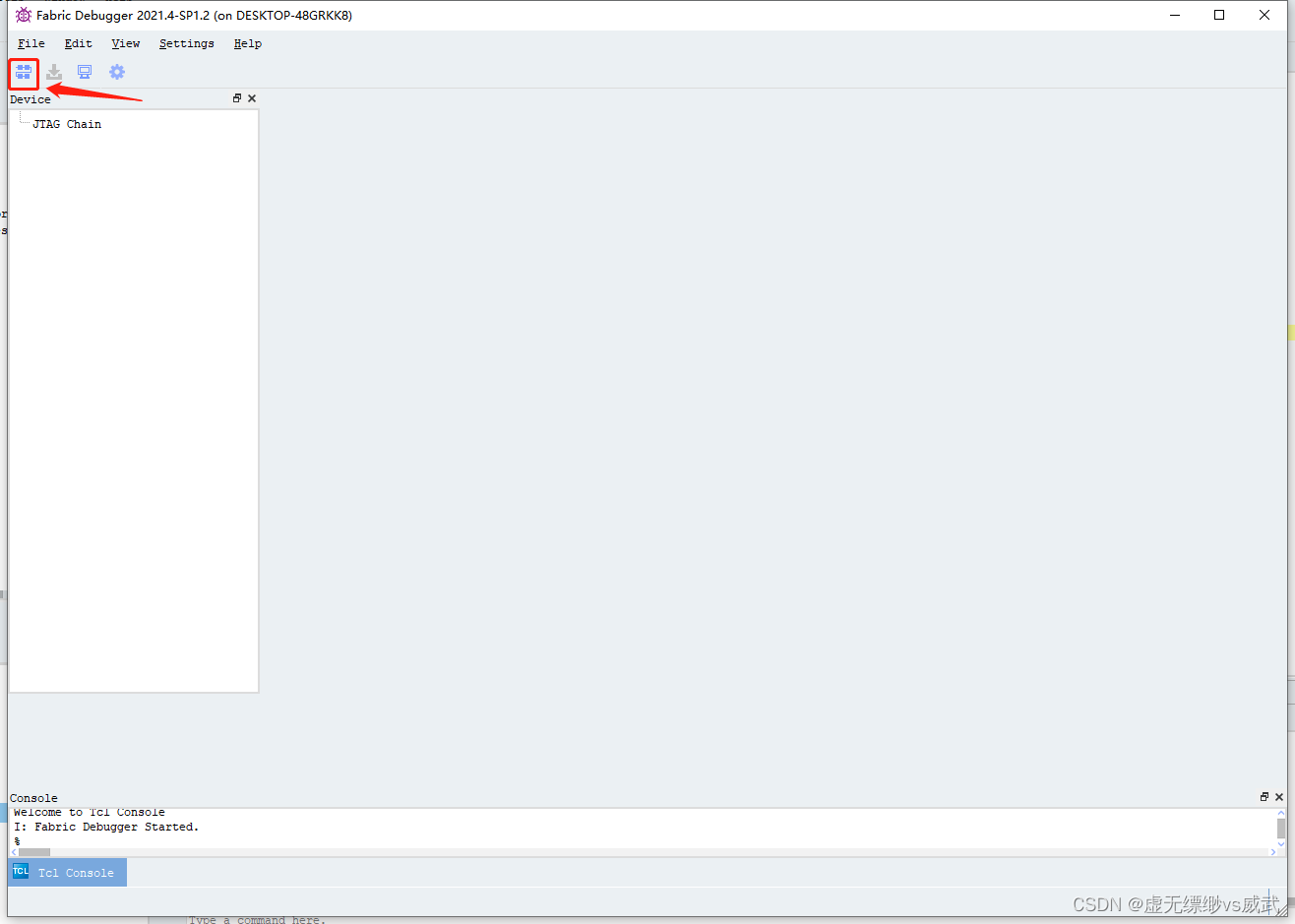

点击这个红色方框

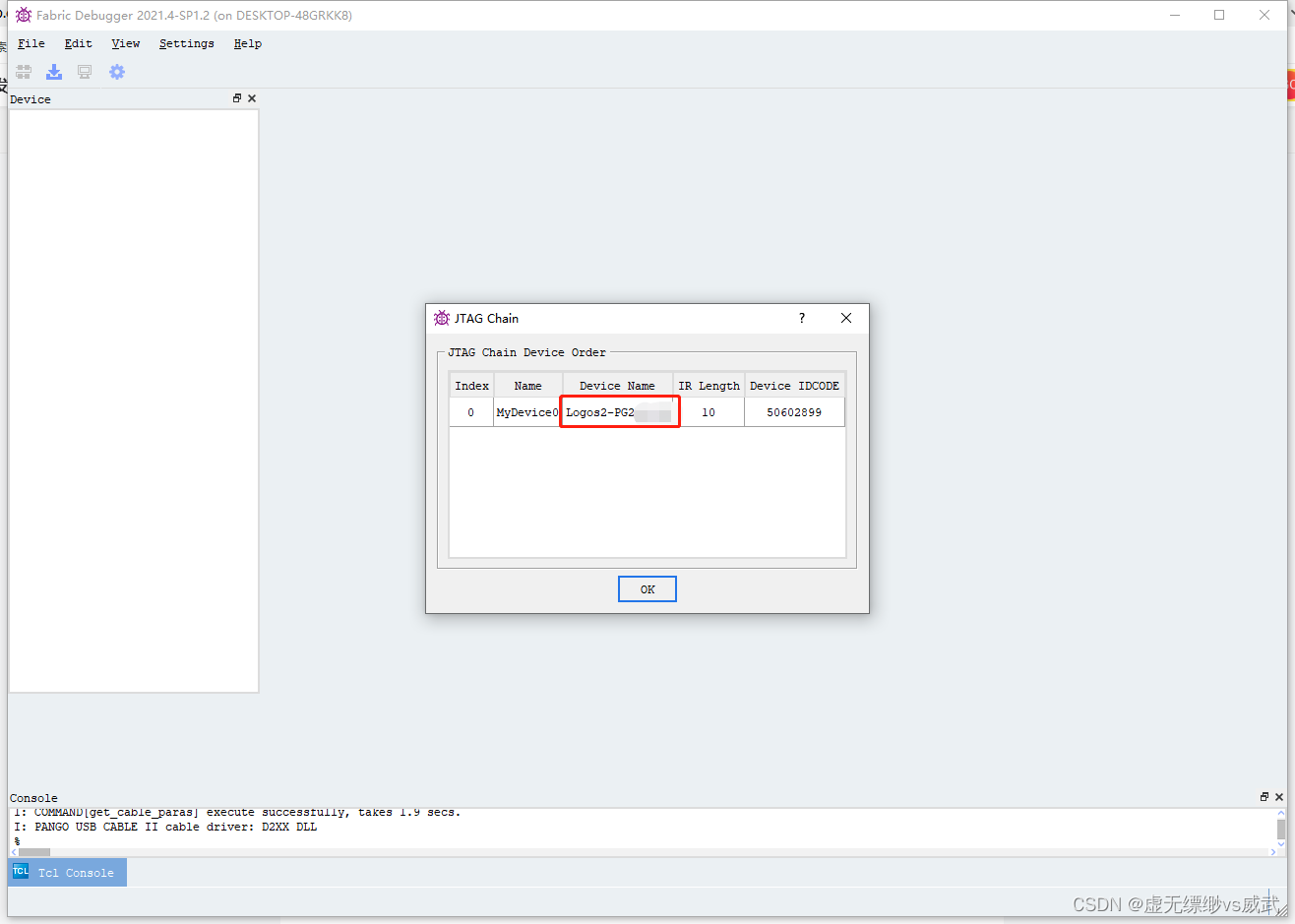

能检测到芯片型号表示jtag连接正常 ,点击OK

然后出现这个界面

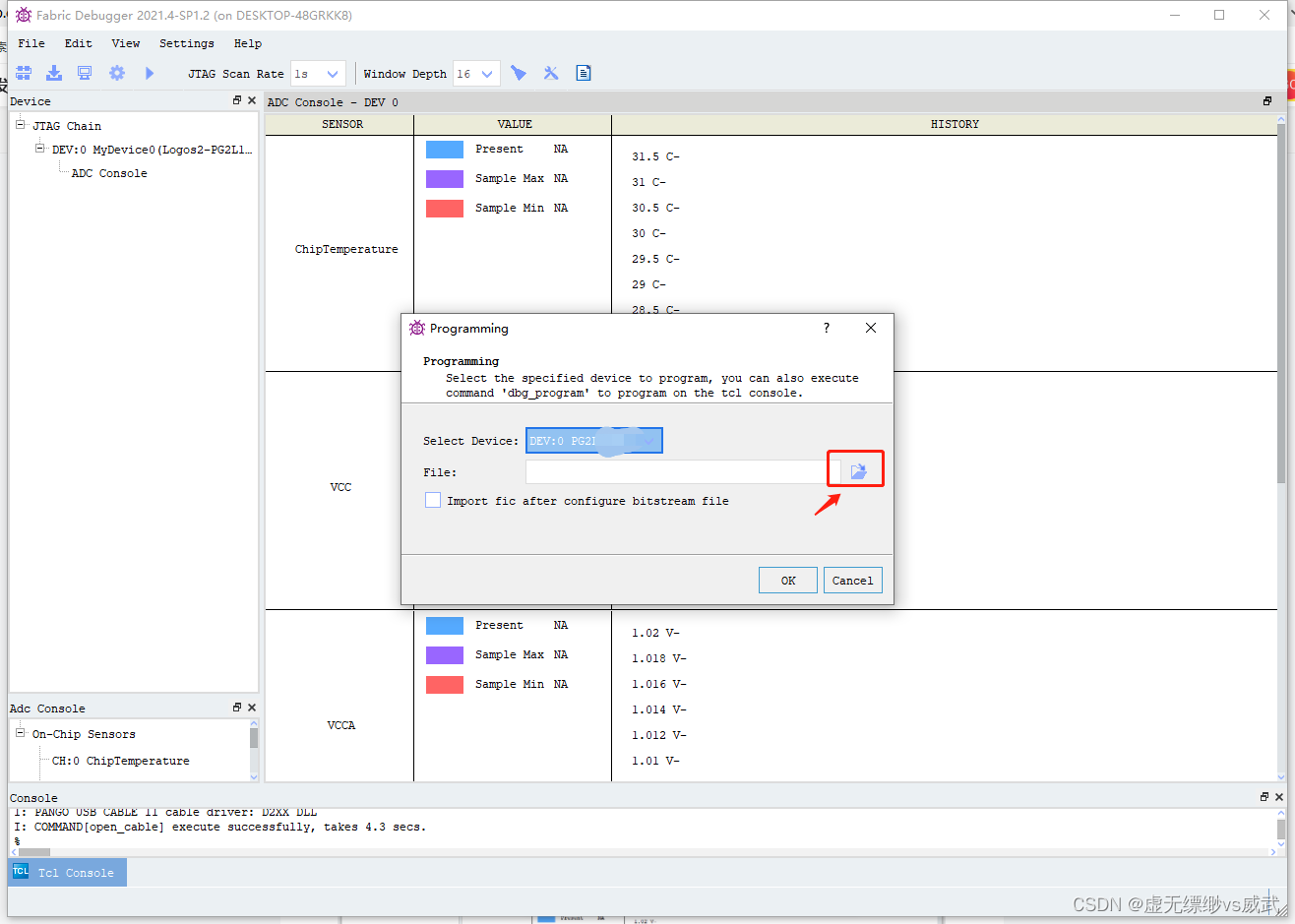

点击下载文件这个图标

点击这个文件夹图标选择工程文件

选中工程文件点击Open

添加需要下载的sbit文件,点击OK

程序正在下载中

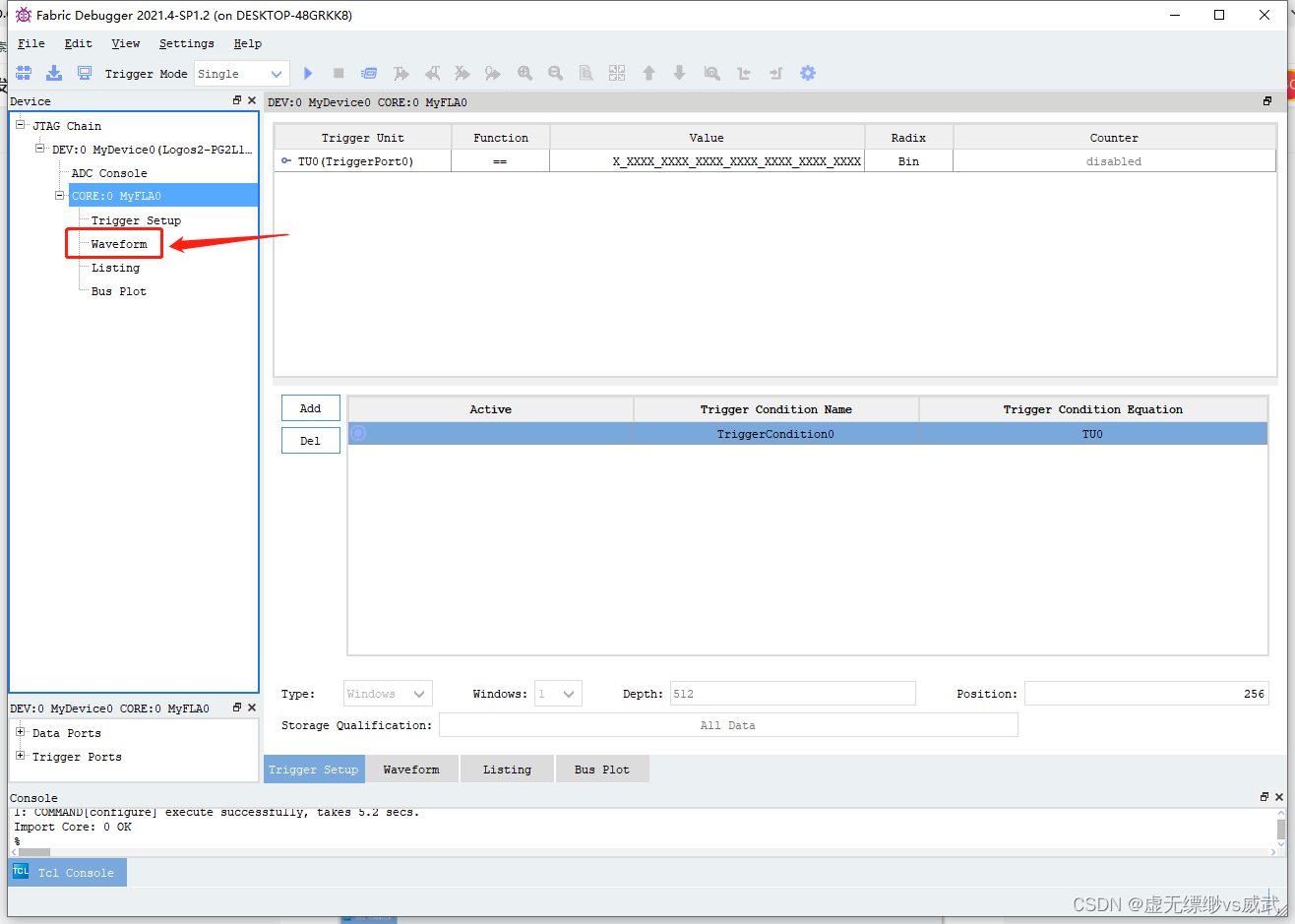

6.波形抓取

程序下载完成后,点击波形这个

可以看到要抓取波形的界面

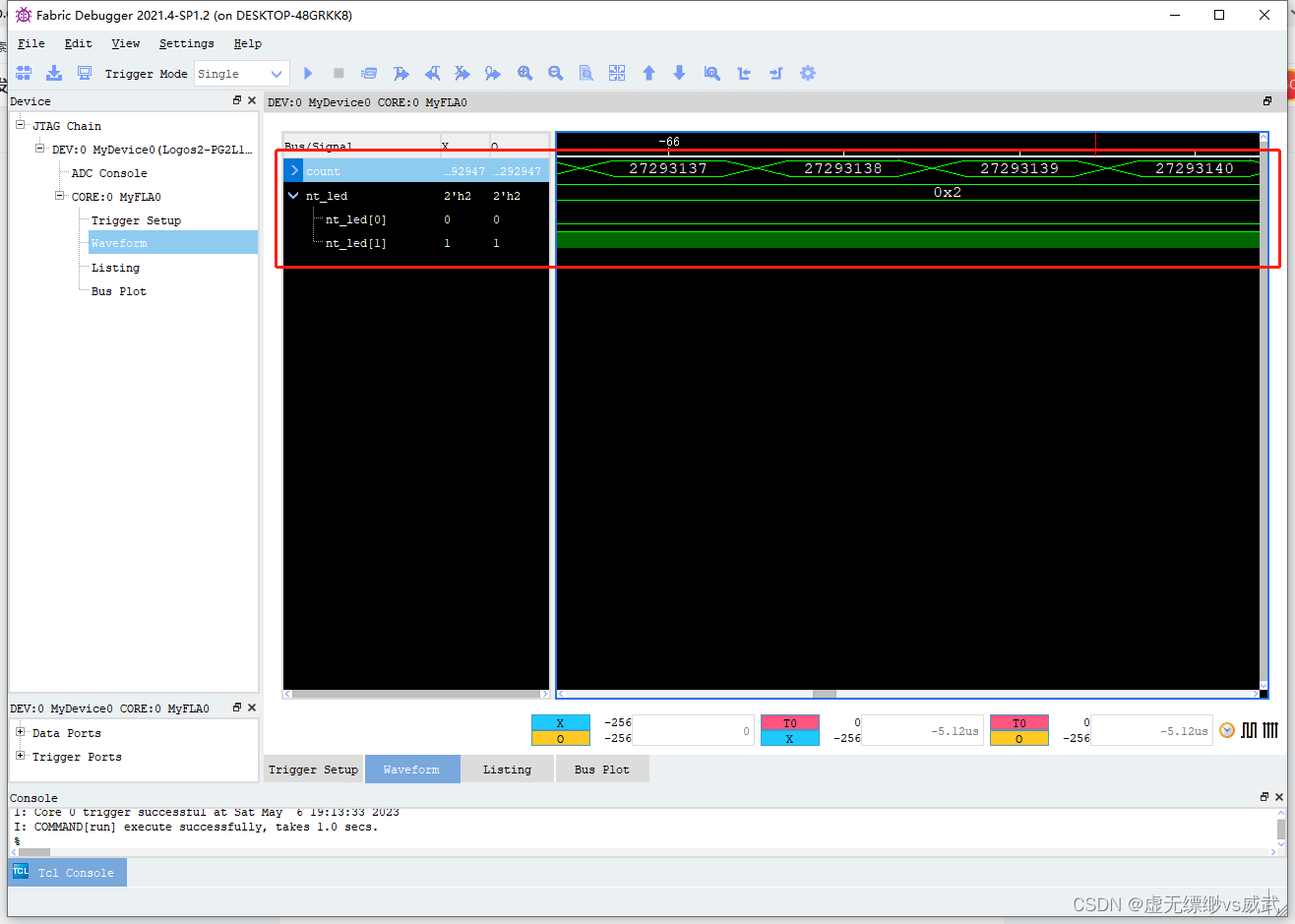

点击运行

将波形拉大后可以看计数值和led的电平

如若转载请注明出处