目录

输入功能

浮空输入:通俗讲就是让管脚什么都不接,悬空着。

上拉输入

下拉输入

模拟输入

输出功能

开漏输出

推挽输出

相关寄存器

GPIOx_MODER 端口模式寄存器

GPIOx_OTYPER 端口输出类型寄存器

GPIOx_ OSPEEDR 端口输出速度寄存器

GPIOx_PUPDR 上拉/下拉寄存器

GPIOx_IDR 端口输入数据寄存器

GPIOx_ODR 端口输出数据寄存器

GPIOx_BSRR 置位 / 复位寄存器

输出试验:点亮一盏灯

》1.查看自己想要点亮的灯编号

编辑

》2.对比电路原理图

》3.编程实现

结果:

输入功能

浮空输入:通俗讲就是让管脚什么都不接,悬空着。

此时VDD和VSS所在路径的两个开关同时断开。因为没有上拉和下拉,所以当IO口没有接输入的时候,此时的电平状态会是一个不确定的值,完全由外部输入决定。(一般实际运用时,引脚不建议悬空,易受干扰。 )

优势:这一种输入模式的电平会完全取决于外部电路而与内部电路无关

缺点:在没有外部电路接入的时候,IO脚浮空会使得电平不确定

应用:该模式是STM32复位之后的默认模式,一般用作对开关按键的读取或用于标准的通讯协议,比如IIC、USART的等

上拉输入

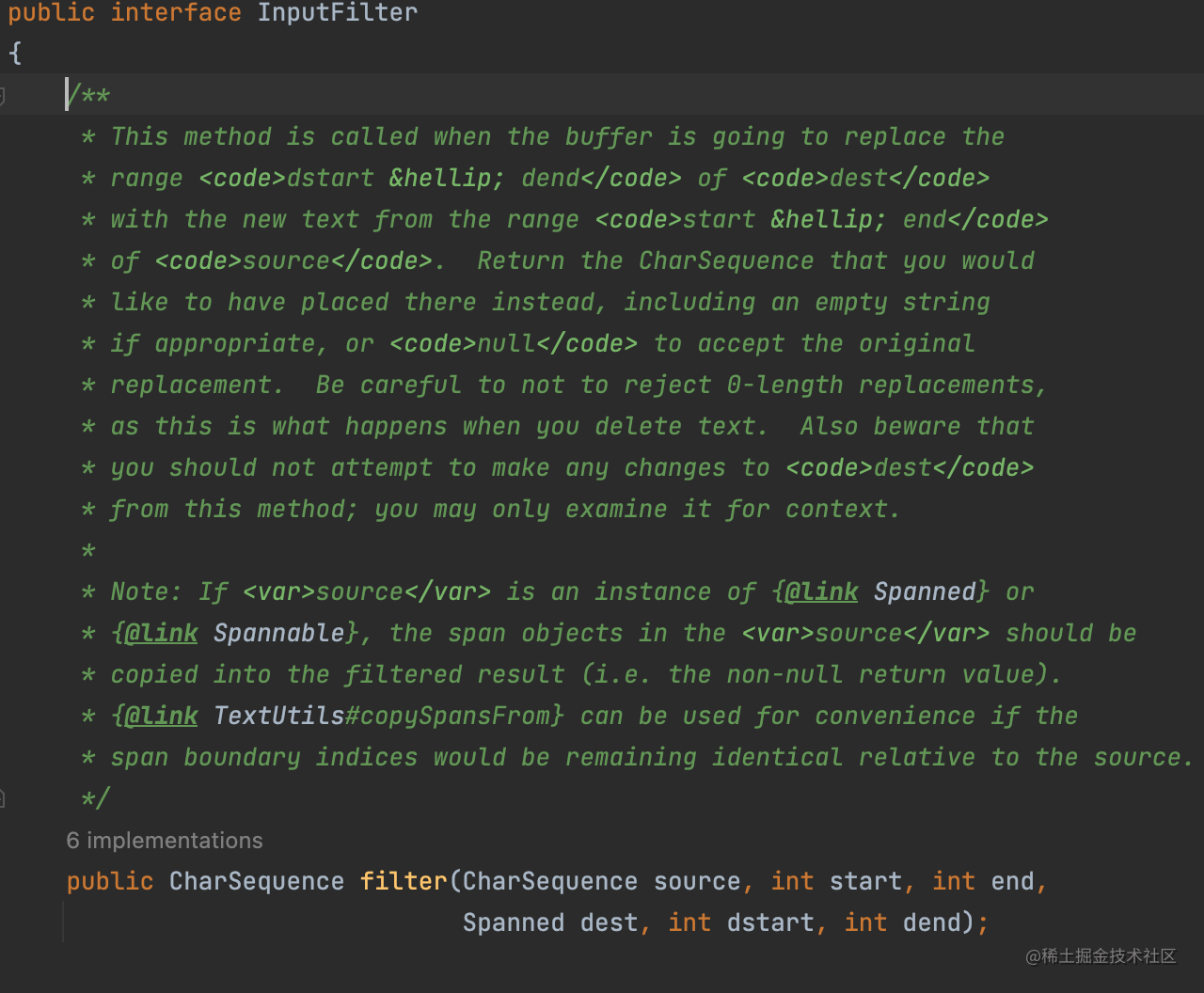

IO端口 - 上拉电阻 - 施密特触发器 - 输入数据寄存器 - 读

输入的电平不会因上下浮动而导致输入信号不稳定,当外部没有信号输入时,上拉电阻会将输入信号钳在高电平,此时引脚始终读到高电平信号。

下拉输入

IO端口 - 下拉电阻 - 施密特触发器 - 输入数据寄存器 - 读

输入的电平不会因上下浮动而导致输入信号不稳定,当外部没有信号输入时,下拉电阻会将输入信号钳在低电平,此时引脚始终读到低电平信号。

模拟输入

未经任何处理的信号

信号进入后不经过上拉电阻或者下拉电阻,关闭施密特触发器,经由另一线路把电压信号传送到片上外设模块。 所以可以理解为模拟输入的信号是未经处理的信号,是原汁原味的信号。

应用:当 GPIO 引脚用于 ADC 采集电压的输入通道时,则需要选择“模拟输入”功能,因为经过施密特触发器后信号只有 0、1 两种状态,所以 ADC 外设要采集到原始的模拟信号,信号源输入必须在施密特触发器之前。

输出功能

开漏输出

输出寄存器上的'0'激活 N-MOS,而输出寄存器上的'1'将端口置于高阻状态 (P-MOS 从不被激活 )。

无法真正输出高电平,即高电平时没有驱动能力,需要借助外部上拉电阻完成对外驱动。

可以利用改变上拉电源的电压来适应所需,进而提高外部电路的驱动能力。

- 在推挽输出模式下,引脚可以提供两个状态的输出:高电平(Vcc)和低电平(GND)。

- 当引脚处于高电平状态时,它会提供一定的输出电流,以使外部设备工作在高电平逻辑状态。

- 当引脚处于低电平状态时,它会提供接近零的输出电压,以使外部设备工作在低电平逻辑状态。

- 推挽输出模式通常用于驱动主动电路(如LED、电机、显示器等),可以提供较高的驱动能力,适用于直接驱动大多数负载。

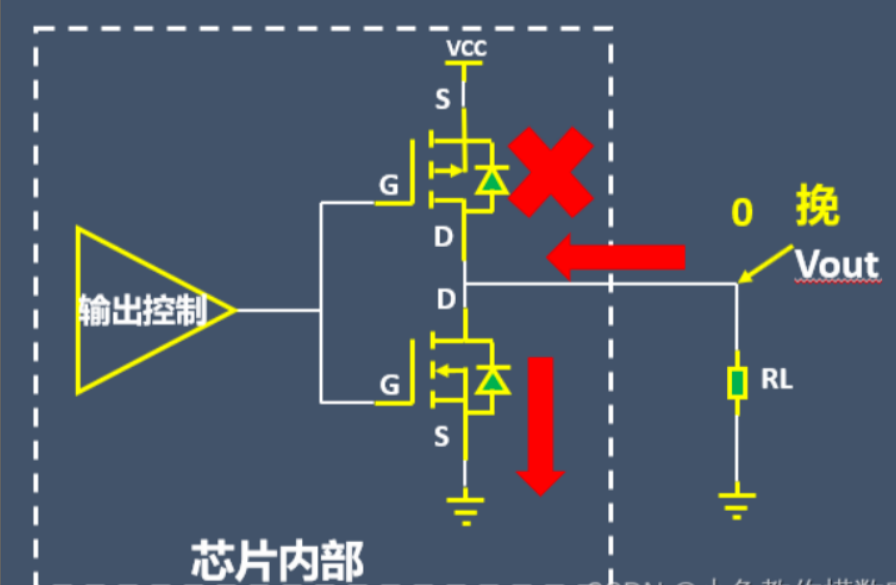

推挽输出

输出寄存器上的'0'激活 N-MOS,而输出寄存器上的'1'将激活 P-MOS,具备输出高低电平的能力。

当上面的MOS管导通时,GPIO输出高电平1,称为“推”。

当下面MOS管导通时,GPIO输出低电平0,称为“挽”。

- 在开漏输出模式下,引脚只提供低电平状态(GND)的输出。而在高电平状态时,引脚会断开,不提供输出电压。

- 在开漏模式下,引脚上有一个开漏晶体管,可以将引脚连接到GND,但不能将其连接到高电平(Vcc)。

- 为了使引脚达到高电平状态,需要通过外部上拉电阻将引脚连接到Vcc。当引脚处于开漏状态时,它不提供输出电流,而是允许外部电路或器件通过上拉电阻拉高电平。

- 开漏输出模式通常用于驱动被动电路(如信号线、总线等),可以实现多个开漏输出引脚的集线器功能,适用于需要共享总线或多点连接的情况。

相关寄存器

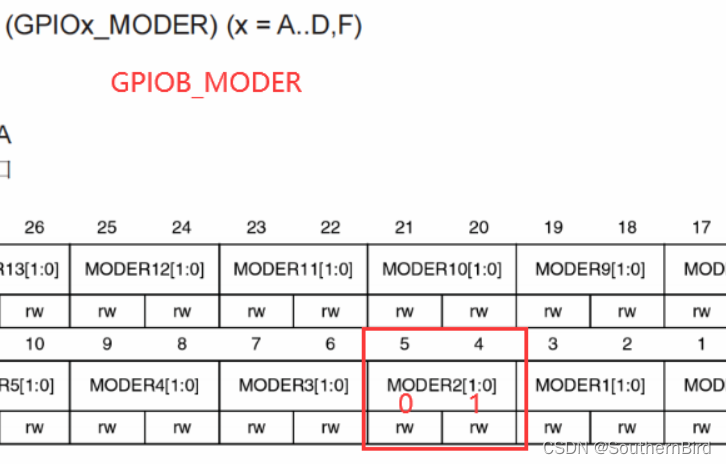

GPIOx_MODER 端口模式寄存器

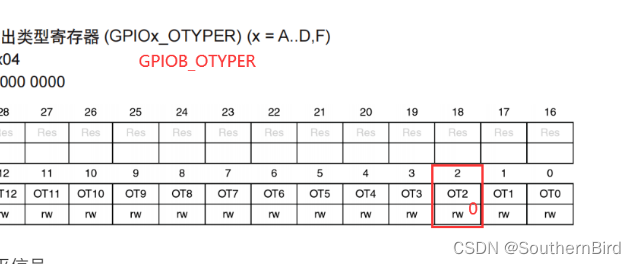

GPIOx_OTYPER 端口输出类型寄存器

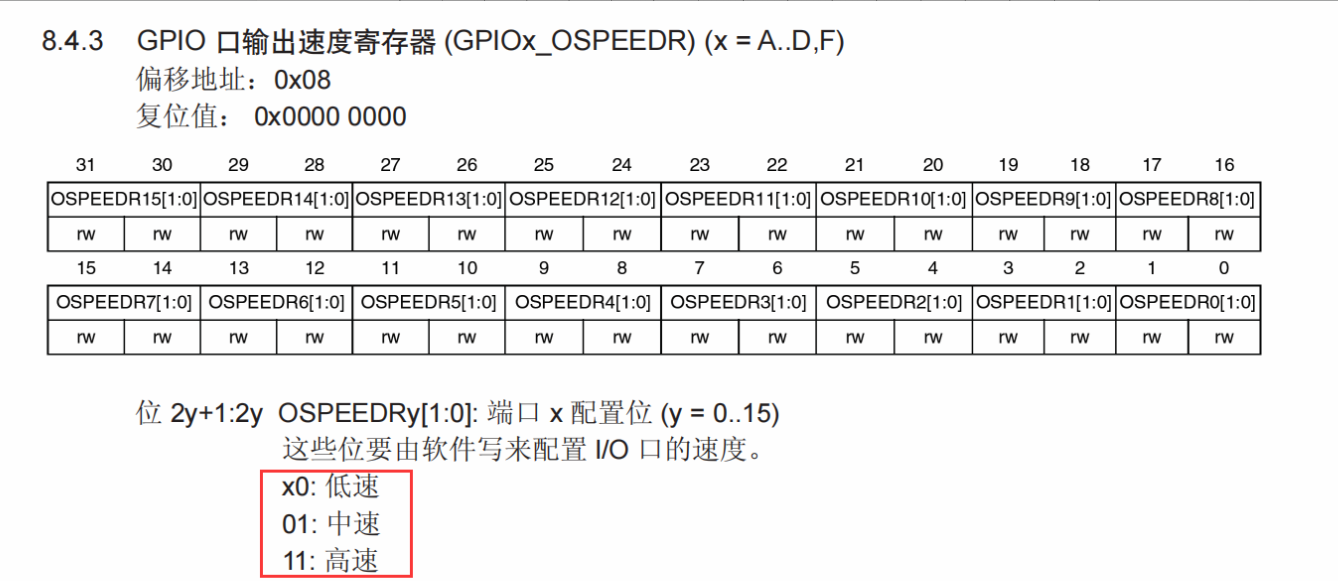

GPIOx_ OSPEEDR 端口输出速度寄存器

GPIOx_PUPDR 上拉/下拉寄存器

GPIOx_IDR 端口输入数据寄存器

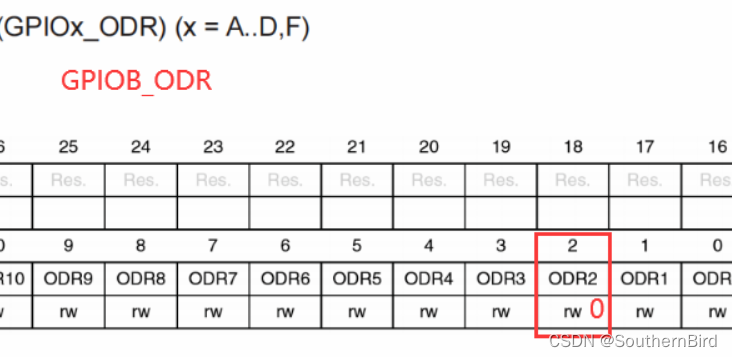

GPIOx_ODR 端口输出数据寄存器

GPIOx_BSRR 置位 / 复位寄存器

输出试验:点亮一盏灯

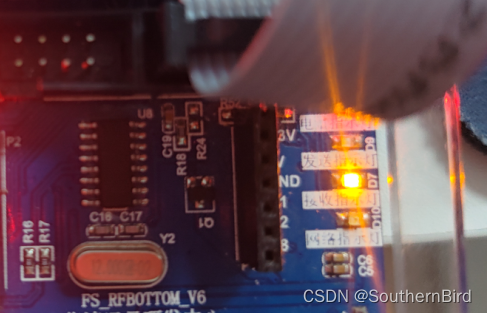

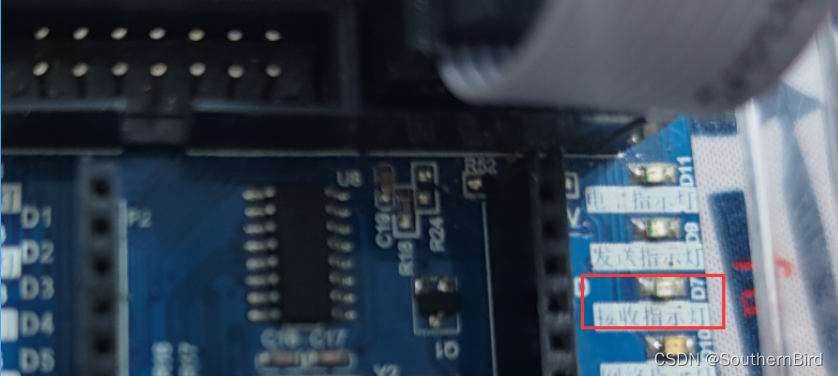

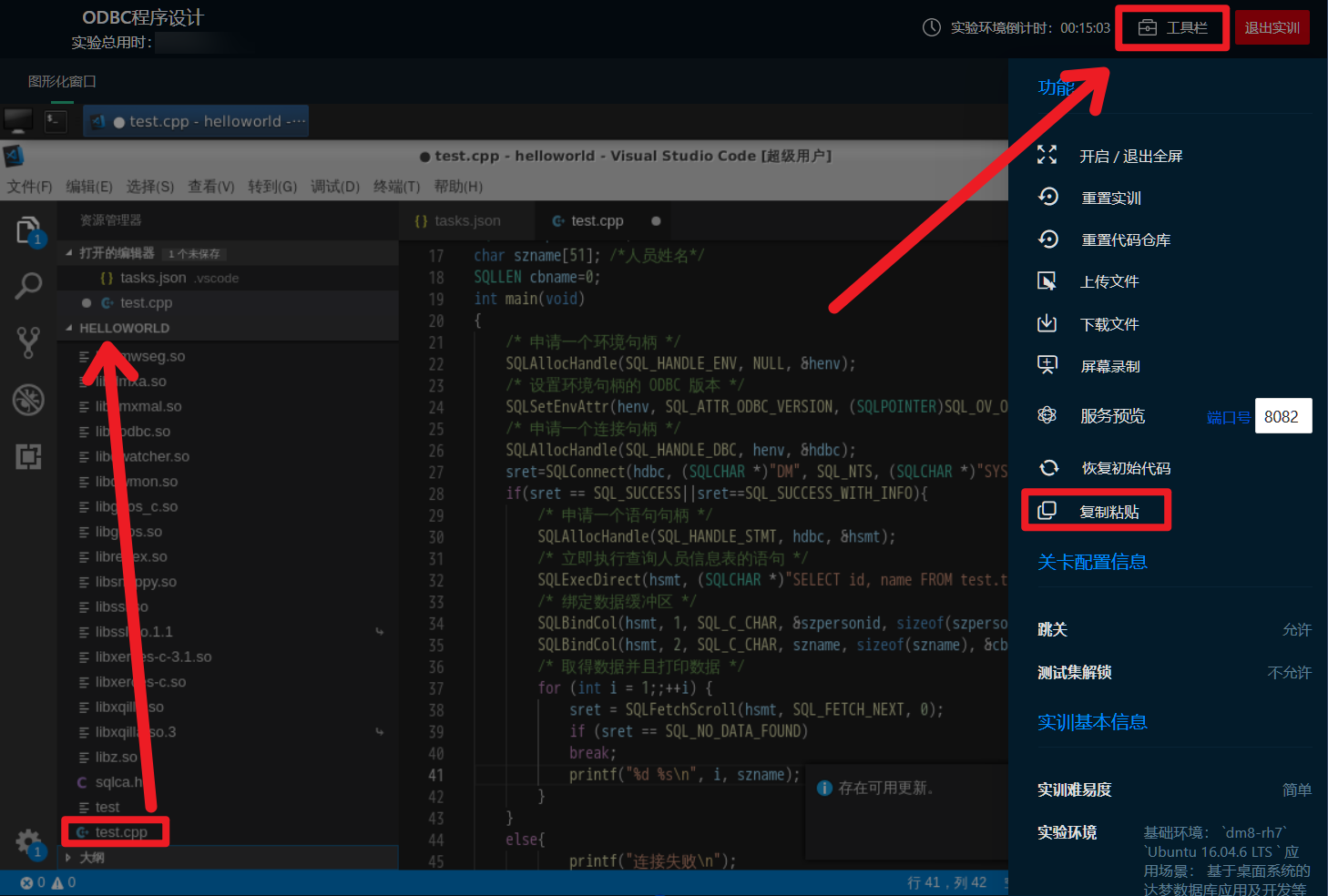

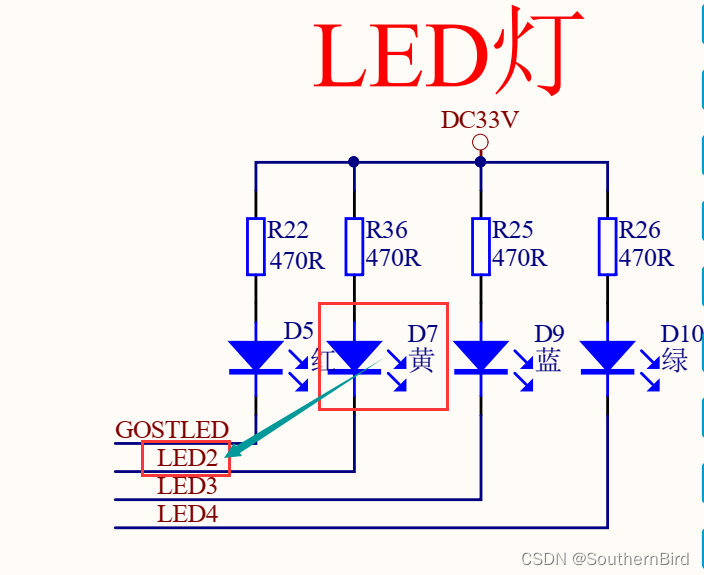

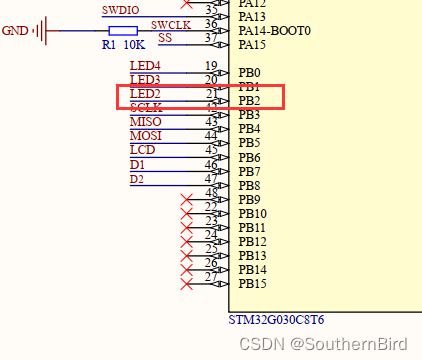

》1.查看自己想要点亮的灯编号

》2.对比电路原理图

让PB2引脚输出电平就可以点亮灯。

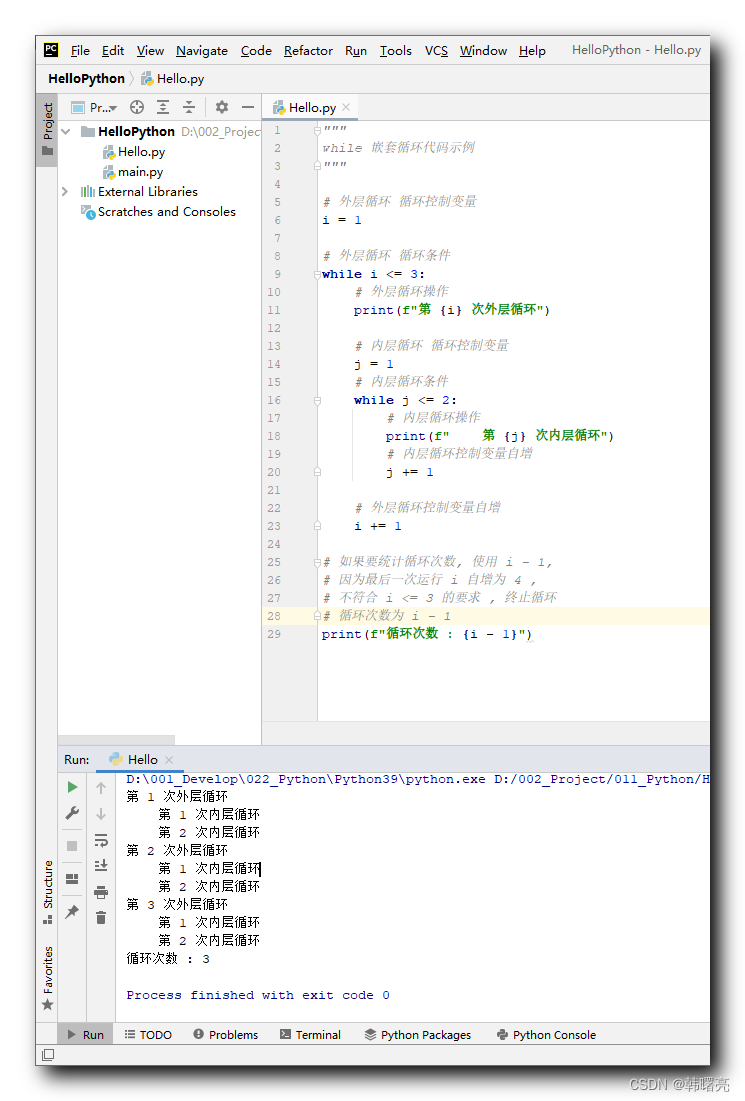

》3.编程实现

分以下几步:

第一步:必须开启GPIOB的时钟,开启时钟才能让单片机知道时间的概念

将GPIOBEN置为1,就能开启时钟

第二步:将PB2设置为输出模式

第三步:选择输出类型

我选择了推挽输出

第四步:选择输出的电平信号

根据分析的结果添加代码,实现功能。

ps:csdn出了添加代码包功能,挺不错的,代码就放在上面了

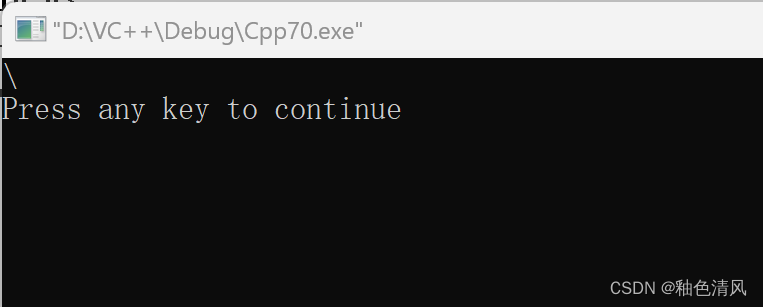

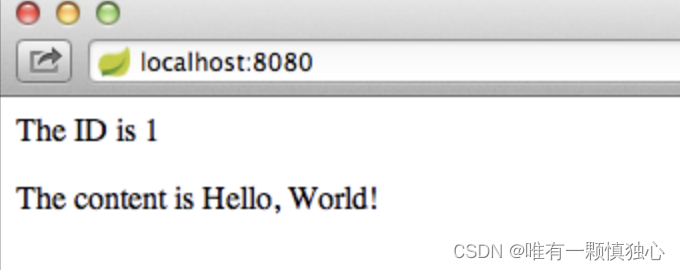

结果: