目录

0、前言

1、硬件状态确认

2、DDR3调试

2.1 DDR3初始化

2.2 DDR3读写测试

2.3 DDR3 ECC(略)

0、前言

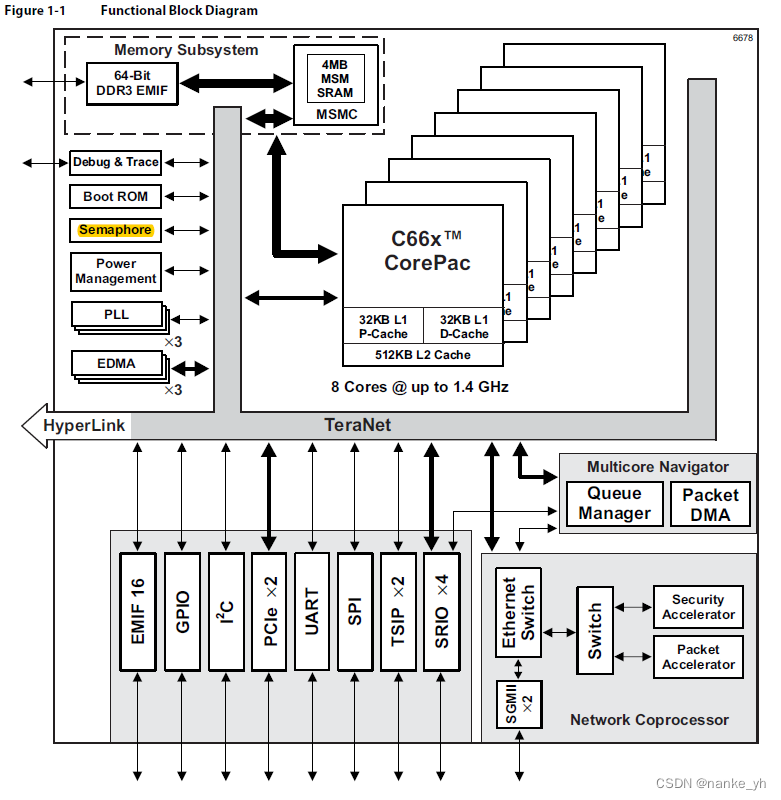

本来在写完《DSP篇--C6678 SPI BOOT详解及其优化实现》这篇文章后是不打算再去更新嵌入式相关的博文了(主要是换行业了)。但是架不住有很多从事嵌入式软件开发相关的粉丝因为看到上面文章后私信问我问题。相隔太久远了,很多我也答不上来,这里只能将以前自己调试C6678记录的心得笔记,写出来供给粉丝们看,希望对你们有所帮助。

这个系列除上面BOOT其他的将包含DDR3、EMIF、GPIO、Nor_FLASH、EDMA3、SPI、TIMER、UART、GE网络等等。

1、硬件状态确认

外部电源确认:电压5V、限流1A

仿真器连接确认:软件target与仿真器配套;connect连接。

时钟确认:主要确认主频、倍频等

2、DDR3调试

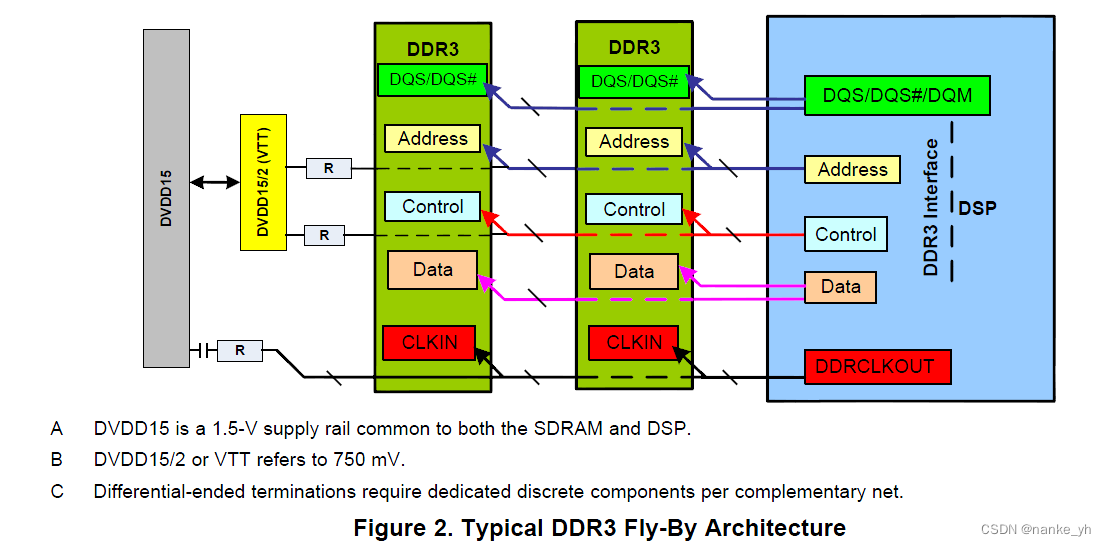

DDR3是在DDR2基础上升级的产品,其作为存储外设单元,主要受时钟的影响。

特性:1、 Read leveling 2、Write leveling3、 Change in pre-fetch size 4、ZQ calibration 5、 A reset pin

功能有:数据存储(读写),以及ECC (Error Correction)。通过接线支持16bit、32bit以及64bit数据读写,并且可产生1位、2位错纠正。

2.1 DDR3初始化

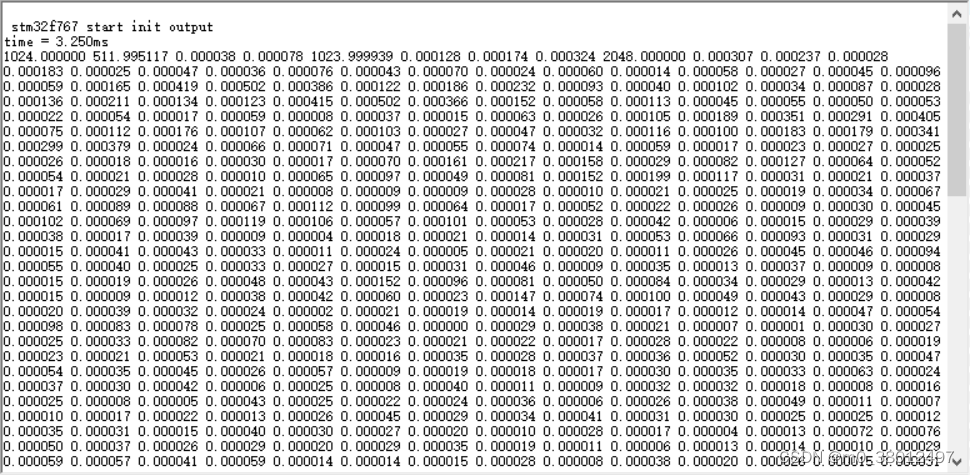

受主频的影响://DDR init 100*40/3= 1333 MHz

UINT32 KeyStone_DDR_init(float ref_clock_MHz, unsigned int DDR_PLLM,unsigned int DDR_PLLD, DDR_ECC_Config * ecc_cfg)

DDR_Speed_MHz = ref_clock_MHz*DDR_PLLM/DDR_PLLD;

DDR_Clock_MHz = DDR_Speed_MHz/2; //data speed is double of clock speed2.2 DDR3读写测试

DDR3容量2GB,地址空间为0x8000,0000~0xFFFF,FFFF。测试方法:

for(i=0;i<(0x10000000);i++)

{

*(volatile unsigned long long*)(0x80000000+i*8)=0xffffffffffffffff;

if(*(volatile unsigned long long*)(0x80000000+i*8)!= 0xffffffffffffffff)

{

ddr_err_count++;

}

}1) 向DDR3地址0x8000,0000~0xFFFF,FFFF写入数据0xFFFF,FFFF;

2) 读取写入的数据,若不等于0xFFFF,FFFF,则错误计数n加1,若n为0则读写全部正确;

3) 向DDR3地址0x8000,0000~0xFFFF,FFFF写入数据0x55555555;

4) 读取写入的数据,若不等于0x55555555,则错误计数n加1,若n为0则读写全部正确。

5) 向DDR3地址0x8000,0000~0xFFFF,FFFF写入数据0xaaaaaaaa;

6) 读取写入的数据,若不等于0xaaaaaaaa,则错误计数n加1,若n为0则读写全部正确。

7) 向DDR3地址0x8000,0000~0xFFFF,FFFF写入数据0x0;

8) 读取写入的数据,若不等于0x0,则错误计数n加1,若n为0则读写全部正确。

2.3 DDR3 ECC(略)

1、填充

2、校错

![[附源码]计算机毕业设计springboot新冠疫苗接种预约系统](https://img-blog.csdnimg.cn/f811eb82f9a7496e9b996ef514694fd1.png)