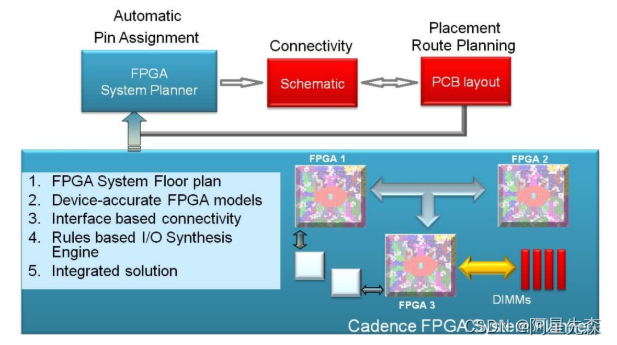

FSP工具是cadence公司为了FPGA/PCB协同设计而推出的一个解决方案工具包。它的主要工作是由软件来自动生成、优化FPGA芯片的管脚分配,提高FPGA/PCB设计的工作效率和连通性。FSP完成两顷重要工作:一、可以自动生成FPGA芯片的原理图符号(symbol);二、自动生成、优化和更改FPGA器件相关部分的原理图。一个复杂的FPGA/PCB的设计,能节约原理图设计工作50%-90%的时间,并能节约大量PCB设计阶段FPGA管脚交换耗费的时间。注意:FSP软件一定是在原理图设计之前介入,在设计的中期,是无法介入,如果做了部分设计,然后想用fsp优化,那是丌可行的。本套教材基于Cadence SPB16.5,以及Hotfix_SPB16.50.003以上版本。

1.1 FSP相关功能

自动分配管脚(根据布局位置,自动优化)

自动IO管脚综合(最少的走线交叉)

原理图符号自动生成(支持capture和Design Entry HDL原理图符号)

原理图自动生成(支持capture和Design Entry HDL两个原理图工具)

电源管脚,信号自动连接支持设计更改(PCB设计布局、管脚分配信息等更改迒回FSP软件)