Vivado HLS是将基于C/C++描述的算法转化成相应的RTL代码,最终在FPGA上实现。这就要求软件工程师对FPGA的内部架构有一些基本的认识,目的在于保证生成的RTL代码在性能和资源上能够达到很好的平衡。实际上,C语言与FPGA是有一些对应关系的。比如:

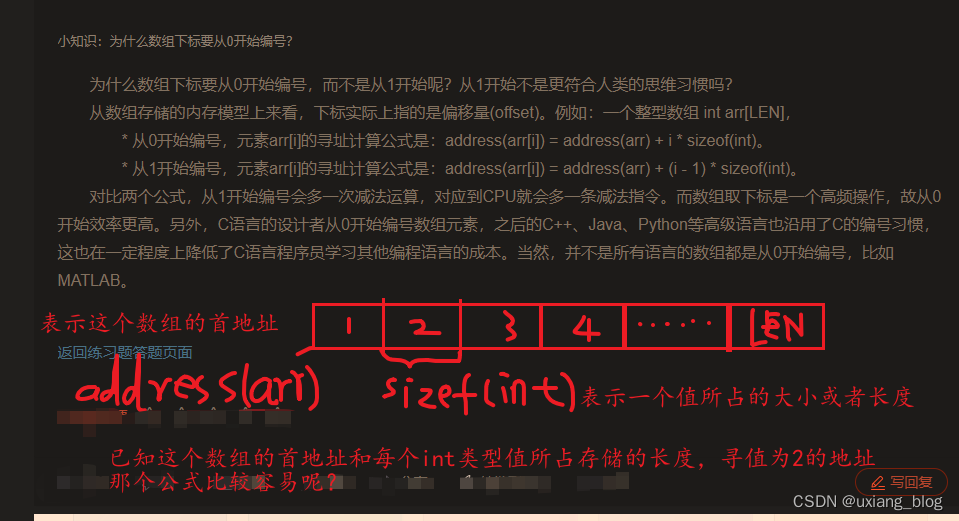

C语言中的数组可对应于FPGA中的寄存器、分布式RAM、Block RAM或者UltraRAM

C语言中的乘加运算可对应于FPGA中的乘加运算单元(DSP48)

但不同于硬件工程师,对于FPGA内部其他资源比如高速收发器等,软件工程师可不必了解。

本讲从软件工程师的视角重点介绍FPGA内部常规逻辑单元,包括查找表(LUT)、乘加运算单元(DSP48)、存储单元(Block RAM)。这三类资源在算法开发中或多或少都会用到,在Vivado HLS的综合报告中也有所体现。

1. VIVADO HLS的设计流程

2. C/C++表述算法时的代码风格

3.FOR循环的优化方法

4.数组的优化方法

5.I/O端口的实现方式

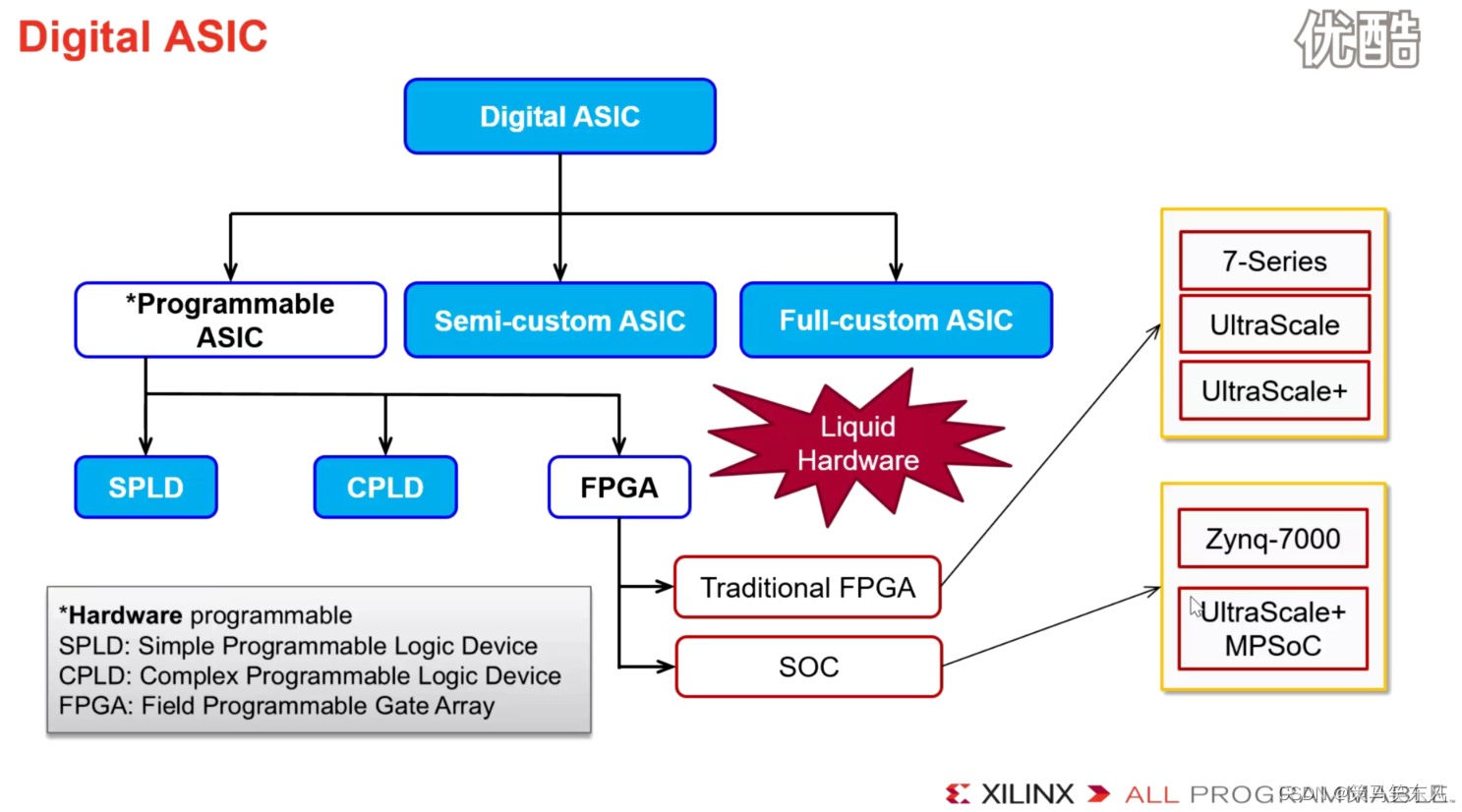

FPGA包括传统FPGA,其中包括7-series ,UltraScale,Ult

![[Hadoop]MapReduce与YARN](https://img-blog.csdnimg.cn/3e30448c90074f74b9ee4196accc5b10.png)