3.1

引言

采集卡的硬件设计是实现采集功能的基础,良好的硬件设计可以使采集功能更容

易实现,方便软件开发。本章基于第二章的硬件设计方案来详细介绍采集卡硬件设计。

包括载卡和子卡的芯片的选型、配置和具体电路的设计。载卡和子卡的硬件设计总体

框图如图

3.1

所示

3.2

载卡硬件设计

3.2.1

主控芯片选型及配置电路

(

1

)主控芯片选型及分析

根据第二章采集卡硬件设计分析结果,控制芯片需满足以下条件:

芯片包含高速

GTX

接口,不少于

12

对,其中光纤

4

对,

PCIE8

对;

片内具有足够的

BRAM

资源,用作

FIFO

接口;

芯片支持

Aurora

及

PCIE2.0

协议;

芯片具有外设接口,方便调试,可移植性好。

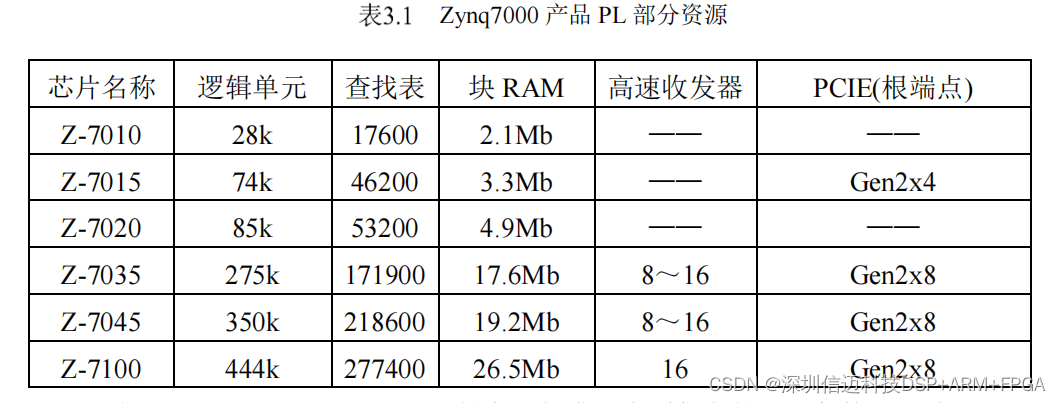

综合以上需求,主控芯片选择

Xlinx

公司

Zynq7000

系列

SoC

,该产品分类及

PL

部分的资源如表

3.1

所示

[23]

。

由表

3.1

可知,

Zynq-7135

以下的产品能满足本采集卡的设计条件,通过对比分

析,选择

Zynq-7100

系列型号为

XC7Z100FFG900-2

的芯片,该芯片内部包含以双

ARM Cortex-A9

为核心的

PS

部分和以

Xilinx Kintex7

系列

FPGA

为核心的

PL

部分。

该芯片的

IOBANK

分布如图

3.2

所示:

图

3.2

中方块里的数字代表引脚所在的

bank

位置,白色方块是电源、接地或者

配置引脚。其中

bank9

~

bank13,bank33

~

bank35

是

PL

部分的

IO

引脚;

bank109

~

bank112

是

PL

部分的高速

GTX

接口,每个

bank

提供四组高速差分收发器;

bank500

~

502

是

PS

部分的引脚,

PS

部分提供常见的接口,例如以太网、

SPI

总线、

CAN

总线、

Uart

接口等。

(

2

)主控芯片的电源配置电路

Zynq7100FFG900

的

PL

和

PS

部分根据

bank

性能和实际需要接入不同的

IO

驱

动电压。

PL

部分需要内核电源、辅助电源、高速

GTX

接口内核电源和高速

GTX

终

端电源。

PL

部分的

BANK

分为

HR(High Range)

和

HP(High Performance)

,

HR

部分电

压范围在

1.2V

~

3.3V

之间,而

HP

部分支持电压范围在

1.2V

~

1.8V

之间。对于

Zynq7100FFG900

,它的

HR

部分为

bank9

~

bank13

,

HP

部分为

bank33

~

bank35

。

PS

部分需要内部电压、辅助电压、

MIO

电压等。其中

PL

部分和

PS

部分供电电压如表

3.2

所示。

(

3

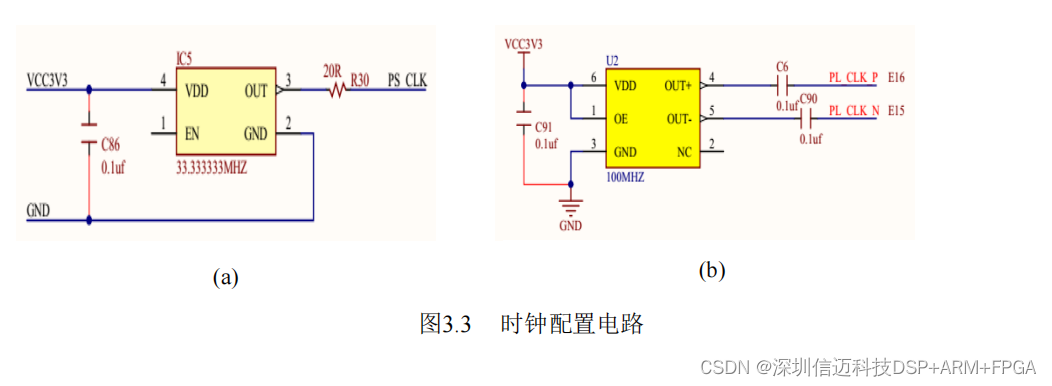

)主控芯片的时钟配置电路

时钟配置电路是

Zynq7000

系列另一种重要的配置电路,所有的时序和命令都是

以外接时钟为基准。若时钟漂移很大,会影响整个系统的性能,甚至出现不工作的现

象。一般用有源晶振作为时钟源。

Zynq7000

系列芯片的时钟有三种,分别为

PL

部分

时钟、

PS

部分时钟和高速

GTX

接口时钟。本采集卡的

PS

部分的时钟由

33.333333MHz

的有源晶振提供,该晶振输出为单端信号;

PL

部分的时钟由

100MHz

的有源晶振提

供,该晶振以差分信号的形式输出。

PS

和

PL

的时钟电路图如图

3.3

所示,其中图(

a

) 是 PS

的时钟,图(

b

)是

PL

的时钟。

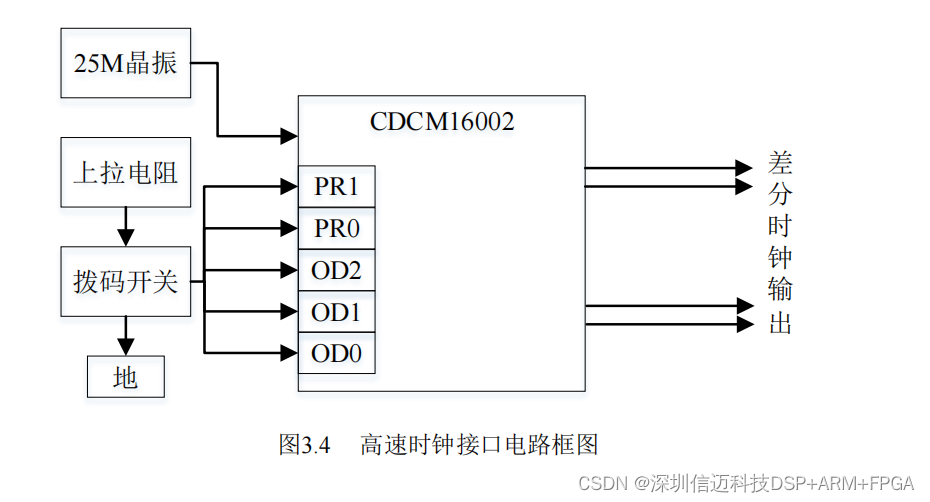

由于高速数据传输协议多种多样,速率不尽相同,因此实际应用时,需根据具体

协议和传输速率确定高速时钟的频率。本采集卡采用

TI

公司的

CDCM61002

可编程

时钟芯片,该时钟芯片输入时钟信号是单端的,输入信号频率范围为

21.875

~

28.57MHz

;片内有高性能

VCO

,工作频率为

1.75GHz

~

2.05GHz

;输出可

1

,

2

,

3

,

4

,

6

,

8

分频;提供两对差分输出时钟,支持

LVCMOS

电平和

LVDS

电平。

本设计中为该时钟芯片接入

25MHz

的时钟信号,采用拨码开关来给芯片引脚输

入不同的电平,进而控制输出频率,输出频率范围为

62.5MHz

~

625MHz

。能满足大

多数高速数据传输需求。

高速时钟配置电路框图如图

3.4

所示。

拨码开关配置及输出时钟频率如表 3.3 所示。

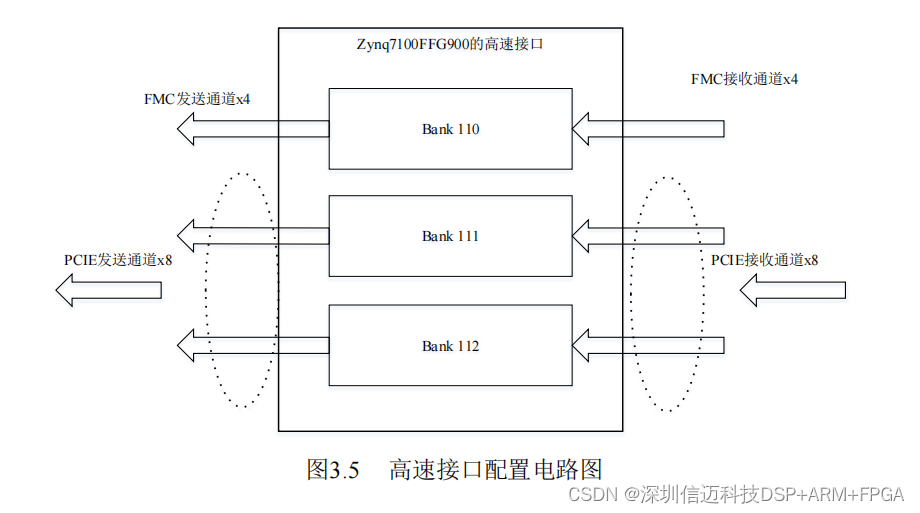

(

4

)主控芯片的高速接口电路

Zynq7100FFG900

的高速数据接口有

16

对,采集卡一共用到了

12

对,其中

FMC

接口

4

对,

PCIE8

对。其中

bank110

是

FMC

接口,

bank111

和

bank112

是

PCIE

接口。

Zynq7100FFG900

的高速接口框图如图

3.5

所示:

(

5

)主控芯片的外围配置及电路

Zynq7000 SoC 芯片掉电之后程序会丢失,需要把程序保存在掉电不容易丢失的

存储介质里,一般程序和系统从

SD

卡或

QSPI FLASH

启动。另外程序和系统还可用

以太网口用来远程控制和更新。本设计用两片

FLASH

、一个

SD

卡接口、一片

EMMC

作为程序固化和系统移植的载体,同时设备需要一个以太网口实现远程操作。

Zynq7000SoC

芯片的

PS

提供

SD

卡、

QSPI FLASH

接口和以太网接口,

EMMC

连接

到

PL

部分,实际应用时,调用

EMIO

功能实现

EMMC

的读写操作。

采集卡使用两片

QSPI FLASH

芯片,作为保存程序或系统的介质。芯片连接在

PS

的

bank500

,

QSPI FLASH

采用

CYPRESS

公司型号为

S25FL256S

,该芯片存储容

量为

256Mb

,读写时钟最高可达

133MHz

。

QSPI FLASH

连接框图如图

3.6

所示。

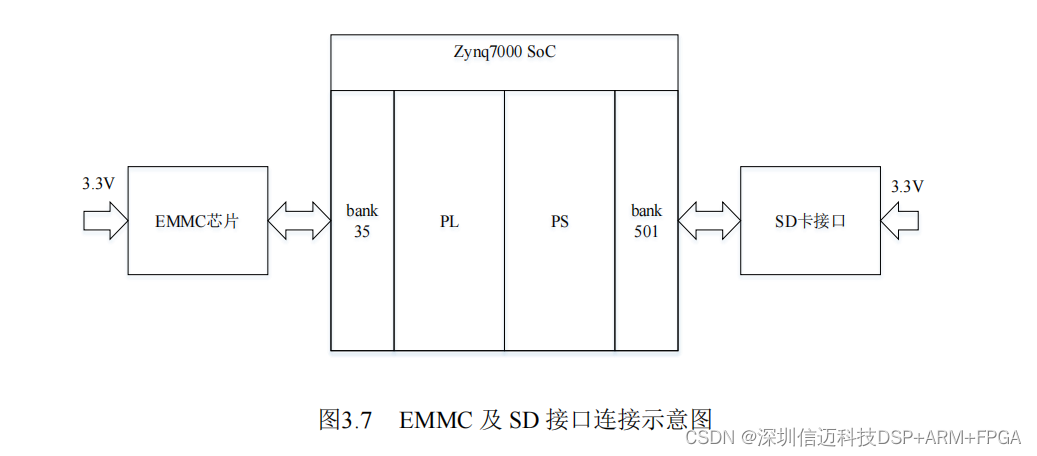

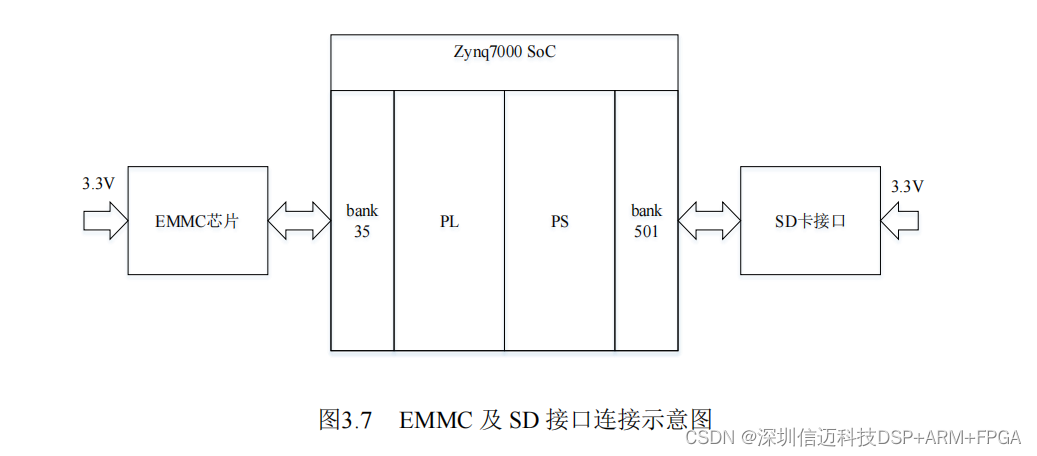

SD

卡接口是用来保存程序或系统的,

SD

卡接口接在了

bank501

,

EMMC

用来作

为数据存储或保存文件系统,采集卡使用

Micron

公司型号为

MTFC8GAKAJCN-4M

的

EMMC

,该芯片具有

8GB

的容量,读写时钟可达

50MHz

,

EMMC

芯片接在了

PL

部分的

bank35

上。

芯片和

SD

卡接口连接示意图如图

3.7

所示。

以太网接口使用通用的 RJ45 接口,以太网驱动芯片选择 MARVELL 公司型号为

88E1518

,该芯片适用于

10/100/1000

兆网的接口驱动芯片,以太网驱动接在了

PS

部

分的

bank501

,网口电路和驱动芯片电路连接框图如图 3.8 所示。

3.2.2

DDR3 SDRAM

选型及配置电路

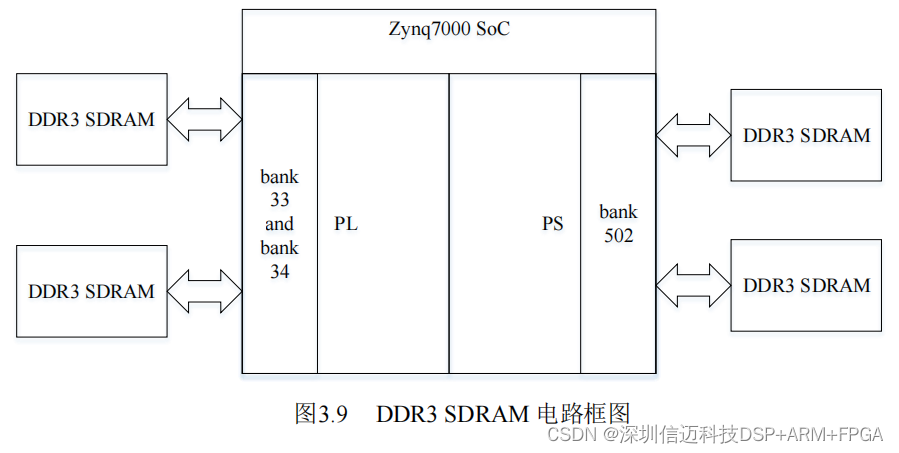

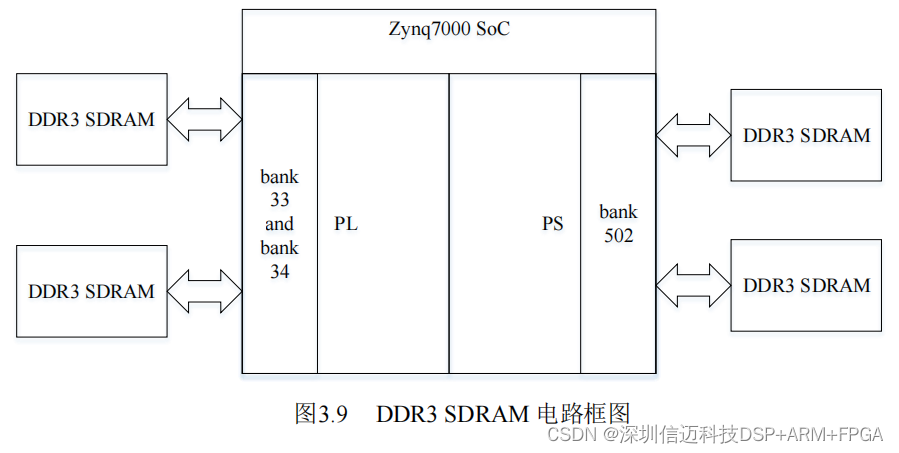

Zynq

芯片的

PS

部分和

PL

部分需要接入

DDR3 SDRAM

,

PS

部分

DDR3 SDRAM

的作用是在系统启动和系统运行时提供数据暂存,

PL

部分

DDR3 SDRAM

主要用来

作为高速数据缓存。采集卡的

DDR3

芯片采用镁光公司型号为

MT41K256M16TW-

107

的

DDR3 SDRAM

,其中

PL

部分和

PS

部分各接入

2

片内存颗粒,单芯片数据位

宽为

16bit

,两片芯片数据位宽为

32bit

,总容量为

1GB

。其中

PS

端内存主频可达

1066MHz

,

PL

端内存主频可达

1600MHz

。

PL

部分的

DDR3 SDRAM

接在了

bank33

和

bank34

,这两个

bank

属于

HP

部分,

能将

DDR3 SDRAM

的性能更好的发挥出来,

PS

部分的

DDR3 SDRAM

接在了

PS

部

分的

bank502

,该

bank

是专用来给

DDR3 SDRAM

提供接口,

PL

部分和

PS

部分的

DDR3 SDRAM

电路框图如图

3.9

所示。

3.2.3

高速接口电路

采集卡的高速接口有

FMC

接口和

PCIE

接口,一般在高速差分信号引脚处接入

0.1uF

的电容,起隔离直流信号的作用。在布线时,单通道差分线采用相邻平行走线,

尽量减少不同层之间的过孔,以获得更高传输速率;不同通道差分线要等长设计,以

满足同步需求。

FMC

接口中文叫做

FPGA

中间层板卡接口,是连接子卡和载卡的连接通道,通

常子卡上采用公座,载卡上使用母座。

FMC

接口支持最大

10Gbps

的传输速率,潜在

传输速率在

40Gbps

。

FMC

接口有两种,一种是具有

160

引脚的

LPC

连接器,另外一

种是

400

引脚的

HPC

连接器

[24]

,

FMC

接口额外提供一组串行收发器、

JTAG

接口和

I

2

C

接口,还可提供不同的电源专用引脚供子卡的器件供电。子卡的设计可以脱离

FPGA IO

引脚的约束,只需要

FMC

引脚对应即可,使设计更具有灵活性。

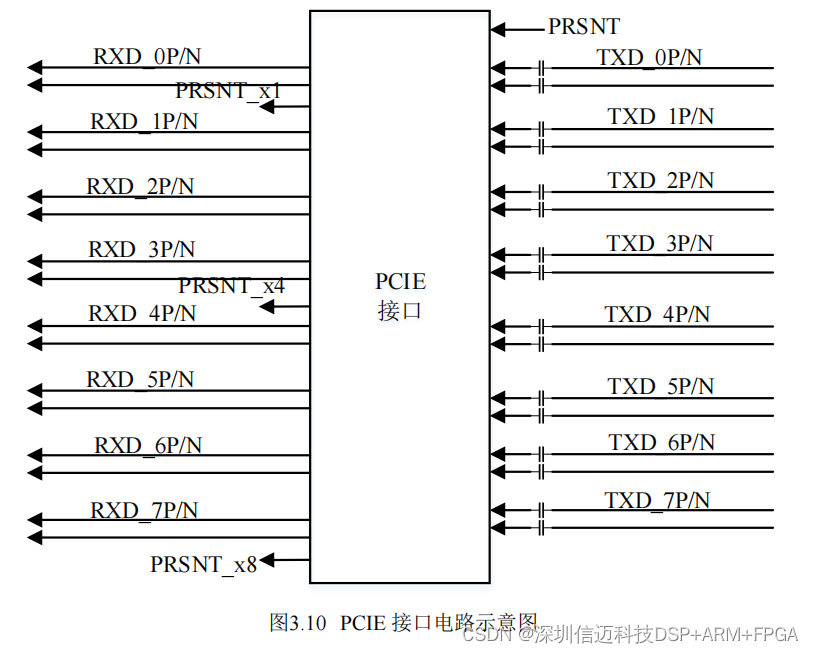

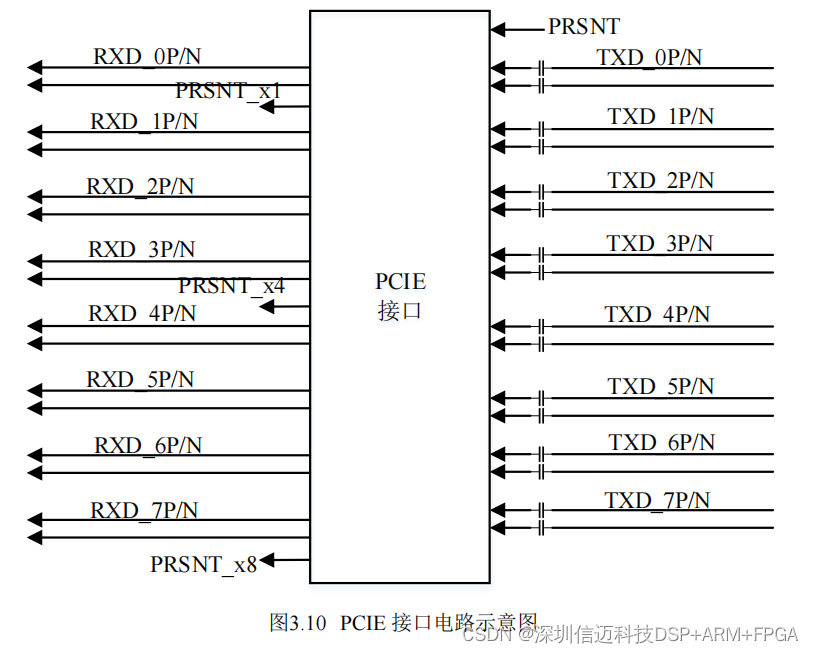

PCIE

接口电路示意图如图

3.10

所示,图中箭头代表数据方向,

RXD

是接收引

脚,用来从

PC

机接收数据,

TXD

代表发送引脚,作用是发送数据至

PC

机,在

TXD

的差分信号端需要接入

0.1uF

的电容。

PCIE

接口可以选择

X1

,

X2

,

X8

模式,只需

要把相应的

PRSNT_xx

脚连接至

PCIE_PG

脚即可。本设计采用

X8

模式,需要把

PRSNT_x8

脚与

PRSNT

引脚连在一块。

PCIE

采用金手指接口,能直接与

PC

机连接。

3.2.4

电源电路

电源是采集板的另外一部分重要的部分,良好的电源可以使板子工作正常,否则

电源纹波过大,会影响板子的性能,使板子不工作和功耗过大,甚至导致板子的损坏。

由于

PC

机主板的电压为

12V

,主板供给

PCIE

接口供电电压也为

12V

。为了兼容

PC

机,本采集卡采用

12V

直流电源供电,再由电源管理芯片转换成其他电压,供不同的

芯片使用。

在给设备芯片供电时,电源管理芯片不能工作在满负荷或者超负荷状态,否则输

出电压不稳定,影响整体的工作性能。

Zynq7000SoC

是低功耗设计,输出电流在几个

安培就可以满足供电需求。采集卡采用核心板

+

底板的结构,而主控芯片位于核心板。

考虑到核心板使用电压种类较多,如果

12V

在底板上完成电源转换再连接至核心板,

一方面会导致底板电路设计复杂,另一方面核心板的电源只能由底板提供,核心板不

能单独开发,失去了设计的灵活性。如果电源在核心板上转换,虽然电路复杂,但是

可以很好的移植其他底板上,使设计更灵活。

底板上有

USB

、以太网和

FMC

接口,供扩展功能和连接子卡,这些接口需要额

外的供电,因此在底板上需要做一下简单的电源转换,框图如图 3.11 所示。

底板的电源管理芯片选择

TI

的

芯片,该芯片输入电压范围为

~

18V

,输出电压范围在

~

7V

之间可编程。最大电流输出为

3A

,能满足大多数

设备开发需求。

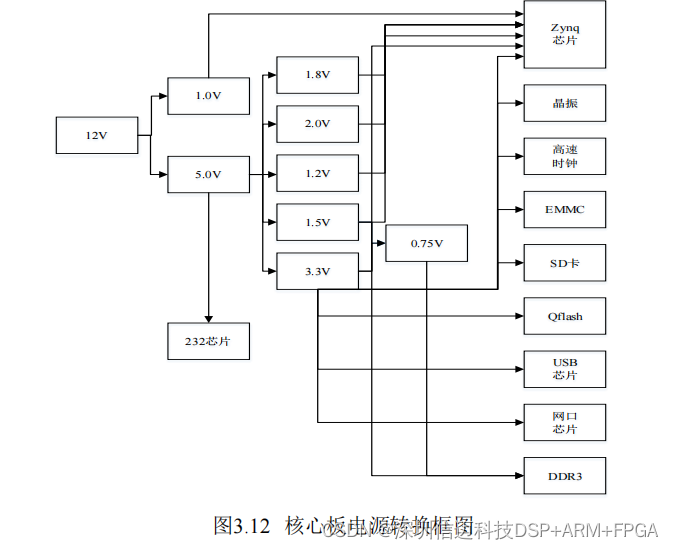

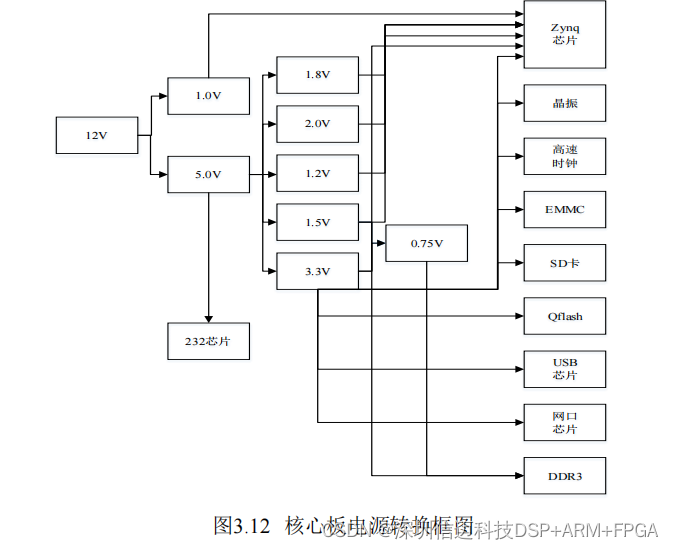

核心板需要

0.75V

,

1.0V

,

1.5V

,

1.8V

,

2.0V

,

3.3V

,

5.0V

等不同的电压,供

主控芯片、

DDR3

芯片和其他外设使用。根据实际选用不同的电源管理芯片,电源转

换框图如图

3.12

所示,用箭头表示电压转换。

在核心板电源设计中,采用 TI 公司的 TPS53355 作为 12V 转 1V 的电源管理芯

片,该芯片需要外部提供转换电压和电源电压。其中转换电压输入范围为

1.5V

~

15V

,

电源电压输入范围为

4.5V

~

25V

,芯片输出电压范围为

~

5.5V

,最大电流可达

30A

;

12V

转

芯片采用

TI

公司的

。该芯片电压输入范围为

~

18V

,

输出电压范围为

0.76V

~

,输出电流可达

6A

;其余由

5V

转至其他电压的芯片

选用

MPS

公司的

MP2143

,该芯片输入电压范围为

2.5V

~

5.5V

,输出电压为

0.6V

~

Vin-0.5V

,其中

Vin

是芯片的供电电压,芯片电流输出能力达到

3A

。经分析验证,芯

片能满足实际开发需求。

3.3

子卡的电路设计

3.3.1

AD

子卡的电路设计

AD

子卡完成模拟信号的数字转换,并通过

FMC

接口发送至采集卡的

Zynq

芯

片。

ADC

芯片采用

TI

公司的型号为

ADC12D800

芯片,该芯片最大采样率为

1.6Gbps

,

分辨率为

12bit

。转换结果根据芯片的配置,能以

12

组差分对的形式输出,也可以分

别作为数据线并行输出。该

ADC

芯片支持两通道的数据转换,分别为

I

通道和

Q

通

道,每个通道有独立的数据线,芯片支持单边沿采样和双边沿采样,通过时钟和控制

接口来控制芯片的工作模式。

芯片的时钟和控制接口及功能如表

3.5

所示。

芯片还配有

SPI

总线接口,在

ADC

芯片工作在延伸控制模式时,

SPI

接口可以

用来对

ADC

进行配置,完成偏置、校准等功能。由于本次设计没有涉及到

SPI

总线,

因此这里不在对

SPI

的配置方式和寄存器功能进行赘述。

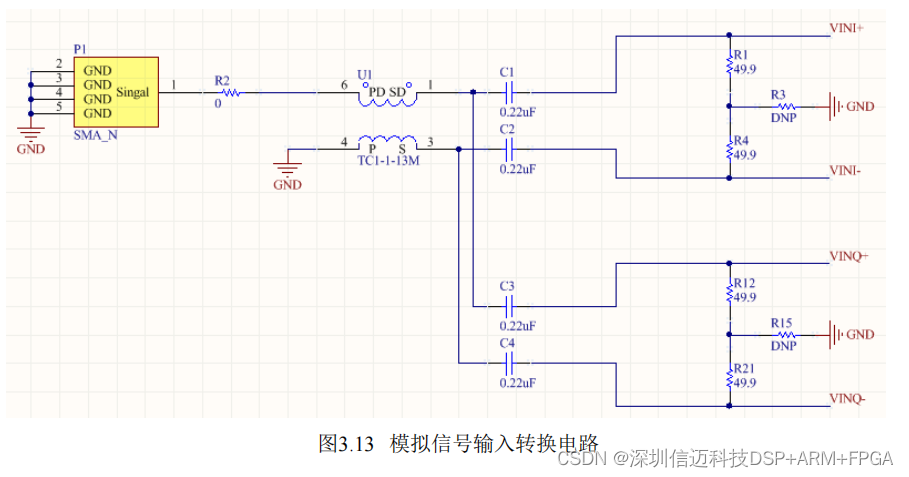

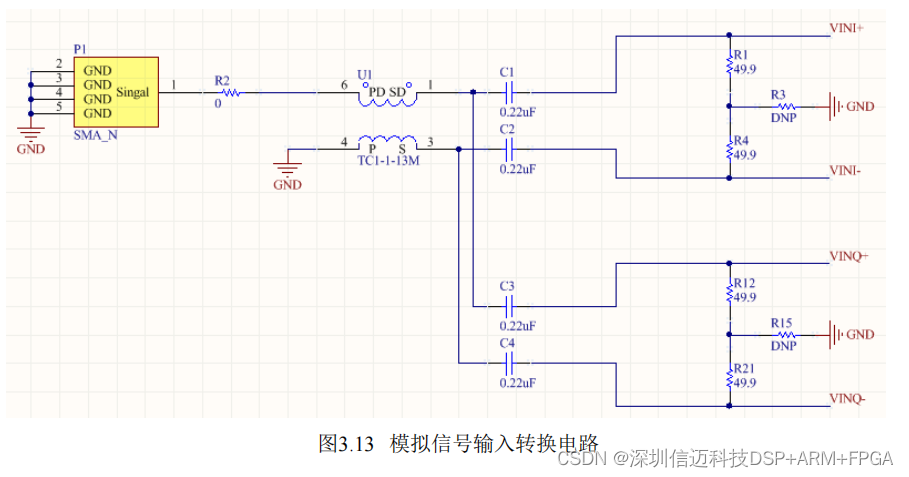

ADC

芯片电压采用差分输入的形式,本次设计为模拟信号以交流耦合的方式进

入

ADC

芯片,模拟信号经过

SMB

射频接口后,经电路转换为两路差分信号进入

ADC

芯片。电路图如图

3.13

所示。

根据

ADC

芯片手册,该

ADC

芯片工作电压最大为

2.2V

,本次子卡设计中电源

采用

1.9V

供电,由

FMC

接口引入

3.3V

的电压,经电源管理芯片转换为

,供

芯片使用。采用

TI

公司的型号为

LP38503-ADJ

作为

3.3V

到

1.9V

的电源转换,

该芯片供电范围为

2.7V-

,输出电压范围为

-5.0V

,输出最大电流为

。能

满足

ADC

工作需求。

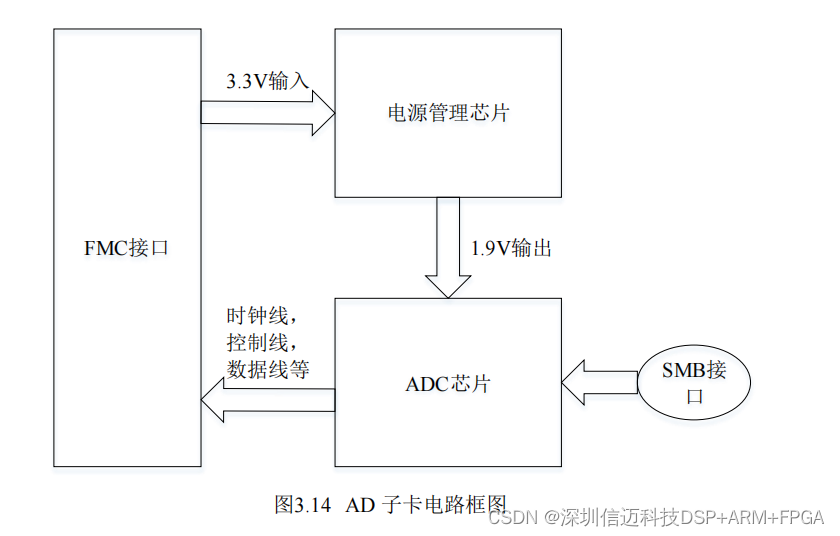

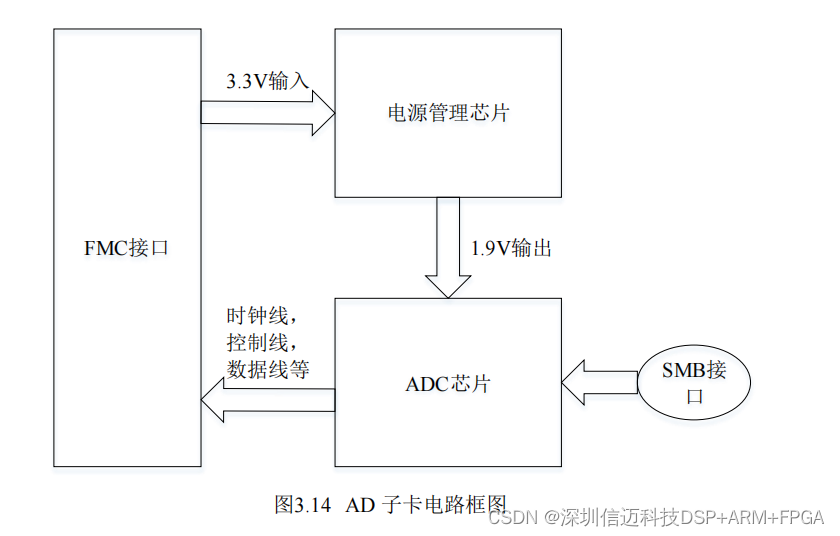

将

AD

芯片的控制线、数据线等引出至

FMC

接口,在电路设计时,数据线要等

长布线,以满足同步需求。综上所述,

AD

子卡的电路框图如图

3.14

所示。

3.3.2

光纤子卡的电路设计

光纤子卡完成了光纤接口到

FMC

接口的转接,光纤接口采用

1761987-9

的

QSFP

接口,该接口提供

4

路高速差分接口,通常搭配光纤接口使用,接口提供了一种小型

化和高速传输的解决方案。

本次设计采用的光纤接口型号为

SR4-40G

的光纤插头,该接头提供

40Gbps

的传

输速率,传输距离可达

150m

。光纤接口需要

3.3V

供电,电源由采集卡的

FMC

接口

提供。并将

4

对高速差分线引至

FMC

接口,光纤子卡的框图如图

3.15

所示。

本章完成了载卡和子卡的硬件设计。在载卡的硬件设计中,首先根据不同

Zynq7000SoC

芯片的资源选择合适的主控芯片,并对主控芯片的外围电路进行配置;

然后是

DDR3 SDRAM

芯片的选型配置;接下来是高速接口选择,对

FMC

接口和

PCIE

接口进行详细介绍;最后是载卡电源电路的设计,根据芯片不同的电压需求产

生相应的电压,保证功率满足设计要求;子卡的硬件设计主要对

AD

子卡和光纤子卡

进行详细的设计和分析,在

AD

子卡设计中,介绍了

ADC

芯片的选型和配置,以及

电路设计。在光纤子卡设计中,主要对光纤接口进行选择和电路设计分析。

5.6

采集卡数据采集传输测试分析

上位机起着控制数据传输和存储的功能,要保证速率的同时,还要降低数据误码

率。本节将基于辐射源识别项目的指标进行数据速率的测试和误码的测试。本次测试

首先用外部光纤接口的递增码来模拟数据的传输,测试速率和准确性,以保证满足辐

射源信号项目的要求,然后进行

ADC

的采样测试。

5.6.1

光纤子卡的测试分析

光纤子卡实物图如图

5.16

所示。子卡实现光纤接口至

FMC

接口的转换,光纤接

口提供

4

通道的高速差分对,连接至

FMC

接口。

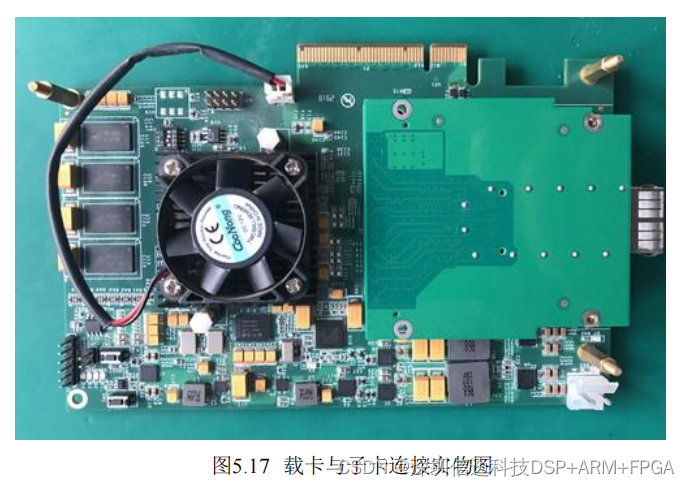

光纤子卡与载卡连接实物图如图 5.17 所示。

把光纤子卡连接至光纤数据源,将数据卡接入

PC

机,以便进行光纤测试,采用

另一块光纤接口卡作为光纤数据数据源,测试环境如图

5.18

所示。