在本实验中,将学习为设计创建约束的两种方法。将使用Vivado2019.2 IDE中包含的Kintex®-7 CPU网表示例设计。

步骤1:打开示例项目

1.打开Vivado IDE。

Vivado IDE的“Getting Started page”包含打开或创建项目以及查看文档的链接。

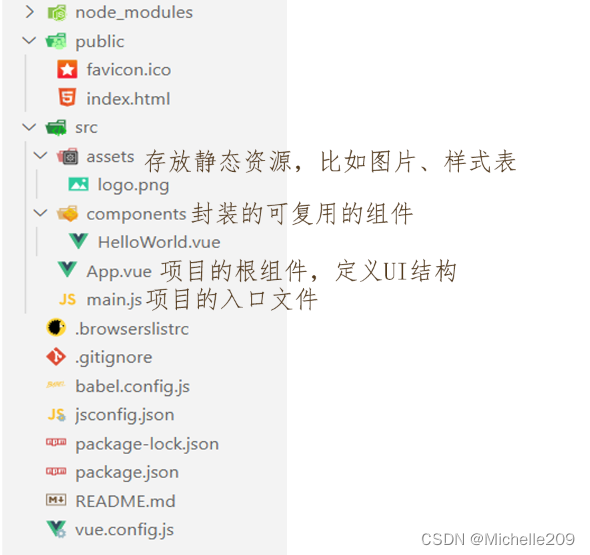

2.在“Getting Started page”页面中,单击“ Open Example Project”,如下图所示。

实验1:定义时序约束和例外

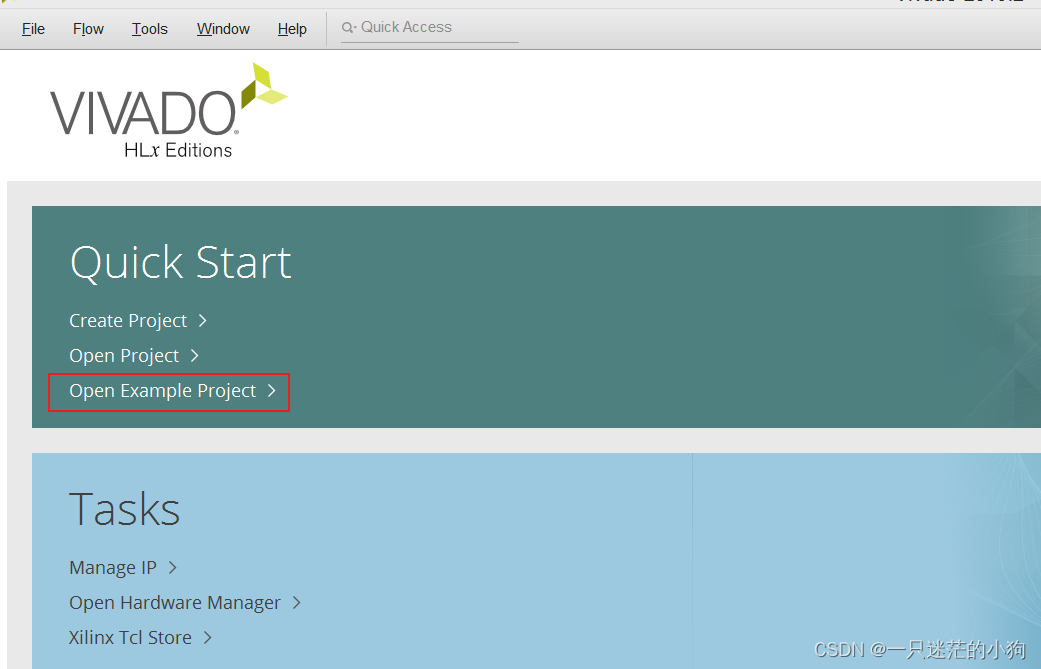

打开示例项目向导将打开“Create an Example Project”页面,如下图所示。

3. 点击“Next”。

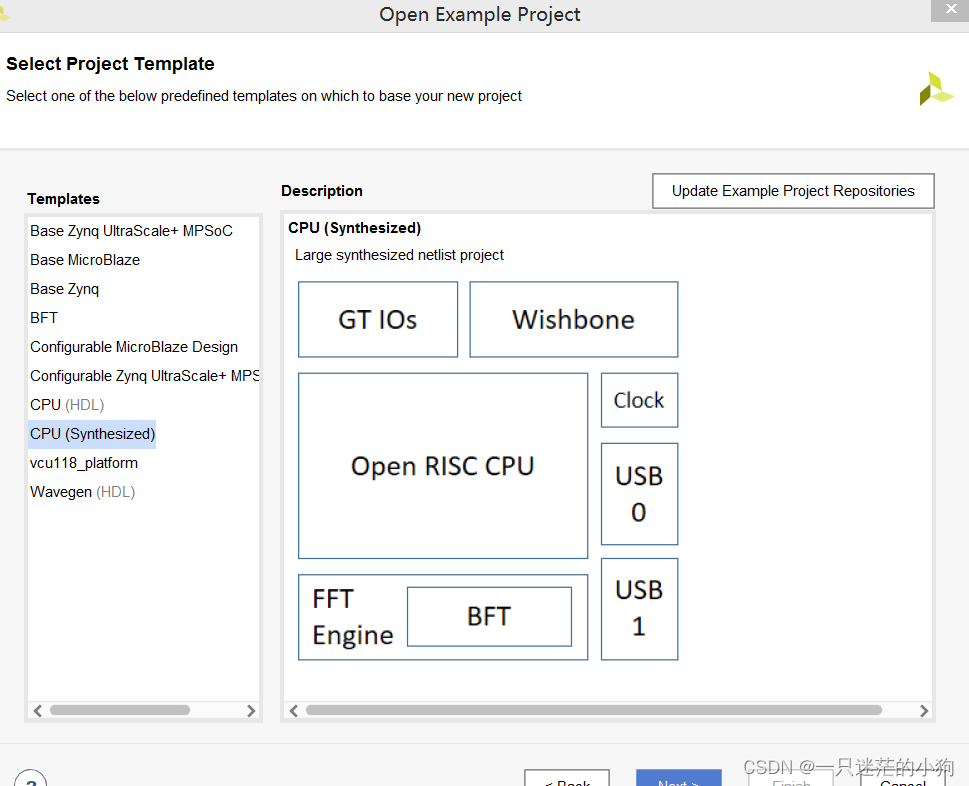

4. 在“Select Project Template”页面, 选择“CPU (Synthesized)”,如下图所示 。

5.单击“ Next”。

6.在“ Project Name”页面中,指定项目名称和位置,如下图所示。

7. 单击“ Next”。

8. 在“Default Part ”页面中,选择Default Part ,如下图所示。

Step 2: Defining Constraint Sets and Files(定义约束集合和文件)

首先创建一个新的约束集,并向其中添加一个空的XDC约束文件。

示例设计已经包含两个约束集,但您不在此实验室中使用它们。

1.在“ Flow Navigator”中,单击“Project Manager ”部分中的“Add Sources”。

2.从“Add Sources”对话框中,选择“Add”或“create constraints”。

3.单击“Next”。

4.从“ Add or Create Constraints ”对话框中,使用“Specify Constraint Set ”下拉菜单选择“Create Constraint Set”,如下图所示。

5.在“Create Constraint Set”对话框中,将约束集名称指定为lab1,然后单击“OK”。

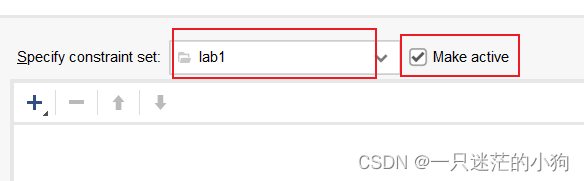

6.使能“ Make active ”复选框。

7.单击“Add”按钮,然后选择“Create File”将新的XDC文件添加到项目中。此时将显示“Create Constraints File”对话框。

8.键入timing作为文件名,并将文件位置设置为<Local to Project>。

9.单击“OK”。timing.xdc文件将添加到lab1约束集中。

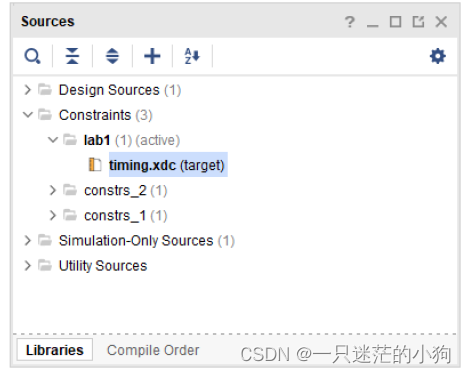

10.单击“Finish”以完成新约束集和XDC文件的创建。应该在Sources窗口中看到新的约束集和XDC文件,如下图所示。约束集将处于活动状态,正如在创建约束集时所指示的那样。

11.在“Sources”窗口(如下图所示)中,右键单击timing.xdc,然后选择“Set as Target Constraint File”。这将timing.xdc文件设置为目标xdc文件。添加到设计中的所有约束都保存在目标XDC文件中。

Step 3: Creating Timing Constraints(创建时序约束)

在此步骤中,您将打开综合设计并使用Vivado®时序约束向导。时序约束向导分析门级网表并查找缺少的约束。使用“ Timing Constraints wizard”可以为此设计生成约束。

1.在“ Flow Navigator”中,单击“Open Synthesized Design”。

2.当综合设计打开时,单击“Synthesized Design section”部分下的“Constraints Wizard”。此时将显示“Timing Constraints wizard ”向导的介绍页面。本页介绍向导创建的约束类型:时钟、输入和输出端口以及跨时钟域。

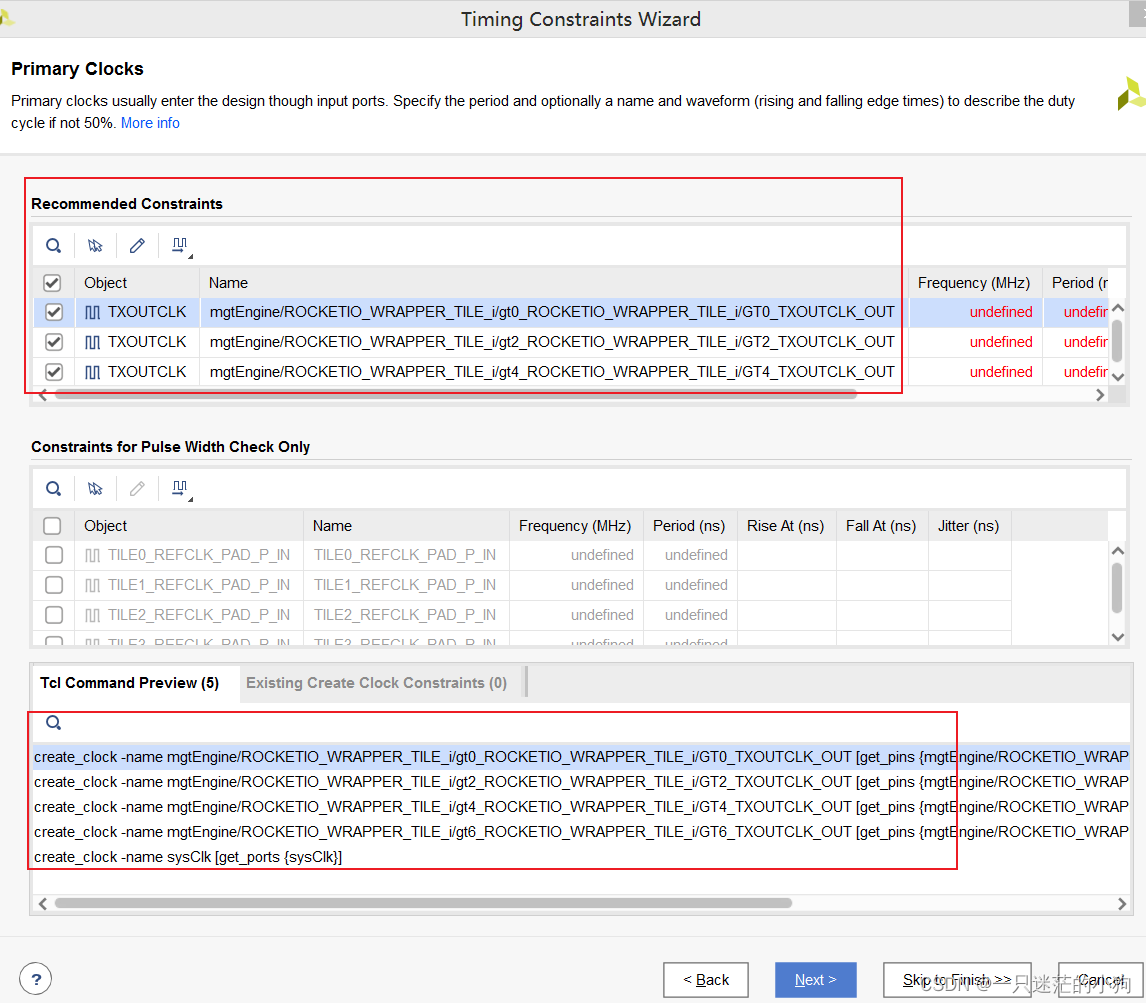

3.阅读页面后,单击“Next”继续。时序约束向导的“Primary Clocks”页面显示所有缺少时钟定义的时钟源。对于此设计,向导检测到为逻辑路径时序所需的五个缺失时钟约束,以及仅验证脉冲宽度和最小或最大周期要求所需的四个缺失时钟限制。

将在设计中填写五个缺失的主时钟的周期。第二类时钟是可选的,显示在“ Constraints for Pulse Width Check Only”表中。对于本例,请不要添加这些最后的约束。

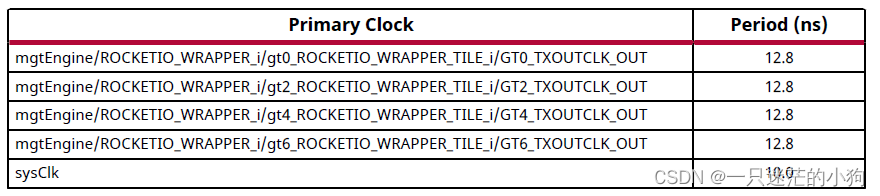

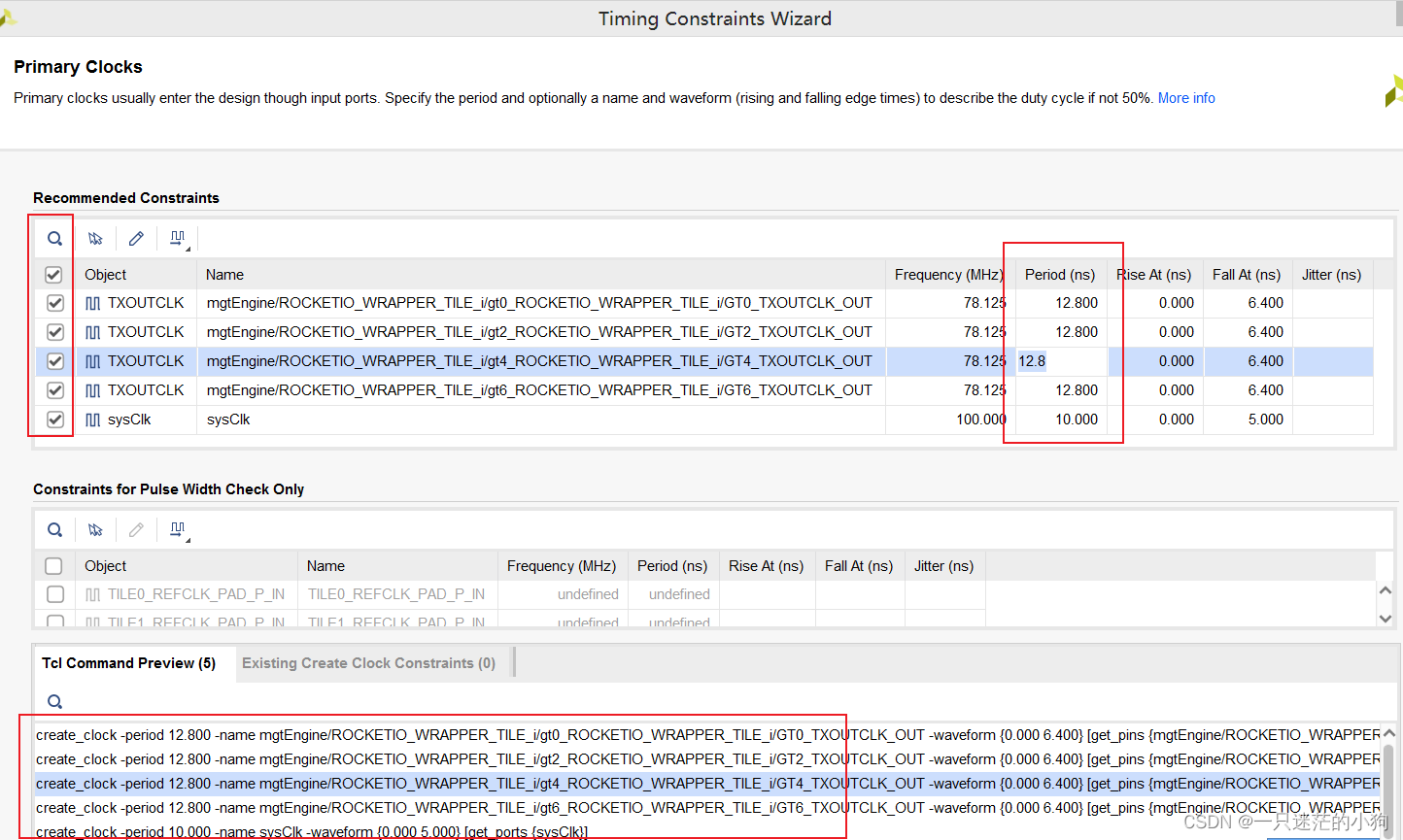

4.在“ Recommended Constraints”表中,向导的每一行都缺少一个约束。要在表中指定约束,请单击时钟周期列中的单元格,然后键入下表中的值,以填充设计中缺少的五个主时钟的周期。当您设置时钟的周期时,频率会自动填充。

表1:在向导的主时钟页面上使用的值

如果不想输入特定时钟的约束,请取消选中时钟旁边的框。有关向导如何查找这些缺失约束的详细信息,请单击向导左下角的“Quick Help”按钮(“?”)。快速帮助页面是特定于上下文的,包含有关向导正在查找的拓扑的更多信息,以及建议使用约束的原因的解释。完成的页面如下图所示。

5.单击“ Next”继续。

主要时钟约束已添加到设计中。接下来,向导将查找不受约束的生成时钟。生成的时钟源自FPGA结构中的主时钟。一个很好的例子是一个用于创建分频时钟的二进制计数器。在此设计中,向导确定不存在不受约束的生成时钟。

6.单击“Next”继续。

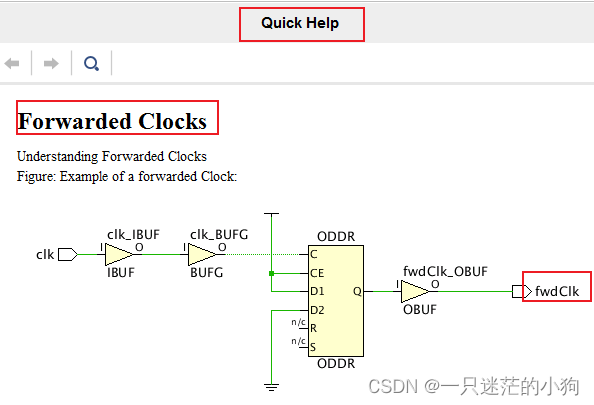

接下来,向导将查找forwarded clocks。forwarded clocks是在FPGA的主输出端口上生成的时钟。当捕获时钟与数据一起传输时,这些通常用于源同步总线。向导已确定设计中不存在不受约束的forwarded clocks。forwarded clocks(在“forwarded clocks”界面点击左下角的“?”)的定义如下图所示:

7.单击“Next”继续。

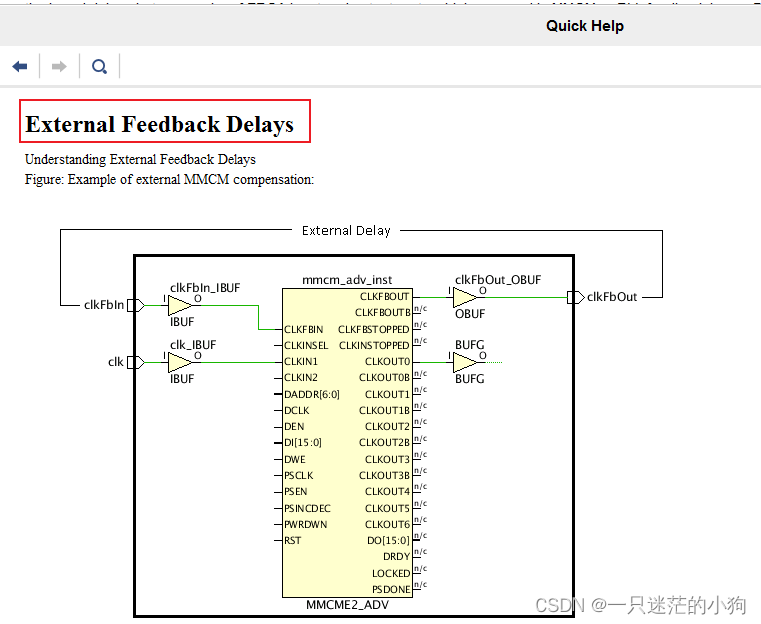

接下来,向导将查找外部反馈延迟。FPGA外部的MMCM或PLL反馈延迟用于计算时序报告中的时钟延迟补偿。向导在设计中未发现任何不受约束的MMCM外部反馈延迟。

8.单击“Next”继续。

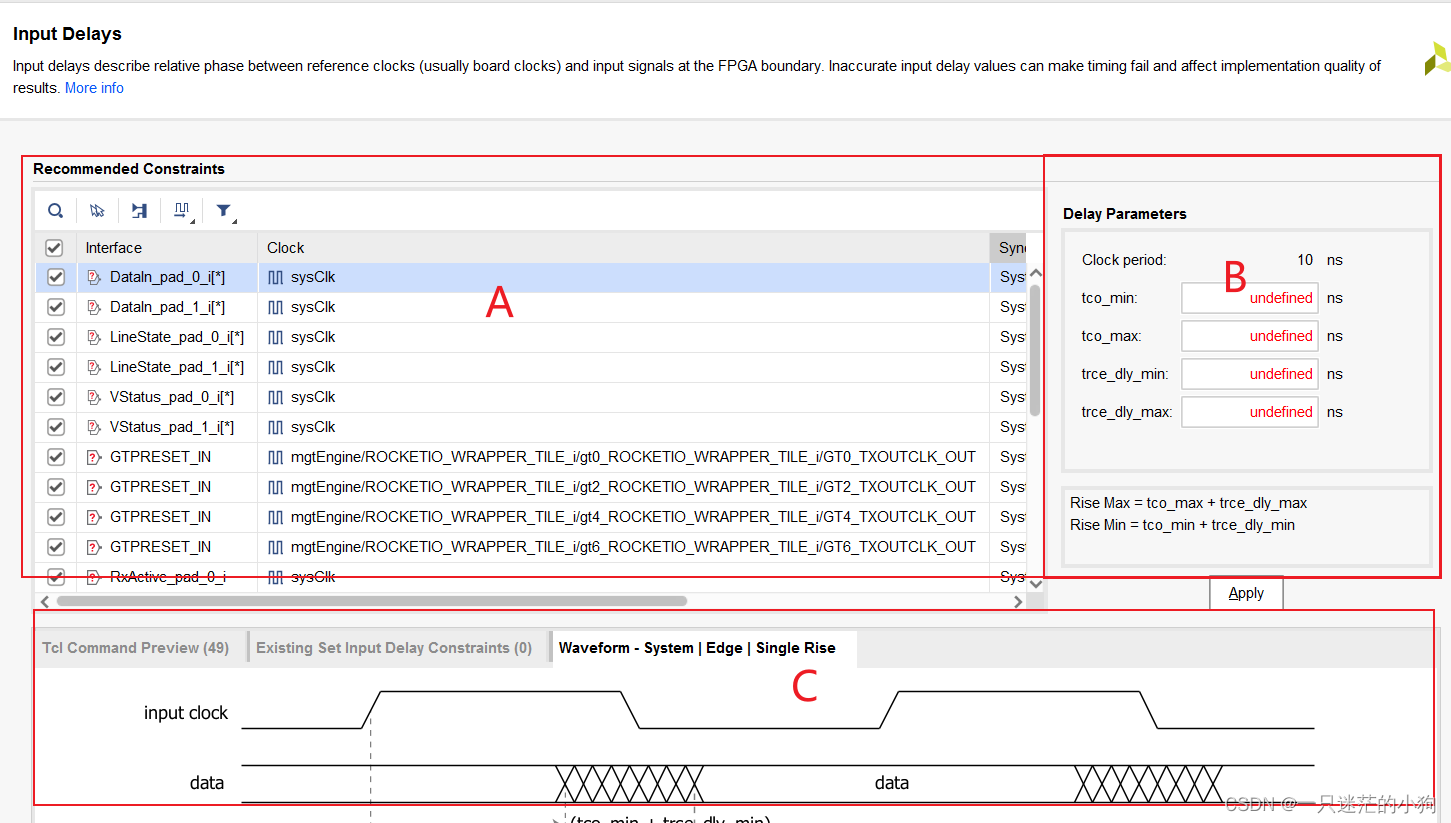

接下来,向导将查看输入延迟。下图显示了“Timing Constraints ”向导的“ Input Delay ”页面。这一页有三个部分。

在A部分中,您可以看到设计中缺少输入延迟约束的所有输入端口。在此表中,您可以选择要用于约束输入的时序模板。

在B部分中,您提供了模板的延迟值。本节将根据A节中选择的模板进行更改。

在C部分中,有三个选项卡:

•Tcl命令预览:预览将用于约束设计的Tcl命令。

• Existing Set Input Delay Constraints:显示设计中存在的输入延迟约束。

•Waveform:显示与模板关联的波形。

接下来,将根据下表填写表格。

9.单击 Clock column header,按时钟名称的字母顺序对表格进行排序。

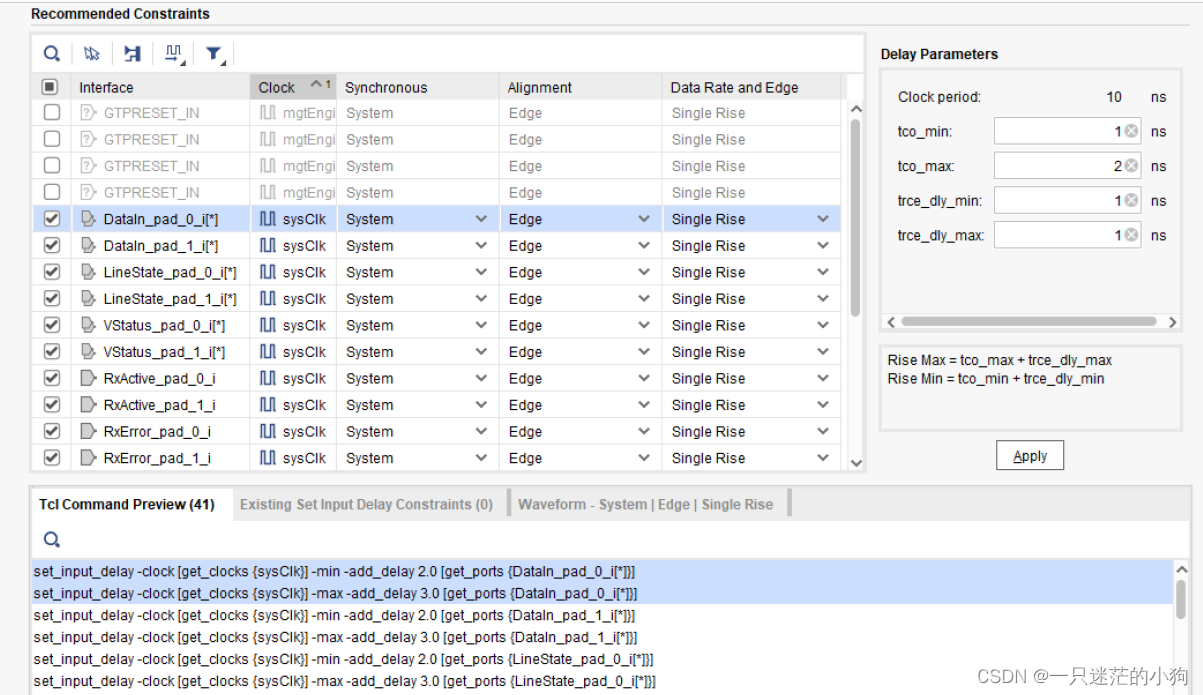

10.选择A部分中的模板,在B部分中输入值,并观察C部分中的Tcl命令、现有输入延迟和模板特定波形。

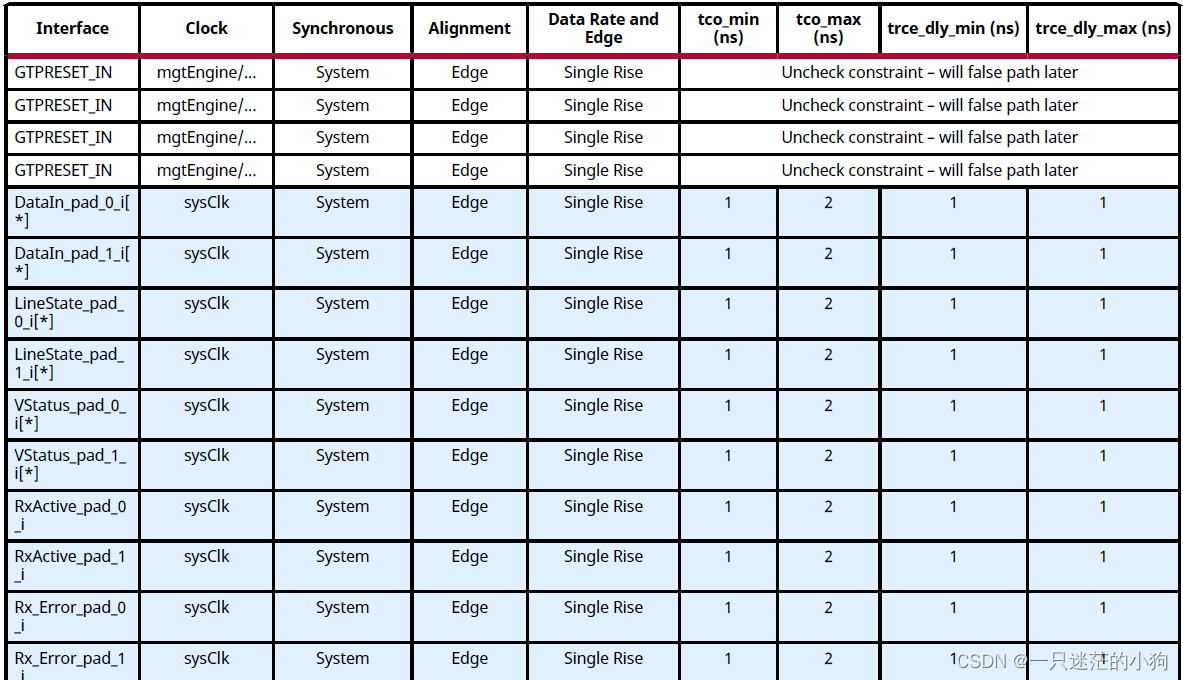

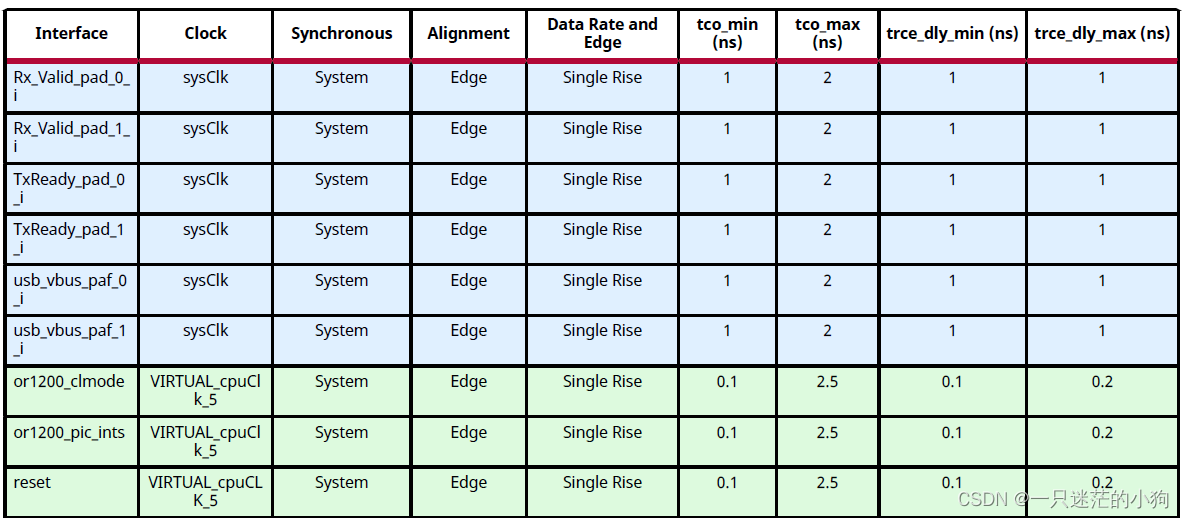

11.通过取消选中约束左侧的框,跳过输入下表中显示的前四个约束。在这种特殊情况下,您稍后会从GTPRESET_IN端口错误地路径这些路径,因为它是在设计内同步的异步复位信号。通过在向导中选择多行(使用Shift或Ctrl按钮并单击以选择多行),然后输入一次值,可以在时序约束向导的输入延迟页面中同时输入下表中的所有彩色行块,如下图所示。一些输入相对于虚拟时钟受到约束,因为它们被具有不同于主板时钟的波形的内部生成时钟捕获。在这种情况下,向导创建一个与内部时钟具有相同频率和波形的虚拟时钟,并建议相对于虚拟时钟的约束。下表带阴影,以指示可以以这种方式输入的信号组。

表2:输入约束值

下图显示了完成的输入延迟页面。请注意要跳过的四个约束。

12.成功输入所有输入约束值后,单击“Next”。

向导的“Output Delays”页面显示设计中不受约束的所有输出。页面布局与输入页面非常相似。

13.在Output Delays 页面中,单击时钟标题以按时钟名称的字母顺序对表格进行排序。

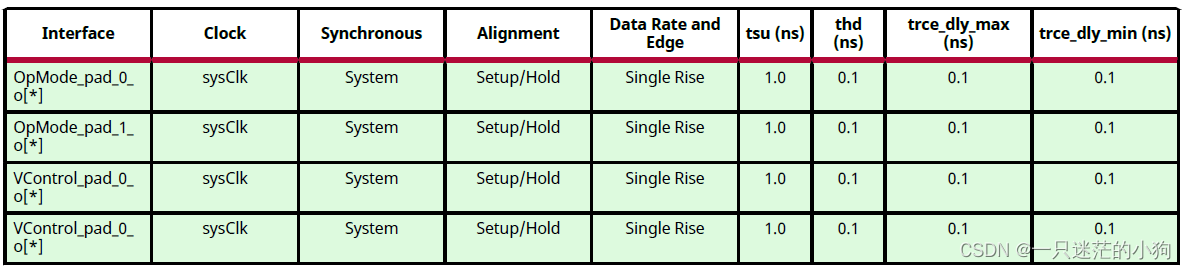

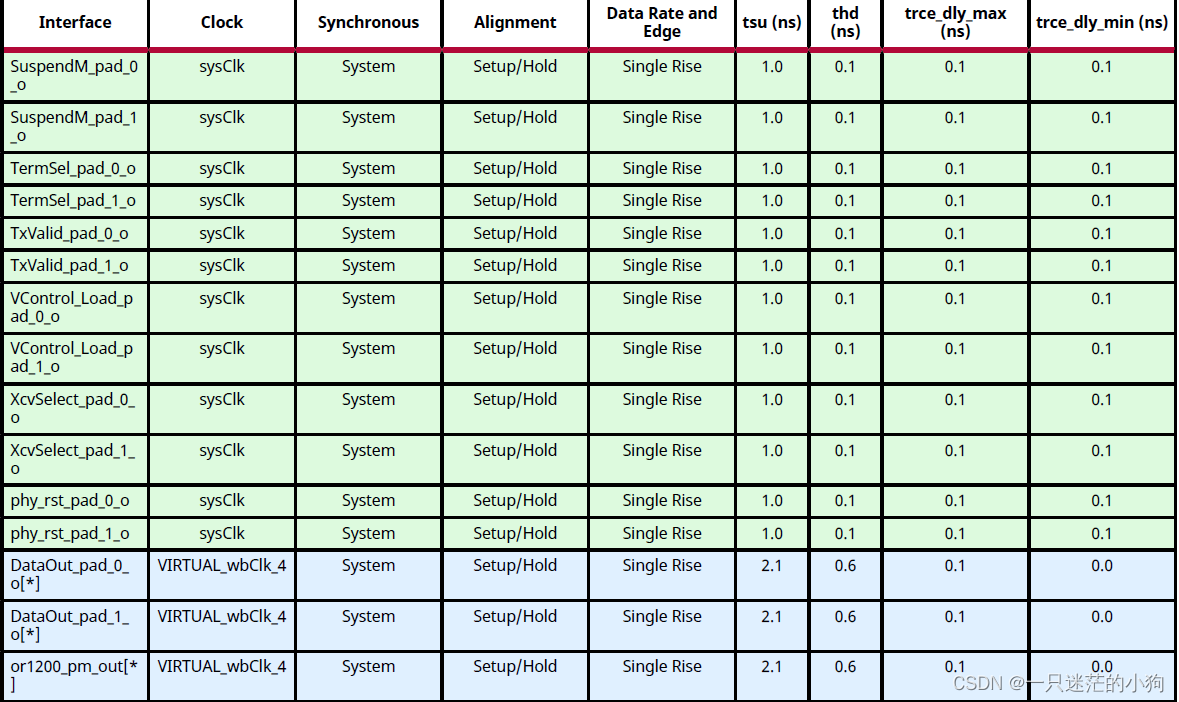

14.使用下表约束所有输出,就像对输入约束值所做的那样。可以在向导中一次选择多行,并同时编辑多个条目。

表3:输出约束值

15.单击“Next”继续。

向导将在设计中查找任何无约束的组合路径。组合路径是在不被任何序列元素捕获的情况下穿过FPGA的路径。该设计不包含任何组合路径。

16.单击“Next”继续。

物理独占时钟组是指设计中不同时存在的时钟。此设计中没有不受约束的物理独占时钟组。

17.单击“Next”继续。

没有交互的逻辑互斥时钟是同时处于活动状态的时钟,但在共享时钟树部分上除外。然后,这些时钟在彼此之间和共享部分外部没有逻辑路径,它们在逻辑上是互斥的。在设计中不存在没有交互的无约束逻辑排他时钟组。

18.单击“Next”继续。

具有交互的逻辑互斥时钟是同时处于活动状态的时钟,但在共享时钟树部分上除外。当这些时钟彼此之间具有逻辑路径时,仅限于共享时钟树部分的时钟在逻辑上是互斥的,因此与没有交互的逻辑互斥时钟不同地受到约束。在设计中没有具有交互的无约束逻辑排他时钟组。

19.单击“Next”继续。

“Asynchronous clock domain crossings”页面建议对安全跨时钟域进行约束。此设计不包含任何不受约束的跨时钟域。

20.单击“Next”继续。

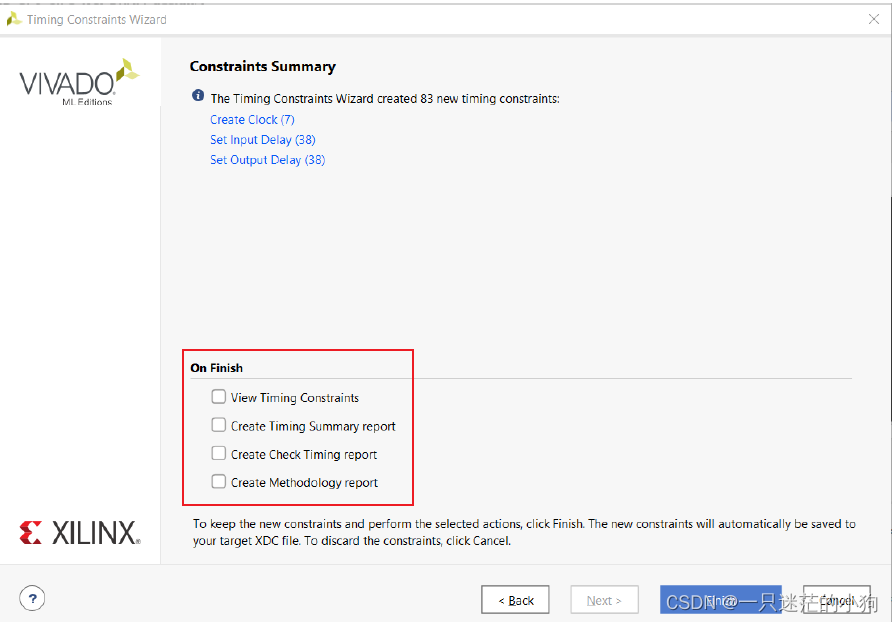

下图显示了“Timing Constraints Wizard”向导的最后一页。通过单击链接可以查看向导生成的所有约束。如果希望在向导完成后运行任何报告,可以使用向导中的复选框进行选择。

21.单击“ Finish”以完成“Timing Constraints”向导。

步骤4:使用“Constraints Editor”

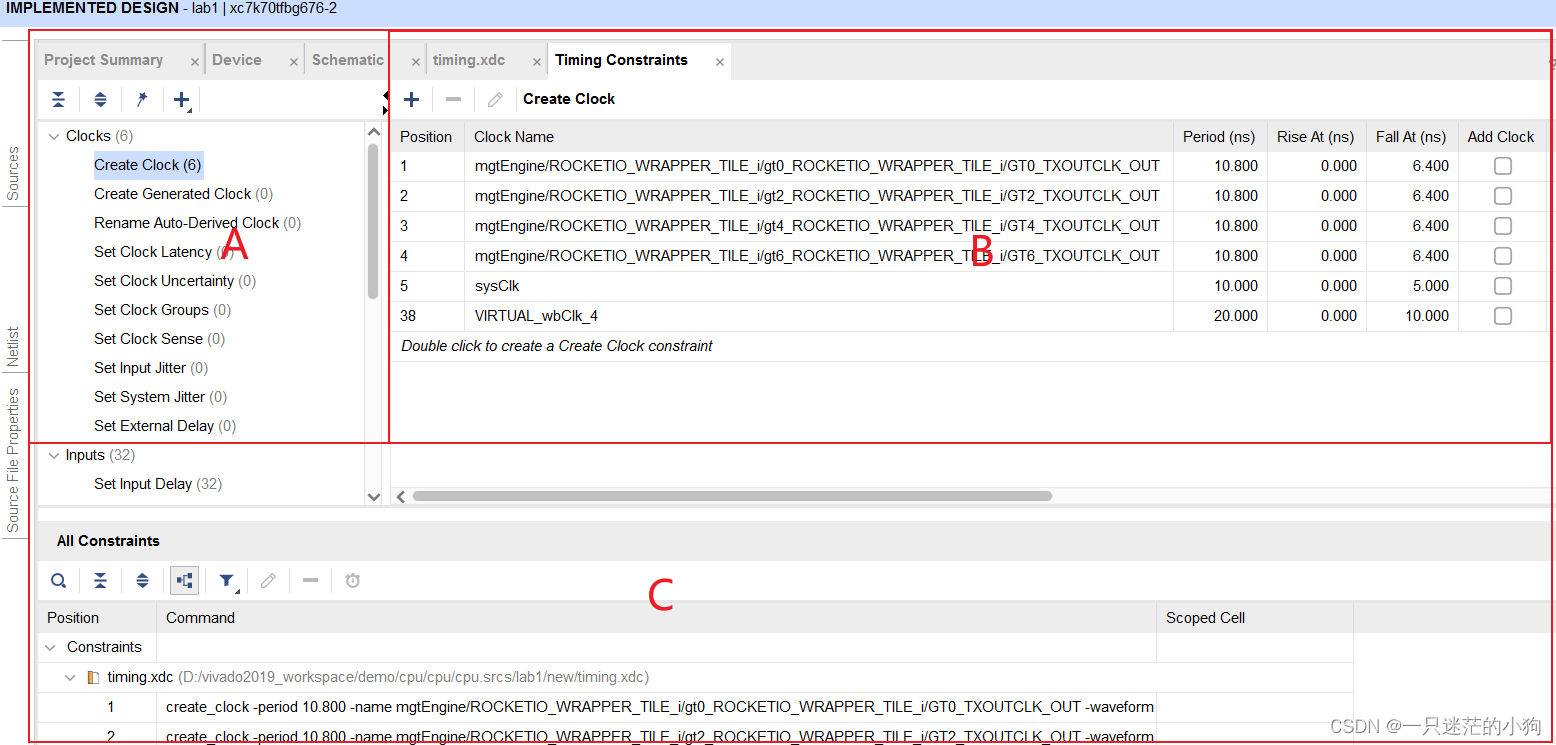

1.在“Synthesized Design ”部分下的“Flow Navigator”中单击“ Edit Timing Constraints ”。Vivado IDE显示“ Edit Timing Constraints ”窗口。

“Timing Constraints”窗口有三个部分,如上图所示:

•Constraints tree view:标记为部分A。此部分显示按类别分组的标准时序约束。双击此部分中的约束将打开一个窗体,以帮助您定义选定的约束。

•Constraints Spreadsheet:标记为B部分。此部分显示当前在“约束”树视图中选择的类型的时序约束。如果愿意,可以使用它直接定义或编辑约束,而不用使用“约束”向导。

• All Constraints:标记为C部分。此部分显示设计中当前存在的所有时序约束。时序约束向导可以识别丢失的时钟、I/O延迟和跨时钟域异常,但它不处理一般的时序异常。将使用时序约束编辑器来创建此设计中存在的异常。

首先,将在GTPRESET_IN输入上设置一个错误的路径。这是在“Timing Constraints”向导的输入延迟页面上取消选中而跳过的输入约束。GTPRESET_IN信号是一种异步复位,在设计中正确同步。有关错误路径的更多信息,请参阅Vivado Design Suite User Guide: Using Constraints (UG903)。

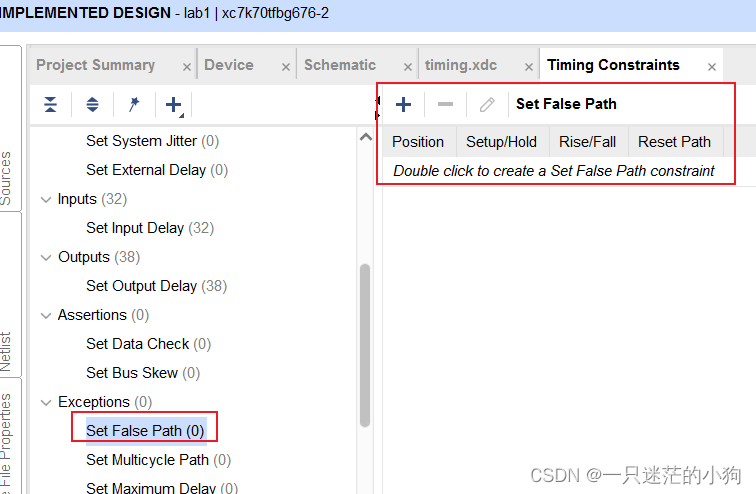

2.在“ Constraints”树视图中,向下滚动到“Exceptions”类别,如下图所示。

3. 双击“Set False Path”

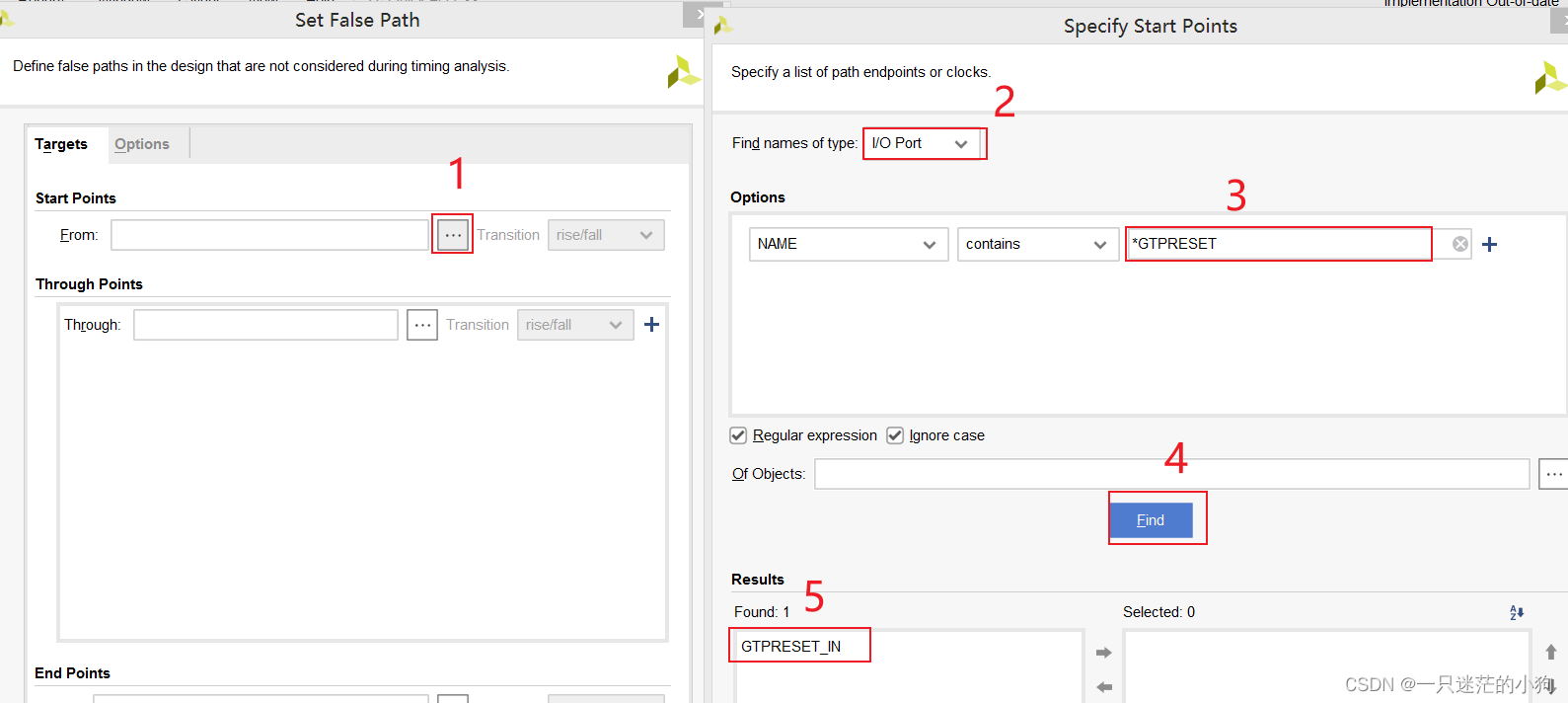

4.在“ From”文本框的右侧,单击“ Choose Start Points”按钮。此时将显示“Specify Start Points”对话框。

5.从查找类型名称下拉列表中,选择I/O端口,如下图所示。

6.在“Options”下,选择"Name", "contains",然后在搜索模式文本框中输入GTPRESET_in。

7.单击“Find ”按钮。

8.在查找结果文本框中选择GTPRESET_IN,然后按向右箭头将其移动到所选名称文本框。

提示:您也可以双击GTPRESET_IN将其从“Find results”列表移动到“Selected names”列表。

请注意,在执行这些不同操作时,对话框底部显示的“Command”字段会发生变化。get_ports命令更改为:

get_ports "*GTPRESET_IN*"

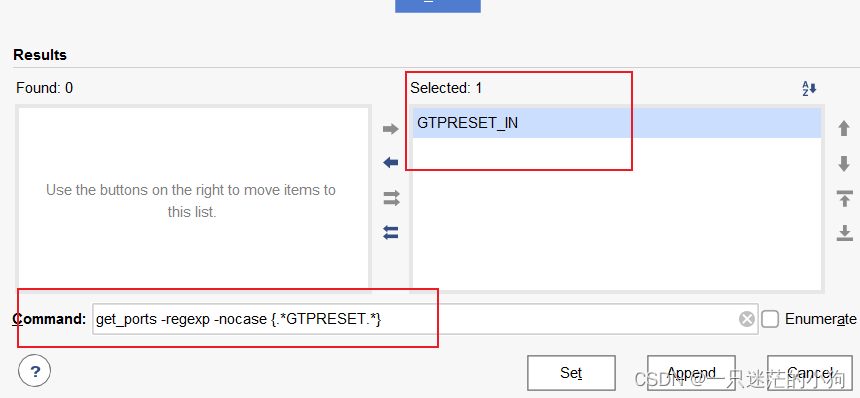

9.在“ Specify Start Points ”对话框中单击“Set”。已完成的“ Set False Path”对话框如下图所示。请注意对话框底部的“Command”字段中的以下命令文本:

set_false_path -from [get_ports -regexp -nocase {.*GTPRESET.*}]Vivado IDE显示通过对话框创建的所有约束的Tcl命令形式,供您查看。这对于学习Tcl命令语法以及在添加最终约束之前验证它非常有用。

10.单击“OK”关闭“Timing Constraint Editor”。Vivado创建错误路径异常。

Add a MultiCycle Path(添加所周期路径)

接下来,将使用约束编辑器添加一个多周期路径。

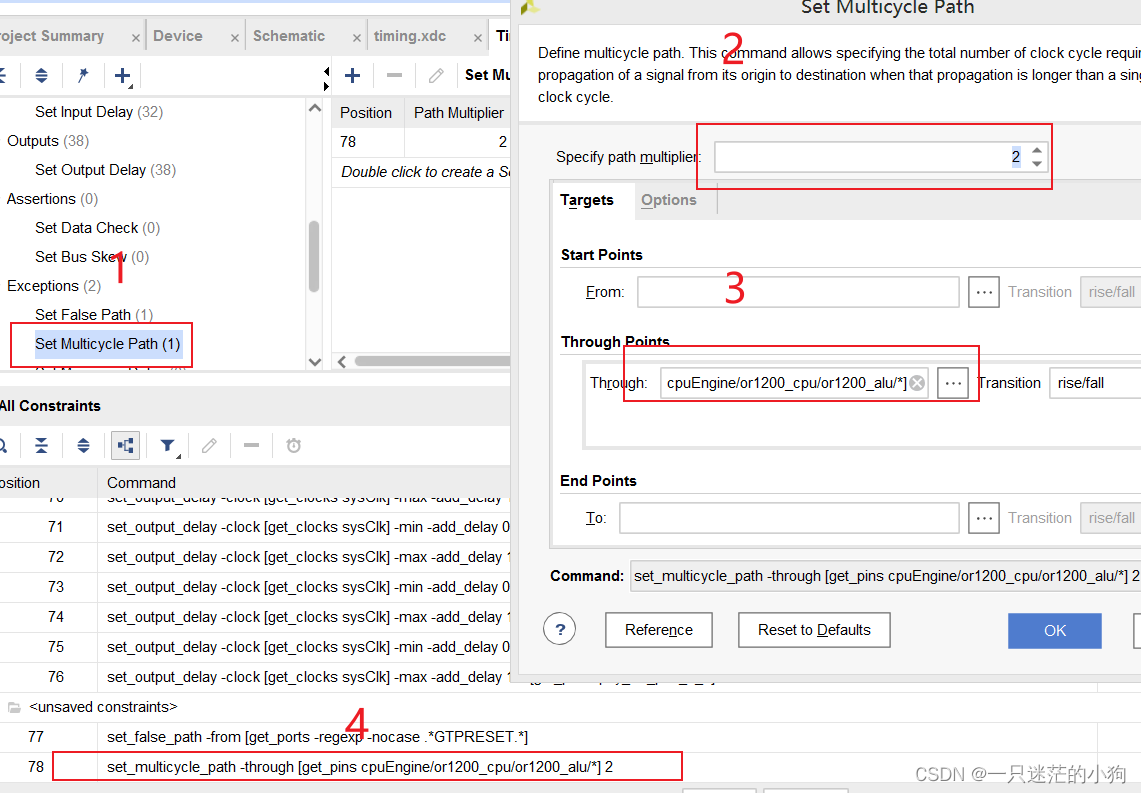

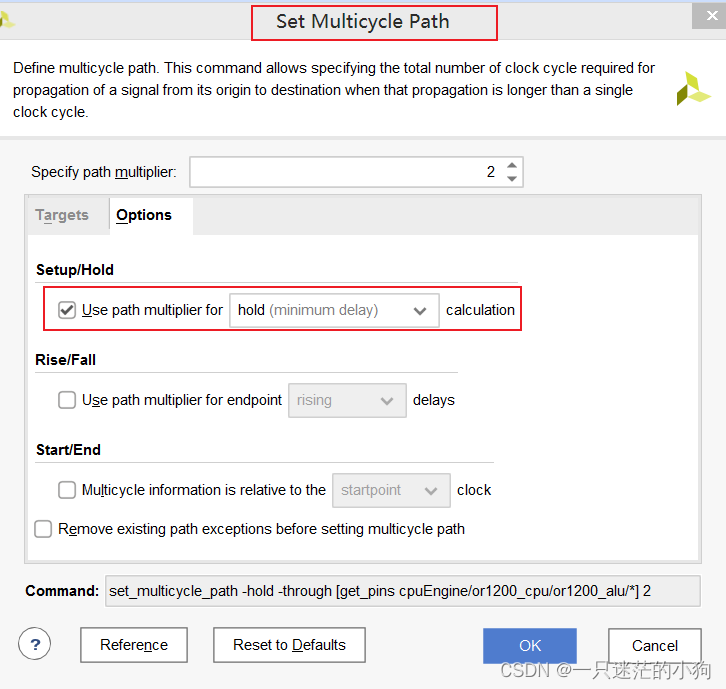

1.双击树的“Exceptions”类别下的“Set Multicycle Path”。

2.在“Set Multicycle Path”对话框中,将路径乘数设置为2。

3.在“Through ”输入框中,键入以下字符串(或者,您可以从这里复制和粘贴它):

[get_pins cpuEngine/or1200_cpu/or1200_alu/*]请注意,Tcl命令显示在“Command”字段中。

4.单击“OK”。

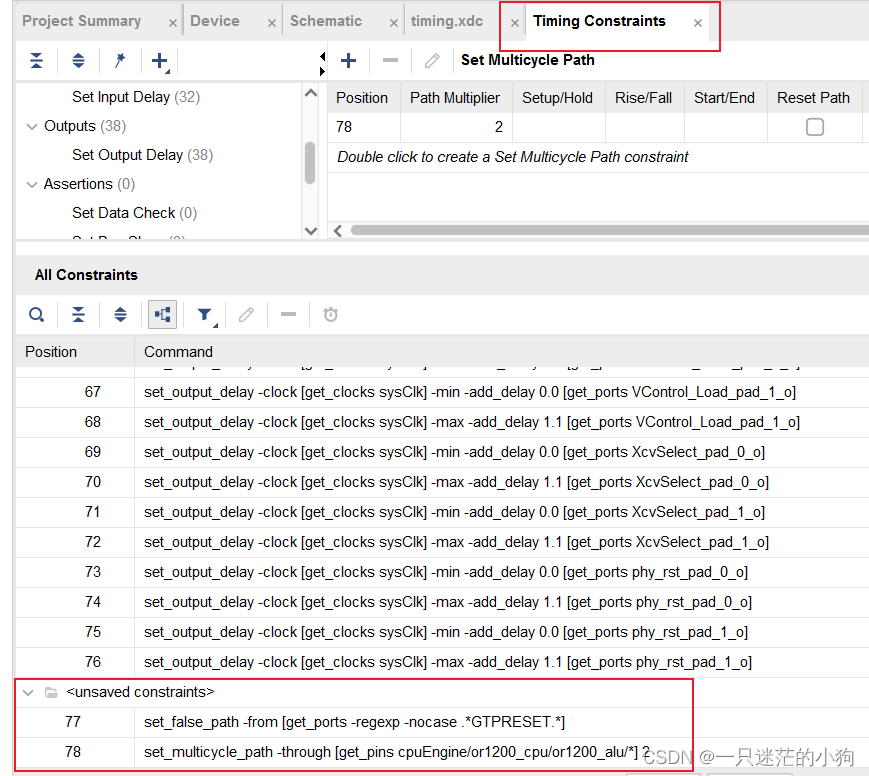

一个新的多周期路径将添加到<unsaved_constraints>部分的约束编辑器中,如下图所示。

默认情况下,添加多周期路径会将setup时间推至指定的周期数(N),但也会将hold时间推至N–1个周期。这通常不是预期的,可能会导致Vivado工具花费大量时间修复hold 时序冲突。

在这种情况下,您需要设置路径时钟。要实现这一点,您需要在hold 边沿上将另一个多周期路径定义为1,这样N–1为零。有关这种情况的更多信息,请参阅Vivado Design Suite User Guide: Using Constraints (UG903)。

5.第二次双击树的“Exceptions”类别下的“Set Multicycle Path”。请注意,之前输入的所有字段仍在填写中。

6.在“Set Multicycle Path”对话框中,将“Path Multiplier”更改为1。

7.选择“ Options”选项卡。

8.在“Setup/Hold”下,选中“Use path multiplier”复选框。

9.使用下拉菜单选择 hold (minimum delay)。

10.单击“OK”。

现在,在内存中有了一个完全受约束的设计。要将约束保存到磁盘,请继续执行步骤5:保存约束。

注意:有关添加多周期约束的原因的更多信息,请单击Xilinx Customer Community。有关检查工具是否应用了写入异常的更多信息,请单击Xilinx Customer Community。

Step 5: Saving Constraints(保存约束)

约束管理是设计流程中的一个重要步骤,Vivado design Suite提供了将新约束添加到现有约束文件、覆盖现有约束或创建新约束文件以跟踪设计更改或完成缺失约束的灵活性。已经为设计创建了一些定时异常,但这些异常只存在于内存中,还不存在于磁盘上。需要将异常保存到timing.xdc文件中。

1.在Vivado的“Sources”窗口中,双击“Constraints ”下的timing.xdc→ lab1。

2.滚动到文件底部,注意文件中不存在set_false_path和set_multipcycle_path约束。这也在“Timing Constraints Editor”中反映为<unsaved_Constraints>,如下图所示。

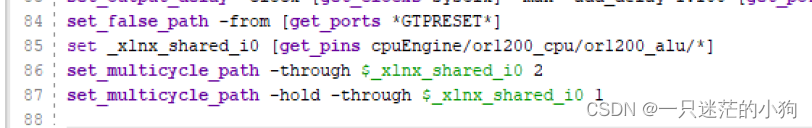

3.单击“Save Constraints”按钮或从主菜单中使用“File → Constraints → Save”命令。

4.单击timing.xdc选项卡标题中的“reload”链接,从磁盘重新加载约束文件。请注意,假路径和多周期路径现在在timing.xdc文本文件中可见,如下图所示。

注意:Tcl变量_xlnx_shared_i0由Vivado自动推断为在多个时序约束之间共享相同的对象集合。

Step 6: Clock Interaction Report(时钟交互报告)

在创建约束之后或创建约束期间,必须验证约束是否完整和安全。Vivado Design Suite默认情况下将所有时钟一起时序分析,除非通过定义时钟组或其他时序例外情况另行指定。set_clock_groups命令指定异步或独占时钟域,并禁用它们之间的时序分析。还可以在两个时钟之间使用set_false_path异常来禁用它们之间所有路径的时序分析,或者在特定的网表对象上使用它来仅禁用某些路径。 set_multycle_path异常修改时序分析期间使用的时钟边沿,而不是默认的单周期假设。有关使用这些约束的更多信息,请参阅Vivado Design Suite User Guide: Using Constraints (UG903)。有关时钟交互的更多信息,请单击Xilinx Customer Community。

Vivado自动推断两个不同时钟域之间交叉的路径的时序路径要求,称为时钟间路径,并对相位和偏移进行假设。“ Report Clock Interaction”命令报告时钟间路径,以帮助识别潜在问题,如两个时钟之间不现实的setup或hold要求,或异步时钟之间不安全的定时(没有已知的相位关系),这些问题可能导致硬件行为不稳定。

有关时钟交互报告的更多信息,请参阅Vivado Design Suite User Guide:Design Analysis and Closure Techniques(UG906)中的“Details of the Clock Interaction Report”。

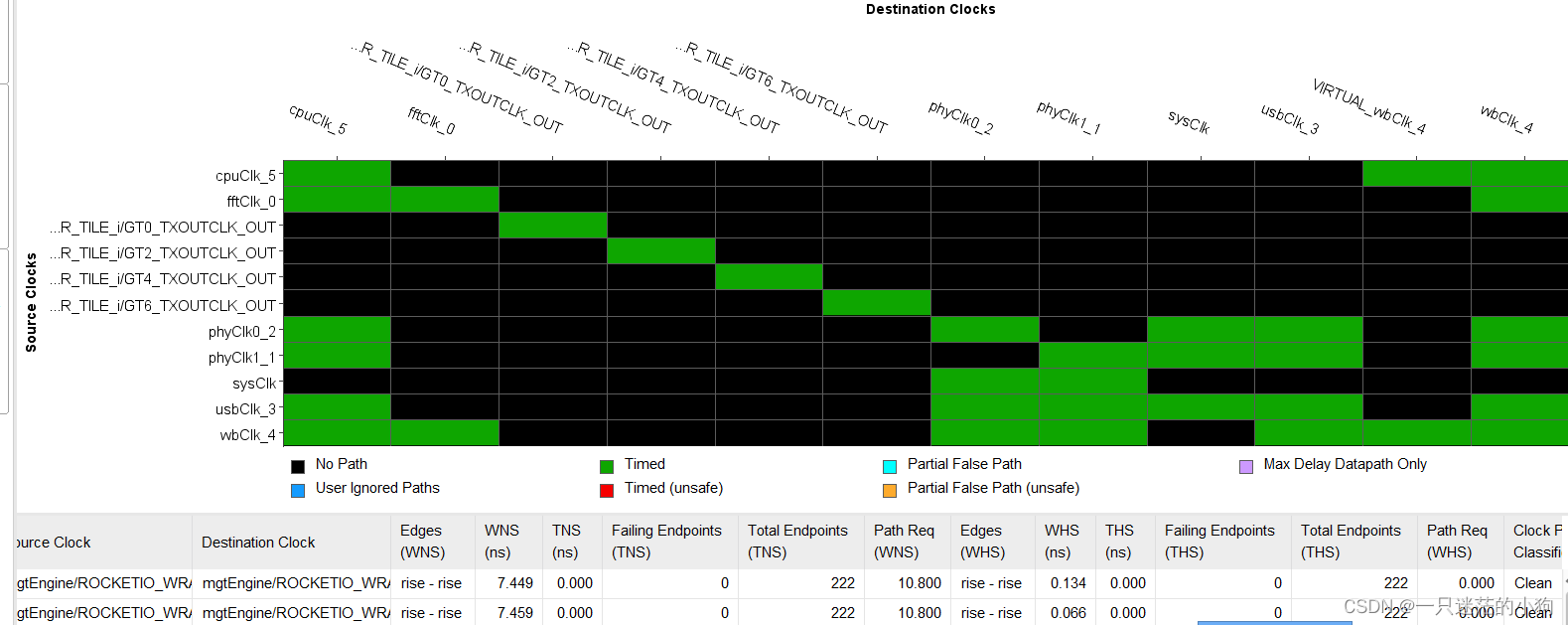

1.从“ Flow Navigator”中,选择“Synthesized Design ”→ “Report Clock Interaction ”,然后单击“ Report Clock Interaction ”对话框中的“OK”以接受默认设置。

Vivado IDE生成一个图形矩阵,说明设计中各种时钟的关系,如上图所示。对于这种设计,主时钟(sysClk)连接到MMCM,MMCM生成六个额外的时钟。所示的时钟交互作用是在这些生成的时钟之间。此外,“ Timing Constraints”向导还创建了额外的生成时钟和虚拟时钟,以完全约束设计。通常,“Clock Interaction”报告显示的时钟对之间没有路径(黑色),路径安全定时(绿色和浅蓝色),路径未安全定时(红色和橙色),路径受“Max Delay Datapath Only ”约束。在这种设计中,只有黑色单元格和绿色单元格显示在矩阵中。

重要:矩阵中的绿色并不意味着满足时序,它只是意味着时序约束和时钟树拓扑允许安全的时序分析和精确的松弛计算。

在“ Clock Interaction”报告中,不安全意味着在源和目标时钟的前1000个时钟周期内没有公共主时钟(没有已知的相位关系),或者没有公共节点(导致未知相位关系的不常见情况),或者不存在公共时钟周期。Vivado时序引擎根据前1000个周期选择发射和捕获时钟的边沿,但这些边沿可能无法反映时钟之间最悲观的分析。

提示:此处描述的颜色是默认颜色。您的颜色配置可能与上图所示的不同。

2.单击窗口选项卡中的“Close”按钮,关闭“Clock Interaction”窗口。

Step 7: Timing Summary Report(时序摘要报告)

时序路径在时序元件处开始和结束。输入和输出端口不是时序元件,默认情况下,Vivado时序分析不会对设计中I/O端口的时序路径进行定时,除非指定了输入/输出延迟限制。

在本步骤中,您将在Vivado中生成并解释时序报告。

1. Reports → Timing → Report Timing Summary。

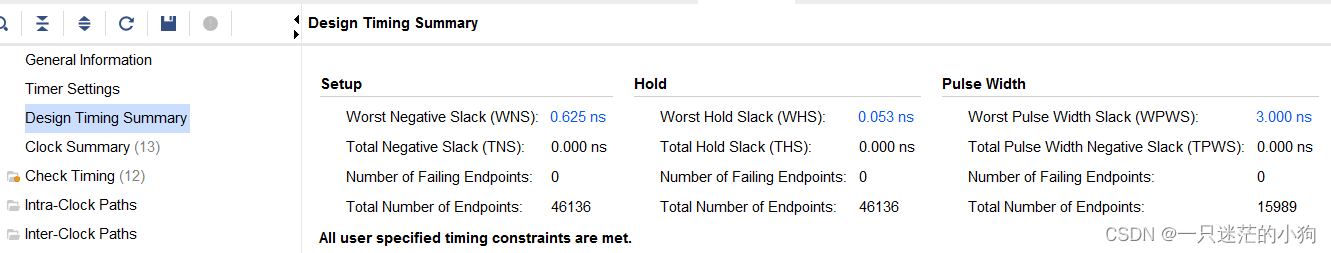

2.单击“OK”以使用默认选项生成报告。此时会打开时序摘要选项卡,如下图所示。

该设计通过了setup时序分析,但未通过hold时序分析。在实现设计之前,时序分析使用代表理想布局的估计净延迟。在流程的这一点上,小规模的hold冲突很常见,并将在布局布线步骤中得到解决。现在,请查看报告的内容。

3.点击设计时序摘要部分的Worst Negative Slack链接,查看设计中最差的时序路径,如下图所示。

4.选择最差路径时,按F4键调出其网表图。下图显示了设计中最糟糕的hold路径。

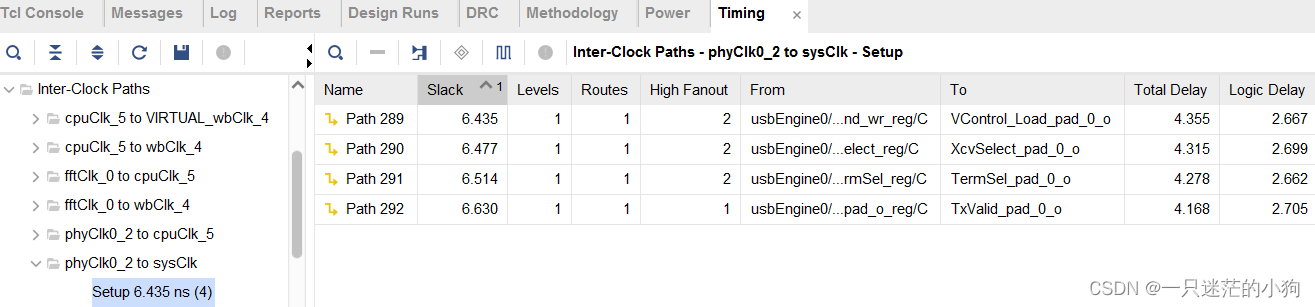

5.在 timing summary 摘要树中,选择 Check Timing。

•如下图所示,Check Timing标记了九个问题。

•其中八项是pulse_width_clock检查,时时约束向导也对其进行了标记,但未进行约束。这些违规具有较低的严重性,因为时时逻辑路径不需要相应的丢失时钟。

•Check Timing标记的剩余问题是no_input_delay检查,这是由于重置信号上的输入约束缺失,而重置信号被设置为false_path。在本例中也可以忽略这一点。

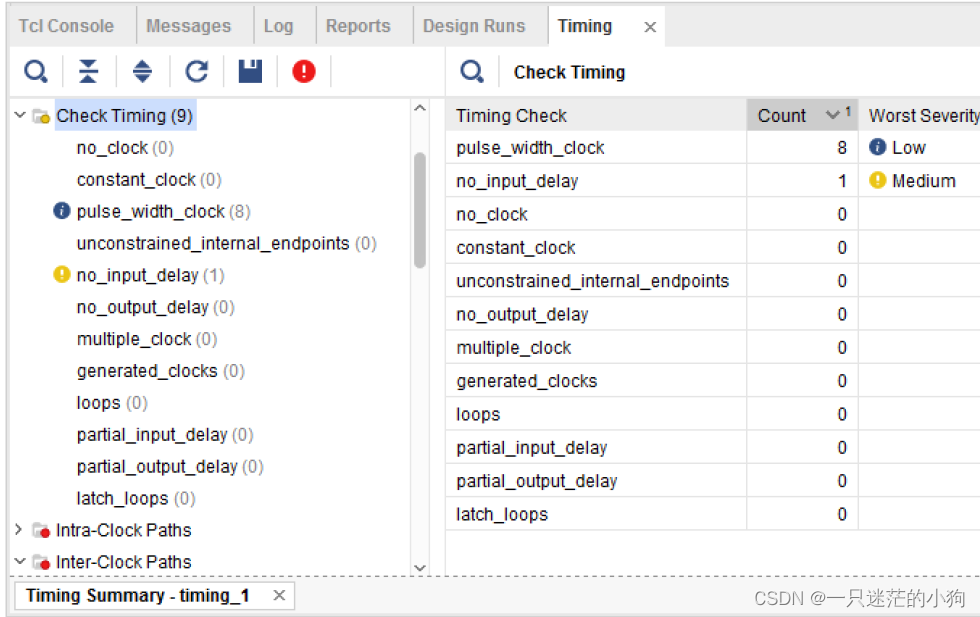

6.在 timing summary树中,选择Clock Summary,如下图所示。

时序摘要报告的时钟摘要部分列出了设计中的所有时钟,并显示了每个时钟的最终频率和波形。层次结构显示了生成的时钟和主时钟之间的关系(例如,cpuClk_5与sysClk)。例如它表明cpuClk_5是由主时钟SysClk产生的,并且其周期是sysClk的周期的两倍。

时序摘要报告的其余部分按其类型对路径进行分组。每个部分都列出了该组中的前十个路径(在生成报告时指定)。这些路径包括时钟间路径、时钟内路径、其他路径组、用户忽略路径和无约束路径。单击根将显示下面的路径摘要。进一步扩展树将最终显示每组的顶部时序路径。

![Rasa 3.x 学习系列-Rasa [3.5.8] -2023-05-12新版本发布](https://img-blog.csdnimg.cn/a9437d24cb0d48f78e2f4b0bc016212d.png)