CPU Architecture [/ˈɑːrkɪtektʃər/]

- 指令集架构 (Instruction Set Architecture)

- 精简指令集处理器 RISC (Reduce Instruction Set Computer)

- 复杂指令集处理器 CISC (Complex Instruction Set Computer)

- CPU按指令集架构分类

- ARM

- 运行模式

- 非特权模式

- 特权模式

- 切换

- 寄存器组

- 未备份寄存器,R0~R7,共享同一组物理寄存器,灰色

- 备份寄存器,R8~R14,在不同模式有自己独有的寄存器

- 程序计数器,R15

- 程序状态寄存器

- Cortex系列处理器内核

- 其他

- 冯·诺伊曼

- 哈弗

- CPU MPU MCU DSP AP BP SOC

- 链接

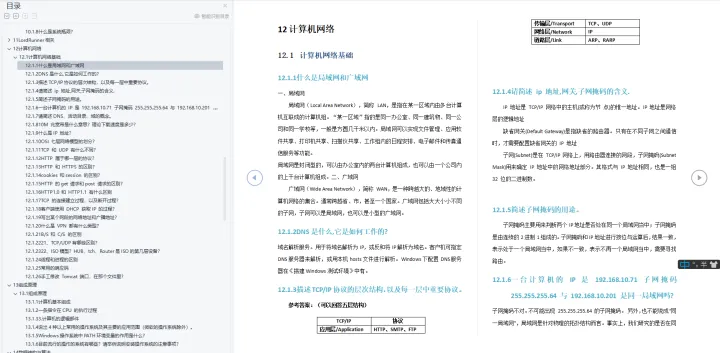

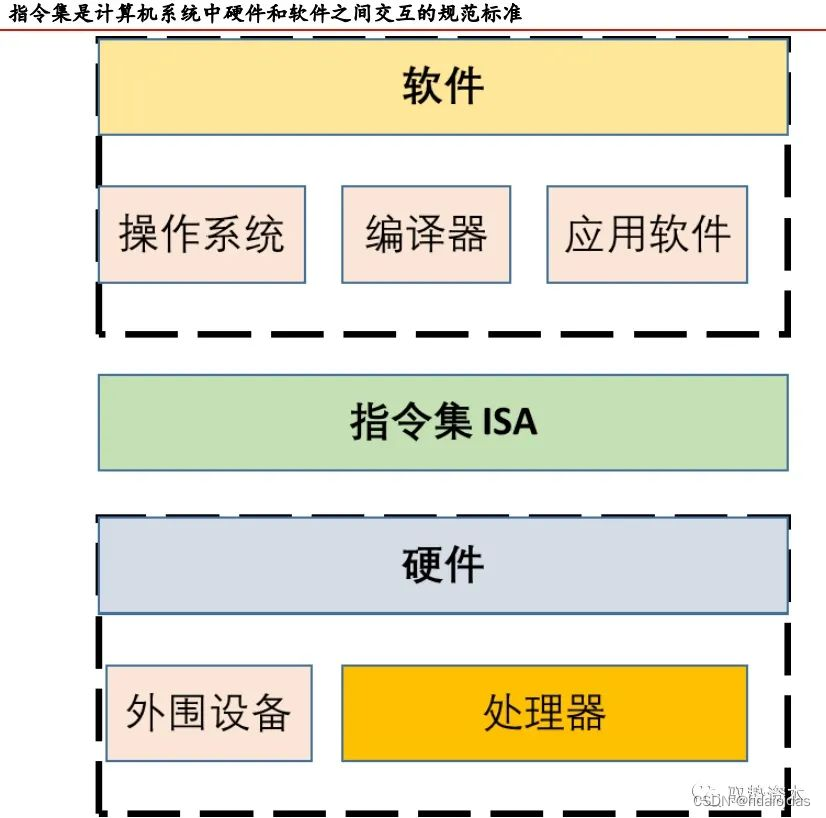

指令集架构 (Instruction Set Architecture)

I:计算机硬件直接能识别的命令,由一串二进制数码组成。一条指令通常由两个部分组成:操作码和地址码。

IS:处理器可以执行操作的最小单元的集合。例如加减乘除就是由具体的指令来实现的。

精简指令集处理器 RISC (Reduce Instruction Set Computer)

一条指令完成一个基本“动作”,多条指令组合完成一个复杂的基本功能

选取了使用频率高的简单指令,指令长度固定,多为单周期指令

功耗、体积、价格方面有优势,多用于嵌入式领域

复杂指令集处理器 CISC (Complex Instruction Set Computer)

侧重于硬件执行指令的功能性

一条指令完成一个复杂的基本功能

指令长度与周期不固定,在处理能力上有优势

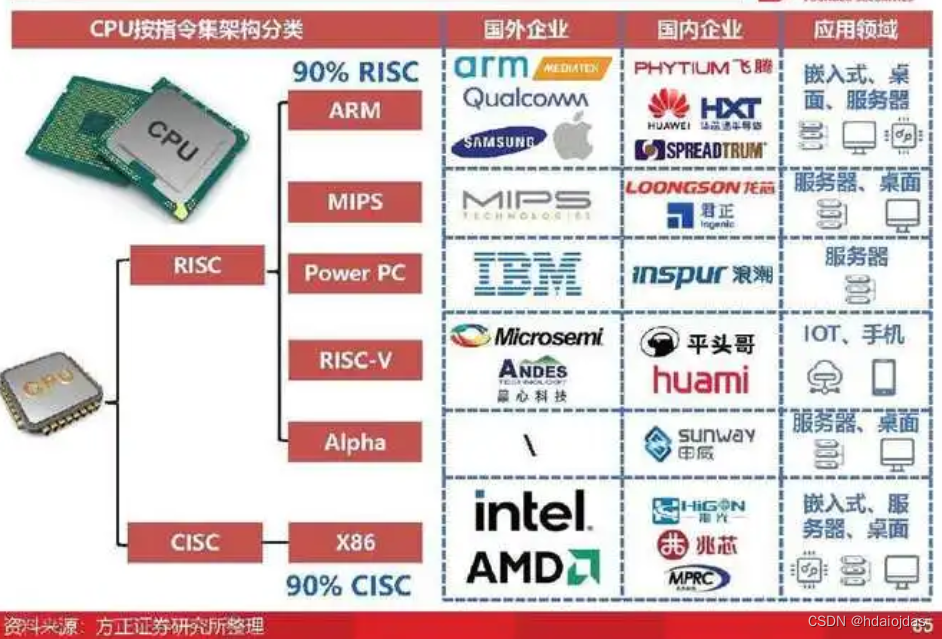

CPU按指令集架构分类

ARM

进阶精简指令集机器(Advanced RISC Machine)

- 对内存只有读、写指令

- 数据运算在CPU内实现

- 使用RISC指令CPU复杂度小,易于设计,系统软件多些

Cortex-A7为例↓

运行模式

非特权模式

- User 用户模式,大部分程序运行的时候处于此模式

特权模式

- Sys(System) 系统模式,运行特权级的操作系统任务

- FIQ 快速中断模式,进入FIQ中断异常

- IRQ 一般中断模式

- ABT(Abort) 数据访问终止模式,用于虚拟存储及存储保护

- SVC(Supervisor) 超级管理员模式,供操作系统使用

- UND(Undef) 未定义指令终止模式

- MON(Monitor) 用于安全扩展

- Hyp 用于虚拟化扩展

切换

运行模式可通过软件、中断或异常进行切换。大多数程序运行在用户模式,不能访问系统所以资源,需进行模式切换,用户模式不能直接进行模式切换,需要借助异常来完成模式切换,需要切换模式时,用户程序产生异常,在异常处理过程中完成处理器模式切换。

- 板子上电,CPU处于SVC模式,使用SVC模式下的寄存器

- 程序发生中断,CPU进入IRQ模式,使用IRQ模式下寄存器

- CPU完成中断处理,切换会SVC模式,使用SVC模式下寄存器

- CPU发生某种异常,例如读取内存出错,进入ABT模式,使用ABT模式下寄存器处理错误

在某种模式下,CPU使用的是这种模式的资源(例如寄存器),免去保存上一模式所使用的寄存器

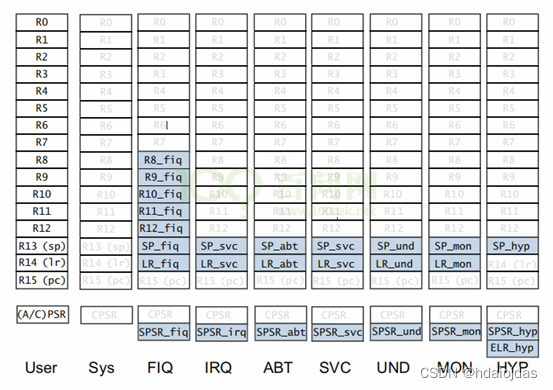

寄存器组

芯片内核寄存器组,Cortex-A9有9种运行模式,每种模式都有一组与之对应的寄存器组。

- 未备份寄存器,R0~R7,共享同一组物理寄存器

- 备份寄存器,R8~R14,在不同模式有自己独有的寄存器,蓝色

- 程序计数器,R15

- 程序状态寄存器

未备份寄存器,R0~R7,共享同一组物理寄存器,灰色

不同模式下,寄存器内数据会被破坏,没有特殊用途

备份寄存器,R8~R14,在不同模式有自己独有的寄存器

R8~R12 快速中断模式和其他模式分别用两种,快速中断模式和其他是独立的;

R13(SP)栈指针,8个物理寄存器,其中一个是User和Sys共用的;

R14(LR)链接寄存器,7个物理寄存器,其中一个是User和Sys和Hyp共用的;

程序计数器,R15

保存当前执行指令地址加8字节。

ARM处理器三级流水线:取指->译码->执行,循环执行。

当前正在执行第一条指令同事对第二条指令进行以嘛,第三条指令也被取出放在PC种。对于32位RAM处理器,每条指令4字节,即+8字节。

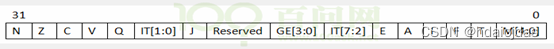

程序状态寄存器

当前程序状态寄存器CPSR和备份程序状态寄存器SPAR。

包含条件标志位、中断禁止位、当前运行模式标志等一些状态位和控制位。

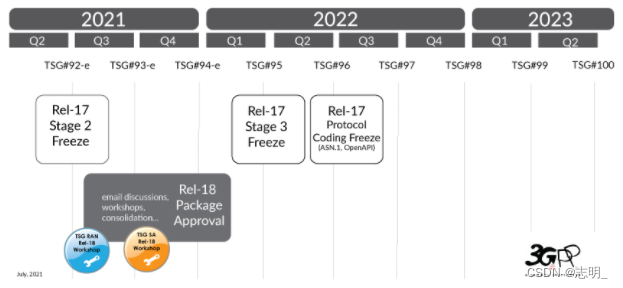

Cortex系列处理器内核

- Cortex-A系列面向高性能计算需求、运行丰富操作系统和程序任务的应用领域。A7x系列为代表的性能大核产品线和A5x系列为代表低功耗小核产品线

- Cortex-R系列面向实时应用的高性能处理器系列,运行在比较高的时钟频率,其响应延迟非常低。主要应用于硬盘控制器,汽车传动系统和无线通讯的基带控制等领域。

- Cortex-M系列内核被设计成面积更小,能效比更高。通常这些处理器的流水线很短,设计简单,最高时钟频率很低,功耗表现优异。

其他

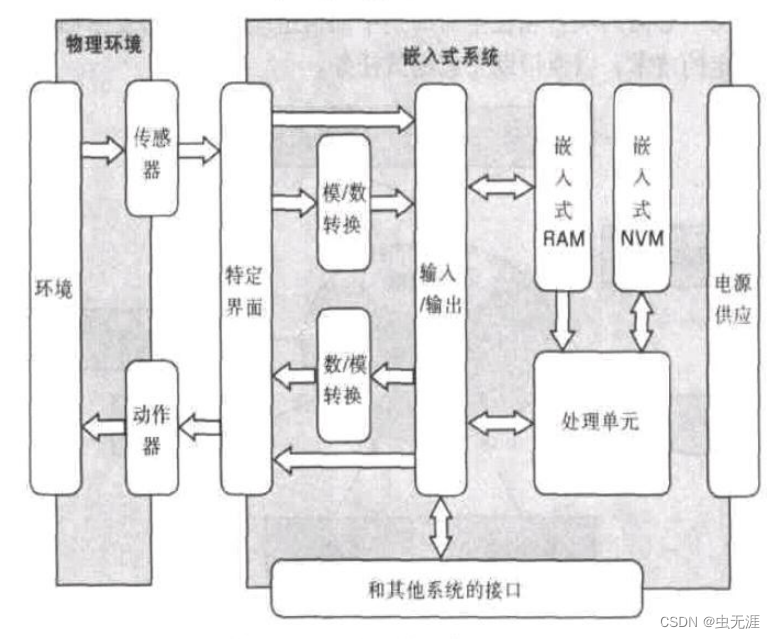

冯·诺伊曼

指令和数据需要从同一存储空间存取,经由同一总线传输,无法重叠执行。

哈弗

指令和数据存在两个相互独立的存储器模块,使用两条独立的总线连接CPU和存储模块。

现代的复杂芯片上,大多数看到是两者融合或者并存的体系。

CPU MPU MCU DSP AP BP SOC

现代CPU成为处理器的核心组件之一,而不是唯一组件。一些数字逻辑运算芯片在CPU外围集成了其他功能多样的组件,这些超大规模集成电路的CPU模块被称为处理器内核(Core)。

- CPU 通用高性能处理器,用在个人电脑和服务器上,Intel amd

- MPU 嵌入式微处理器,芯片集成度高,外设功能很丰富,主要用在移动设备和多媒体相关应用,高通 MTK

- MCU 微控制器,信号控制和简单运算,成本低,功耗低,用在对性能要求不高的地方,IOT、工业控制、智能家居等,ST GD

- DSP 数字信号处理器,性能较弱,功耗低,擅长数字运算,应用在需要大量实时计算的场合,比如音频编解码

传统手机中有AP和BP两个处理器组成

- AP 负责运行操作系统和多媒体应用的处理器,通常是MPU类型的处理器。MPU GPU

- BP 负责射频通信的处理器,通常是MCU或DSP类型的处理器。

MMU 内存管理单元,主要负责物理地址和虚拟地址的交换。没有MMU不能运行想linux一样的操作系统。MCU没有MMU,MPU有MMU。

- SOC 片上操作系统,芯片上有一个系统。把一个系统的核心功能集成到一个芯片上。

例:蓝牙SOC:nRF52832,集成了MCU和BLE。

手机SOC:高通骁龙888,集成了AP(MPU+GPU)和BP。

注:历史发展叫的名字,

链接

CPU指令集架构科普

cpu架构----通俗理解

聊聊MCU的困惑

ARM

https://www.100ask.net/