👉个人主页:highman110

👉作者简介:一名硬件工程师,持续学习,不断记录,保持思考,输出干货内容

参考书籍:《PCI.EXPRESS系统体系结构标准教材 Mindshare》

目录

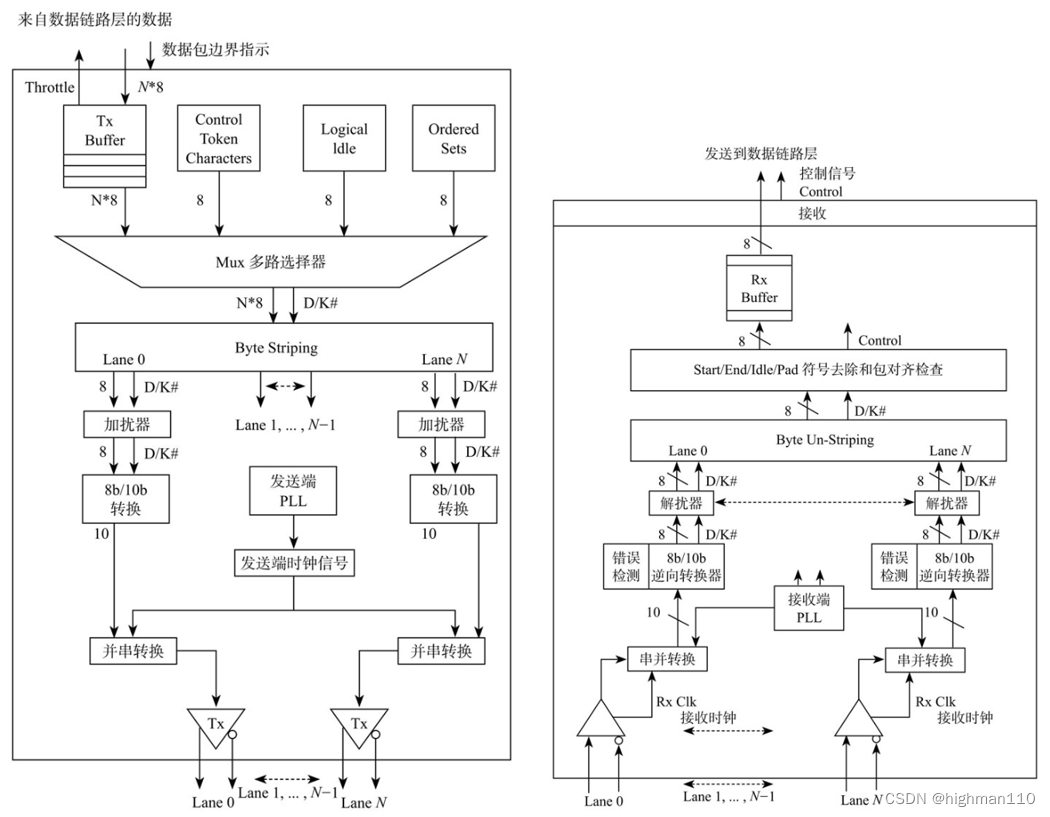

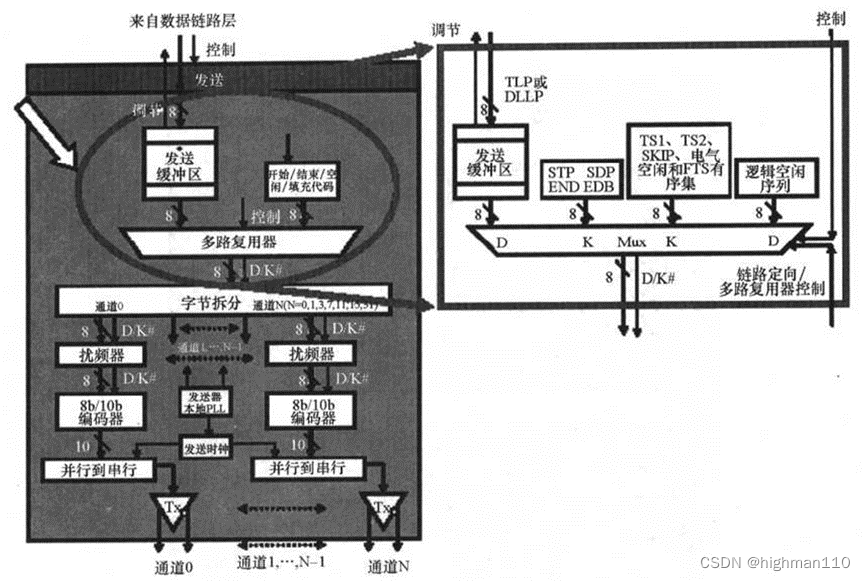

物理层逻辑框图

发送多路复用器

字节拆分器的位置

通道间的相位补偿

物理层逻辑框图

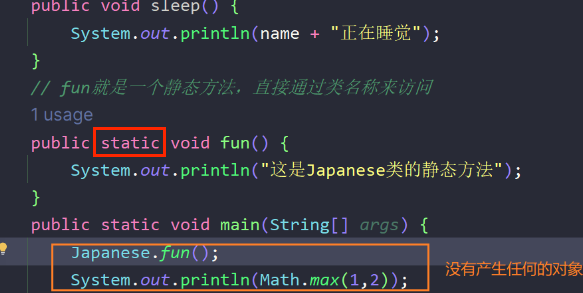

发送多路复用器

从上图可以看到,进入到多路复用器的内容有以下四种:

发送数据缓冲区的TLP和DLLP:当数据链路层提供了需要发送的数据包时,多路复用器会选通数据包码流通过字节拆分逻辑。发送缓冲区内的字符是数据或“D”字符,因此选通发送缓冲区的内容时,D/K#信号被驱动为高电平。

开始和结束字符:这些控制字符被附加到每个TLP和DLLP的开始和结束位置。这些成帧字符使接收器能够轻松地检测数据包的开始和结束。有两类开始字符,一类是开始TLP字符(STP),另一类是开始DLLP字符(SDP)。结束字符也有两类:结束好TLP(End Good TLP)或DLLP字符(END)和结束坏TLP(End BadTLP)字符(EDB)。来自数据链路层的控制信号与数据包的类型一起决定着选通哪类成帧字符。开始和结束字符是控制或“K”字符,因此当开始和结束字符分别在数据包的开始和结束位置被选通输出时,D/K#信号被驱动为低电平。

有序集(Ordered-Set):有序集的长度是4字符序列的倍数,它以逗号(COM)控制符开始,后面跟有其他字符。在如下所述的特殊事件期间才发送有序集。

1、链路训练期间在链路上发送定向序列1和2(TS1和TS2)有序集。基本复位、热复位或出现某些错误状况后都会出现链路定向。有关TSI和TS2有序集的详细内容后面会讲。

2、多路复用器以固定的间隔为字节拆分逻辑选通SKIP有序集,以便在链路另一侧端口的接收器电路中进行时钟的容差补偿。

3、一台设备要将其发送器置于电气空闲状态时,它必须通知位于链路另一端的远程接收器。为此,该设备要选通一个电气空闲有序集。

4、 一台设备要将其链路电源状态从L0s低功耗状态改为L0工作电源状态时,它要向接收器发送快速定向序列(Fast Traning Sequence,FTS)有序集。接收器使用该有序集来重新同步其PLL与发送时钟。

有序集以K字符开始,并且根据有序集的类型,它可能包含D或K字符。因此在有序集传输期间,可能某个时钟驱动D/K#信号为低电平,然后可能又将其驱动为高电平。

逻辑空闲序列:链路上不发送数据包时(称为逻辑空闲链路)会选通逻辑空闲字符,而不是让链路处于悬接状态(floating state)或什么也不做。这样做就保证链路上有信号转换,从而使接收器的PLL能够与发送时钟保持时钟同步。另外,接收器能够维持比特和符号的锁定。逻辑空闲序列由发送00h字符所组成。它由D类型的字符组成,因此在多路复用器选通逻辑空闲序列时,D/K#信号为高电平。

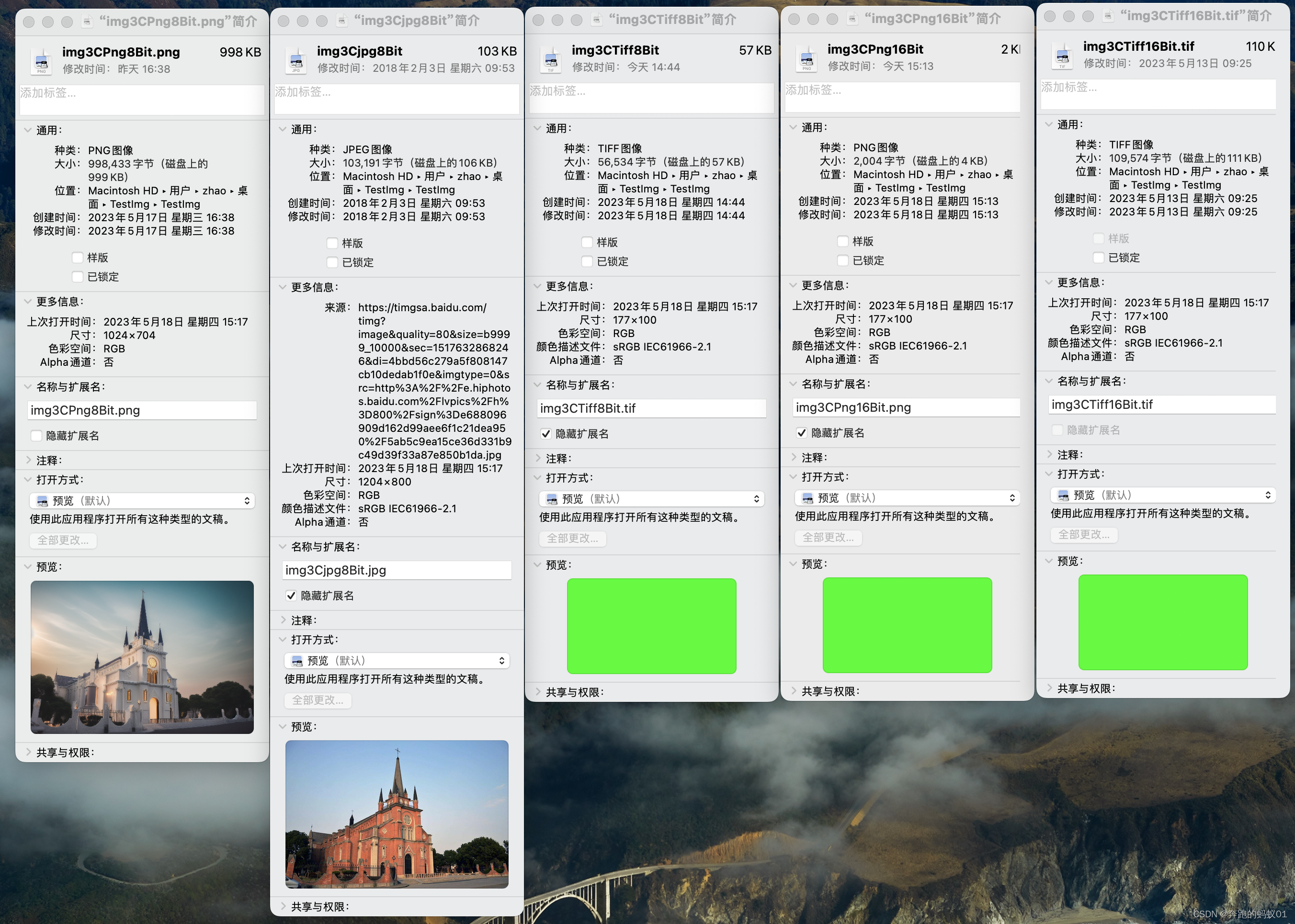

字节拆分器的位置

从上面的物理层框架图可以看到,发送端字节拆分在扰码和8B/10B编码之前,这里就有疑问了,拆分之后每一条lane都有扰码和8B/10B编码单元,这不是增加了芯片面积和成本吗?为什么不先统一做完扰码和8B/10B编码再拆分到多个lane?其实这么做的目的是为了使接收端能检测到每一条lane上无效的10b字符,如果发现某条lane有错误,可以禁用该通道,并用剩下的通道来重新初始化链路。

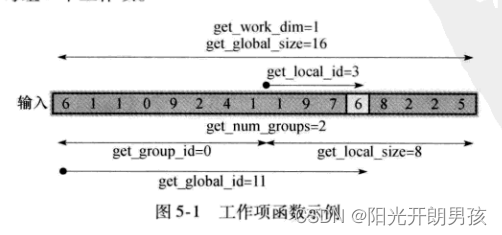

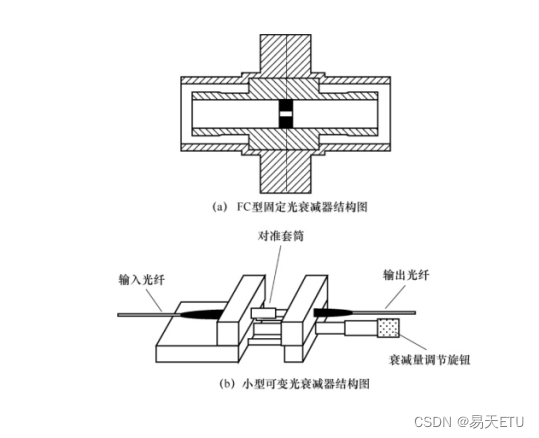

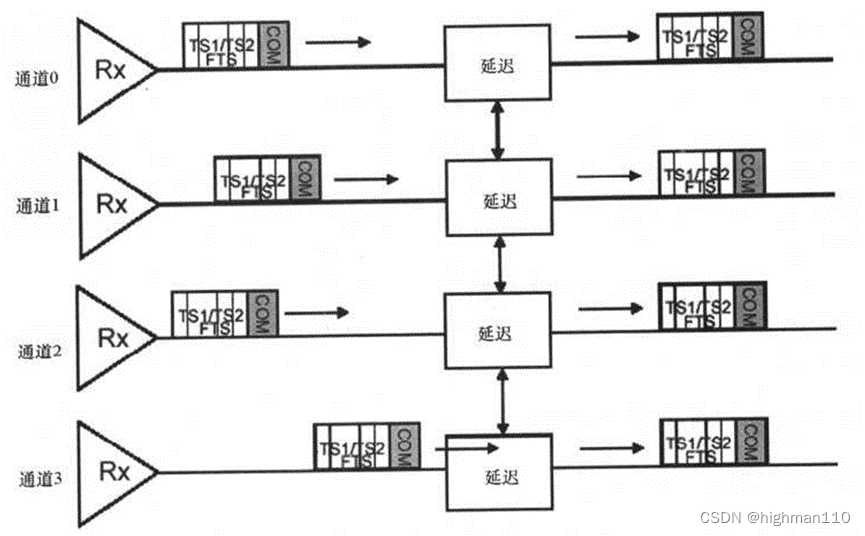

通道间的相位补偿

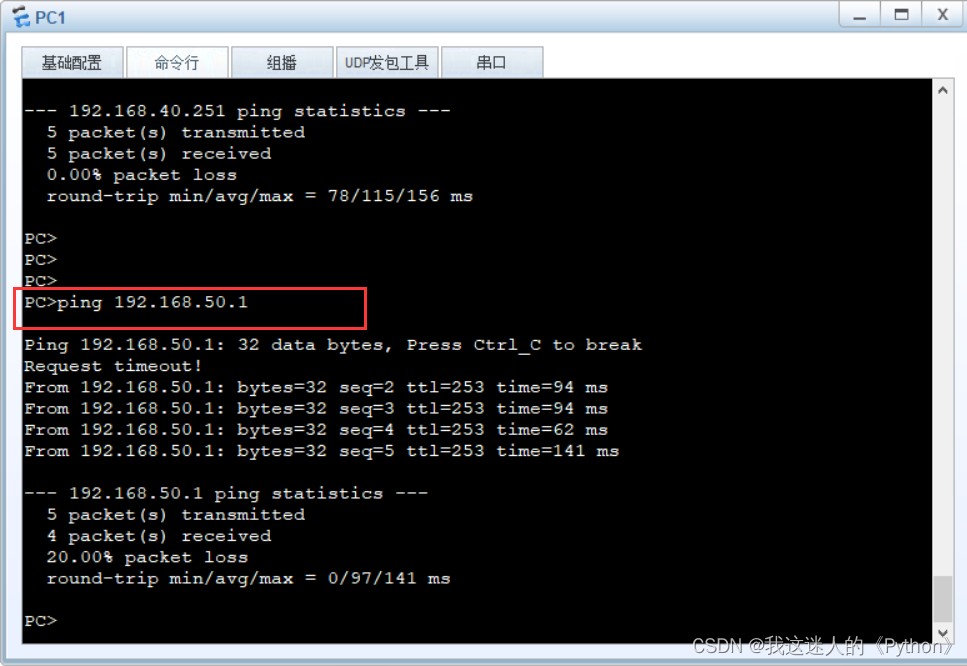

在多条lane的情况下,每条lane上的延时常常是难以控制一致的。如果在每条通道上同时发送的数据在不同时间到达接收器的每条通道,然后被反串行化并送人字节反拆分逻辑部件,那么肯定会引起混乱,所以必须要做通道间的相位补偿。

在链路训练时,ordered sets TS1/TS2、FTS是同时在每条lane上传输的,所以使得接收器的相位补偿逻辑可以使用这两个有序集来确定通道之间的相位偏移量。规范并未定义实现多通道对齐的方法。举个例子,接收器逻辑可以通过微调一个自动延迟电路(位于每条通道的接收器中)来补偿相位偏移,如下图所示:

仅在最初的链路定向或链路重新定向期间(也就是恢复期间)才传输TS1和TS2有序集,在退出L0s期间才传输FTS有序集。因此只在这些时间内接收器才执行相位补偿,而不是定期进行相位补偿。

后面再细讲物理层控制字符和链路训练相关内容。