|

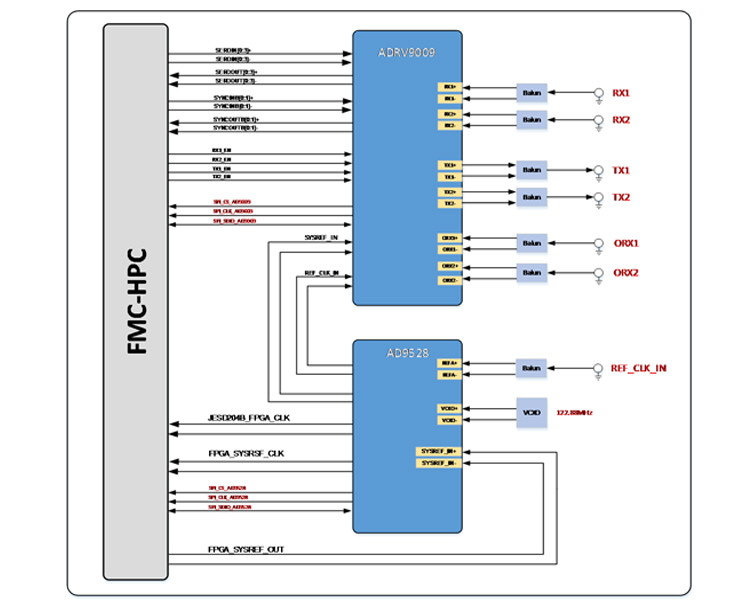

FMCJ450-基于ADRV9009的双收双发射频FMC子卡

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

FMC子卡设计资料原理图450-基于ADRV9009的双收双发射频FMC子卡 数字信号处理卡 射频收发卡 基站应用 便携测试设备

news2026/2/10 19:46:27

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处:http://www.coloradmin.cn/o/540702.html

如若内容造成侵权/违法违规/事实不符,请联系多彩编程网进行投诉反馈,一经查实,立即删除!相关文章

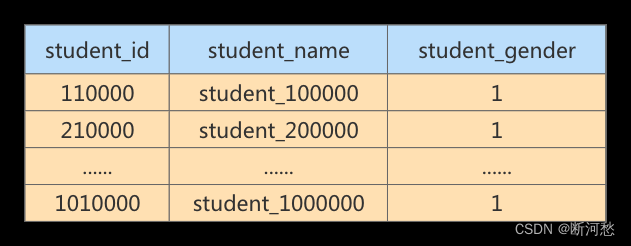

MySQL高级_第08章_索引的创建与设计原则

MySQL高级_第08章_索引的创建与设计原则

1. 索引的声明与使用

1.1 索引的分类 MySQL 的索引包括普通索引、唯一性索引、全文索引、单列索引、多列索引和空间索引等。 从 功能逻辑 上说,索引主要有 4 种,分别是普通索引、唯一索引、主键索引、全文索…

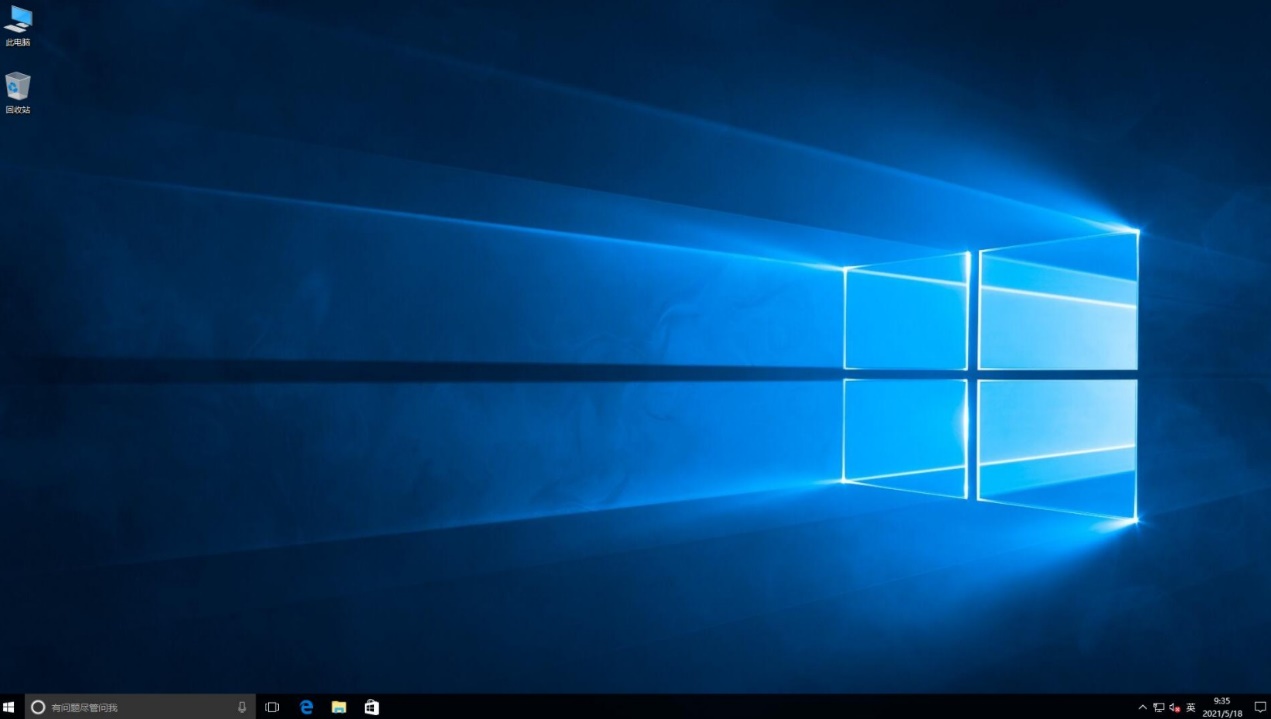

新手如何重装Win10系统 新手重装Win10系统的方法

电脑系统是电脑运行的核心,如果出现问题就需要重装系统。对于新手来说,重装电脑系统可能会显得比较困难和陌生。本文将介绍新手如何重装电脑系统Win10,让电脑新手也能轻松搞定。

新手重装Win10系统的方法

一、准备工作

1、下载极客狗电脑重…

canvas、svg的基本使用【数据可视化】

什么是数据可视化?

基本概念:是关于数据视觉表现形式的科学技术研究 这个概念向我们传达了两个信息: (1)数据可视化是一门学科 (2)数据可视化与数据和视觉有关 数据可视化简单理解,…

veth网卡的多队列及RPS

背景:

3.10内核下容器使用的veth网卡,默认开启的是一个队列,导致在某些单线程多TCP链接的应用场景下,出现某个CPU软中断高的情况。之前处理的方案一直是开启这个veth网卡的RPS,让其在多流场景下可以去分散到其它CPU上…

DSSM - 双塔经典模型(微软)

《Learning Deep Structured Semantic Models for Web Search using Clickthrough Data》论文由微软发表于 CIKM-2013。DSSM被广泛用于工业界的 召回/粗排 阶段。

模型结构 模型结构一目了然,非常简单,双塔结构:user侧一个塔,ite…

ChatGPT的兴起的时代,国内chatgpt产品大盘点

在人工智能技术的不断发展和应用下,自然语言处理技术成为了研究的热点之一。而其中最受关注的就是“聊天机器人”技术,而GPT(Generative Pre-trained Transformer)模型则是目前最流行的聊天机器人生成模型之一。

随着 ChatGPT 技…

蓝牙RSSI/BLE AOA/UWB室内定位技术哪个好?

蓝牙AOA定位技术的出现,弥补了蓝牙RSSI值定位精度不高的缺陷。从理论上来说,可以对目前的蓝牙RSSI定位方案进行一定程度的替代。当然了,在高精度定位应用领域中,UWB定位已经在批量的成熟商用了。蓝牙AOA也具有很高的定位精度&…

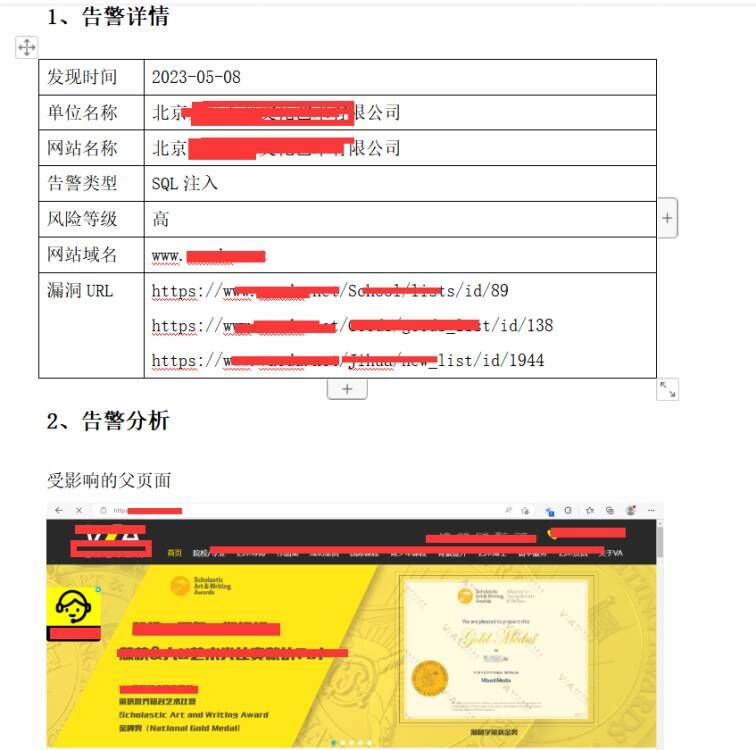

单位网站被黑被下达整改进行行政处罚

最近这几年,由于信息系统安全等级保护法的普及,越来越多公司收到当地公安网监部门打来的电话,说你们公司网站有漏洞,需要限期在2-3内进行漏洞整改和加固,遇到这种情况,不要着急,下面来分享一下该…

JavaEE(系列8) -- 多线程案例(单例模式)

目录 1. 设计模式 2. 单例模式 -- 饿汉模式 3. 单例模式 -- 懒汉模式 4. 单例模式(懒汉模式-多线程) 1. 设计模式 什么是设计模式? 设计模式好比象棋中的 "棋谱". 红方当头炮, 黑方马来跳. 针对红方的一些走法, 黑方应招的时候有一些固定的套路. 按照套路…

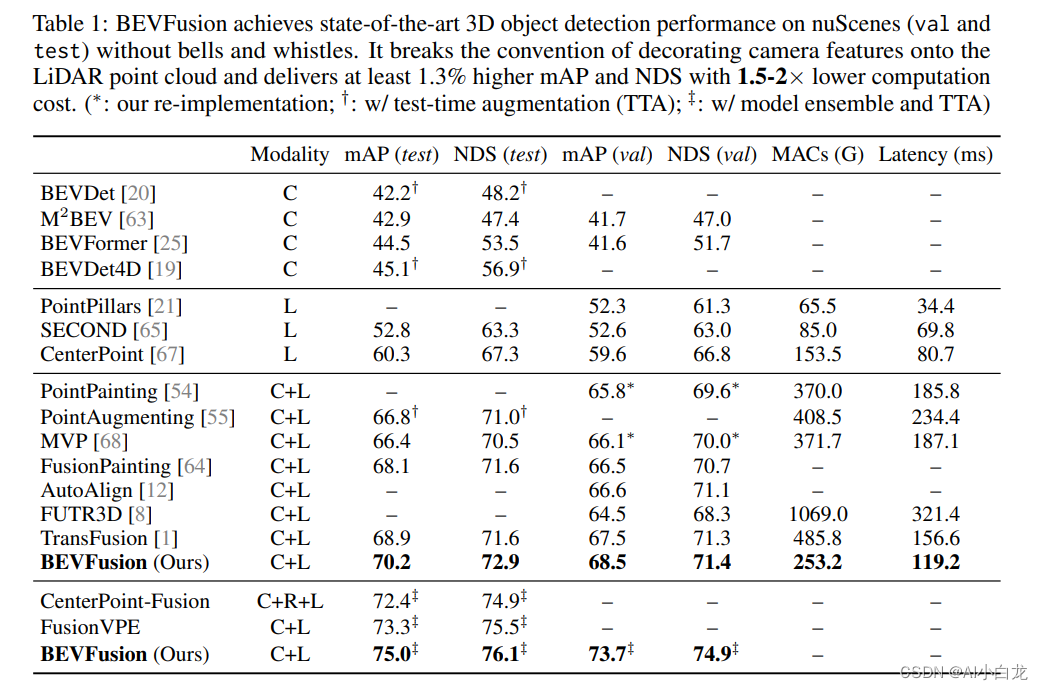

【融合感知】激光雷达和相机融合感知-BEVFusion

BEVFusion有两篇文章,这里在一起分析下不同,分别是:

【1】BEVFusion: A Simple and Robust LiDAR-Camera Fusion Framework.

【2】BEVFusion: Multi-Task Multi-Sensor Fusion with Unified Bird’s-Eye View Representation

先说结论&…

品牌联名又出圈了!小红书数据揭示,引爆流量三部曲

这几天,你们的朋友圈是不是被喜茶FENDI黄刷屏啦?近日,茶饮品牌牵手意大利奢侈品牌联名上新,一跃成为各平台热门。 品牌新联名,这次又出圈了! 喜茶可谓是联名界的老玩家了,曾与藤原浩、《梦华录》…

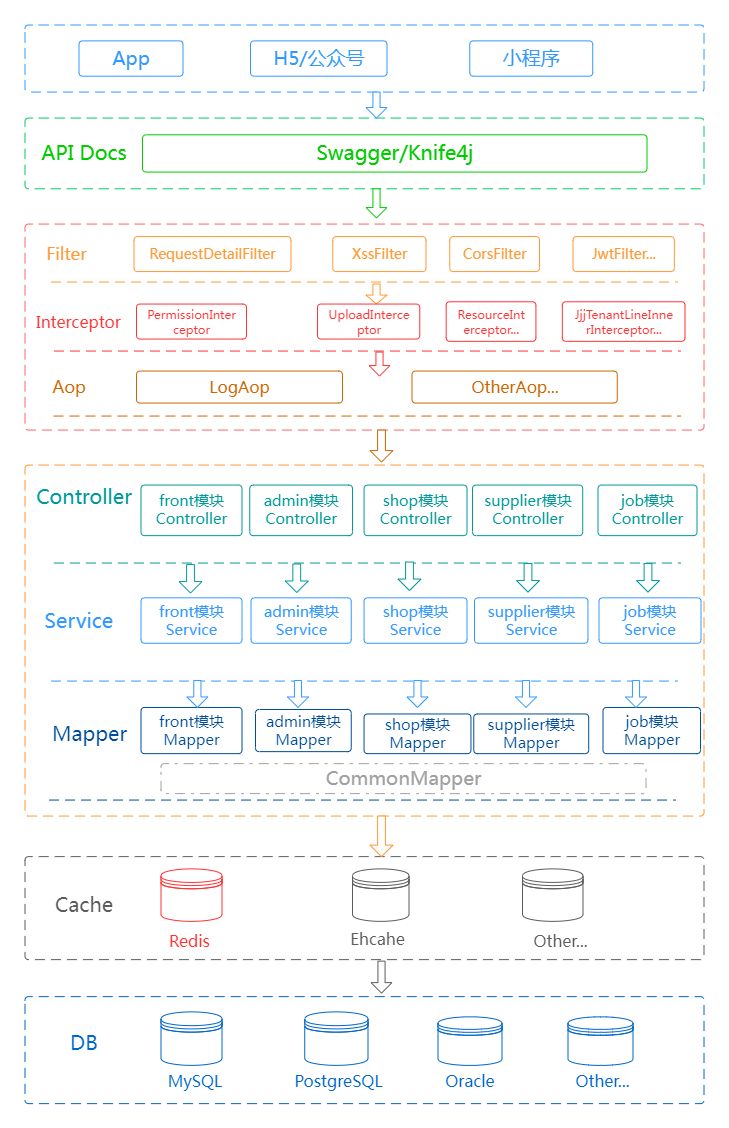

Java开发的多商户商城系统源码小程序app

Java开发的多商户商城系统源码小程序app主要是为商家提供一个线上销售平台,实现商品展示、订单管理、支付等功能,并且支持多商户注册,以下是它的功能介绍:

一、 用户端:1. 用户注册与登录:用户可以使用手机…

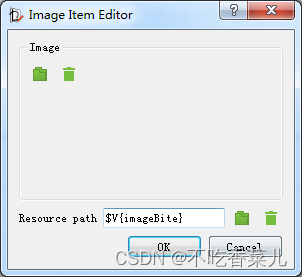

关于LimeReport导出报告在Qt下的使用问题

关于这个第三方库的使用网上有很多资料了

具体说一下关于文本和图片控件的使用 1、文本使用 如果需要自定义文本内容,需要的格式为上图$V{};

2、图片使用 如果需要自定义图片内容,需要的格式为上图$V{},写法和文本内容一样;

3、…

博士毕业答辩流程 注意事项

前言:2023年5月17日14:00-17:00,与实验室其他同学一起旁听了本实验室的博士论文答辩。接下来,我对博士毕业答辩的大致流程进行简要介绍,并对个环节的注意事项进行总结归纳,供毕业生参考。 目录 1. 准备阶段2. 汇报期间…

Python 框架学习 Django篇 (一) 安装及基本使用

环境说明 python 3.11.3 Django 4.2.1 idea 2023.1 一、安装调试 我这里默认idea和python环境都是装好的,直接从建项目开始 新建项目

项目名称: demo 安装Django

//配置清华镜像源

pip config set global.index-url https://pypi.tuna.tsinghua.edu.cn/simp…

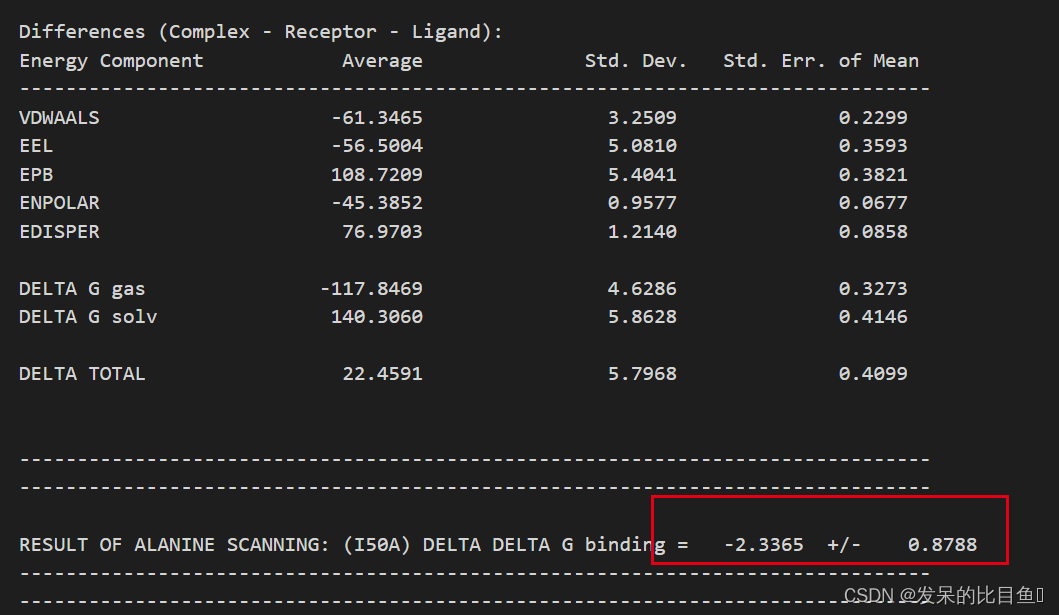

AMBER分子动力学模拟之结果分析(突变型的能量计算,丙氨酸扫描)-- HIV蛋白酶-抑制剂复合物(5)

AMBER分子动力学模拟之结果分析(突变型的能量计算,丙氨酸扫描)-- HIV蛋白酶-抑制剂复合物(5)

丙氨酸扫描

在带电残基上引入一个或几个丙氨酸,观察这些改变对蛋白功能的影响。置换成丙氨酸,去除了侧链上的活性基团,换成了体积小、无其他官能…

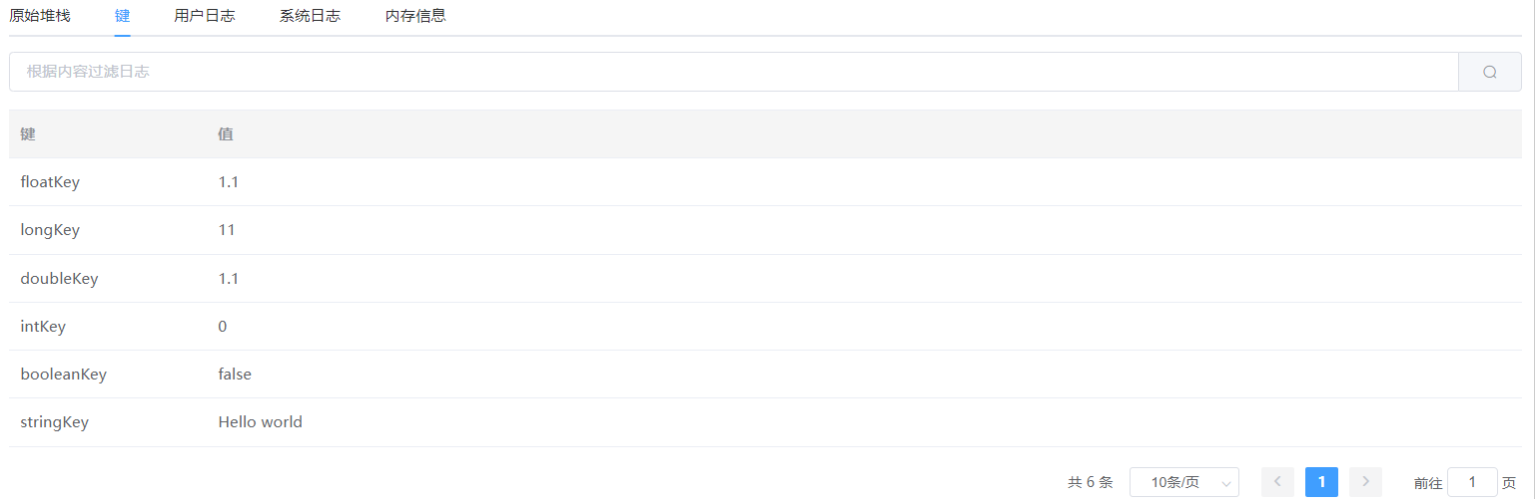

【AGC】新版鸿蒙崩溃SDK集成使用方法

【背景】

我们知道AGC的Crash SDK都是需要强制集成华为分析SDK的,在使用时的崩溃数据上报都要依靠分析服务来完成,这就容易受到限制,有时出现无数据的情况就要依次排查崩溃SDK与分析SDK,比较麻烦。而就在不久前,鸿蒙崩…

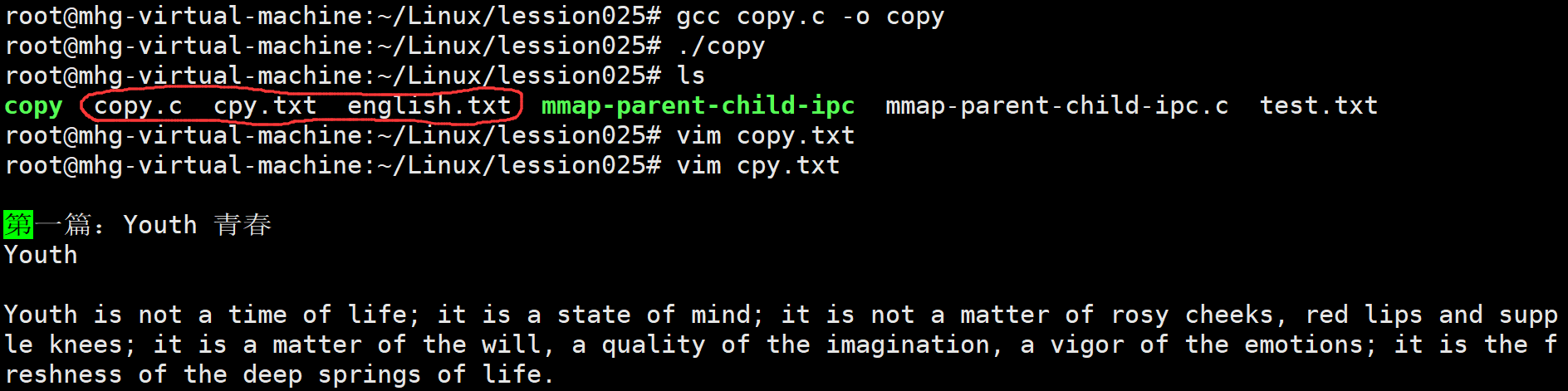

【Linux】内存映射

目录 内存映射相关函数解析代码示例1(使用内存映射实现没有关系的进程间的通信):代码示例2(使用内存映射实现文件间拷贝):匿名内存映射 橙色

内存映射

内存映射(Memory-mapped I/o)是将磁盘文件的数据映射…

GitLabRunner安装部署

实战:GitLabRunner安装部署-2023.4.26(安装成功) 目录 实验环境

gitlab/gitlab-ce:15.0.3-ce.0

gitlab-runner-15.0.1-1.x86_64.rpm实验软件

链接:https://pan.baidu.com/s/10aL_kWzDKnZXBXG3-hS2tA 提取码:0820 2023.4.26-实战:…