0 前言

最近在学习SPI,刚开始接触四种mode的时候,还有点懵,也是搜了好几个博客,才算搞懂,特此记录下,防止下次又要翻好几篇博客才找到答案 >_<

1 四种mode的组成单元

这四种mode是由时钟极性和时钟相位组成,2 bits数据刚好组成4种情况,

-

时钟极性CPOL(Clock POLarity):即SPI空闲时,时钟信号SCLK的电平

- 0:空闲时低电平

- 1:空闲时高电平

-

时钟相位CPHA(Clock PHAse):即SPI在SCLK第几个边沿采样数据

- 0:第一个边沿

- 1:第二个边沿

时钟极性就不多说了,描述的很清楚了

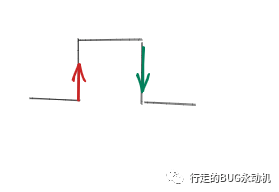

时钟相位中说的第一个边沿和第二边沿是这样理解的,简单画一个clk信号,如下图

从图中可以看到,这个clk有两个边沿,红色的上升沿,和绿色的下降沿

从左往右看去,第一个边沿是上升沿(红色),第二个边沿是下降沿(绿色),所以在这种情况下

-

CPHA = 0,表示在

clk上升沿采样 -

CPHA = 1,表示在

clk下降沿采样 -

采样:在时钟沿到来前,master和slave数据必须在MISO/MOSI线上准备好

-

发送:在另一个时钟沿,master和slave将准备好的数据

2 四种mode

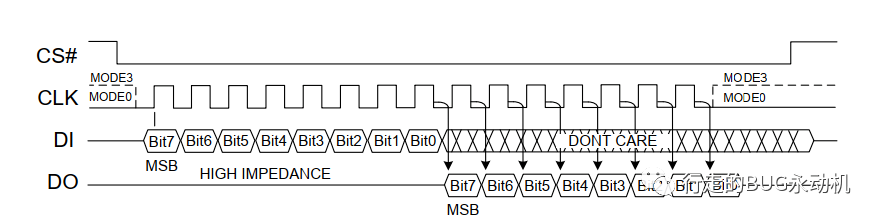

很多介绍spi四种mode时用的都是下面这种图,虽然简洁,但不利于新手理解(别问我是怎么知道的)

列个表给出四种mode

| CPOL | CPHA | |

|---|---|---|

| 0 | 0 | mode 0 |

| 0 | 1 | mode 1 |

| 1 | 0 | mode 2 |

| 1 | 1 | mode 3 |

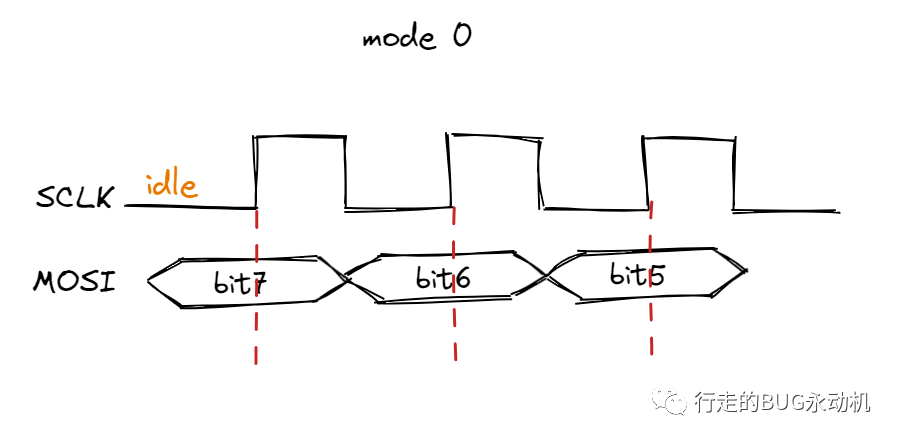

2.1 mode 0

mode 0表示:空闲的时候是低电平,在上升沿采样,如下图所示,在红色虚线处采样

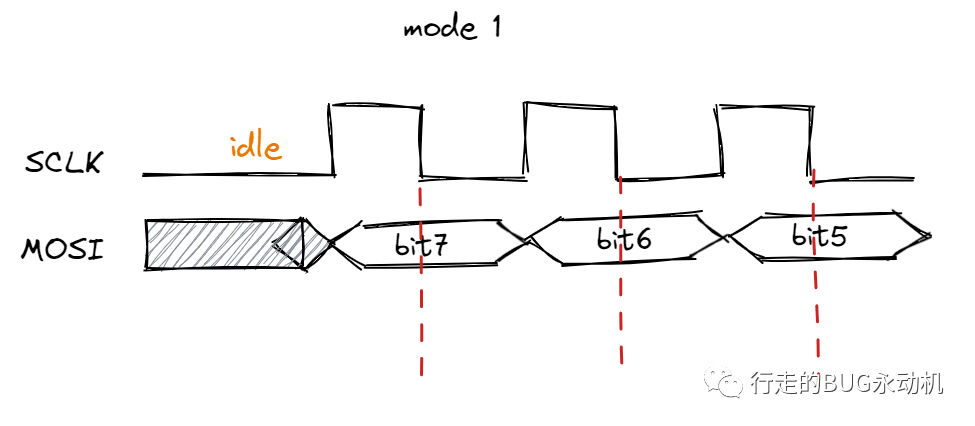

2.2 mode 1

mode 1表示:空闲的时候是低电平,在下降沿采样,如下图所示,在红色虚线处采样

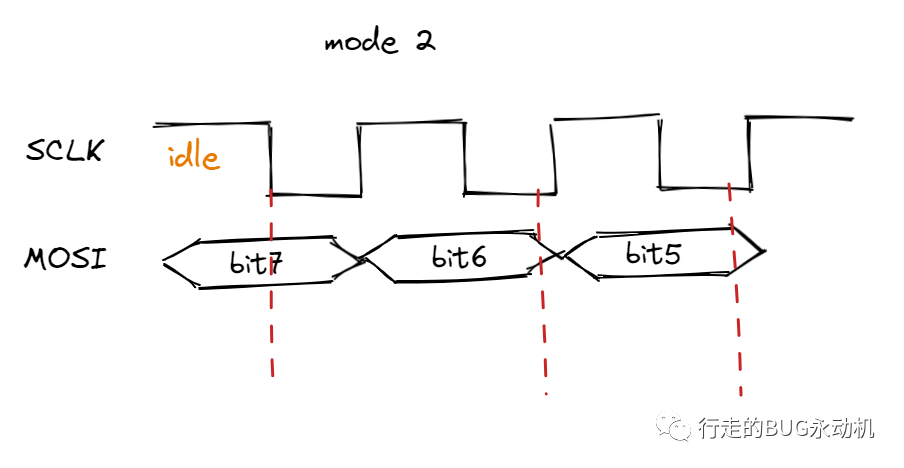

2.3 mode 2

mode 2表示:空闲时是高电平,在下降沿采样,如下图所示,在红色虚线处采样

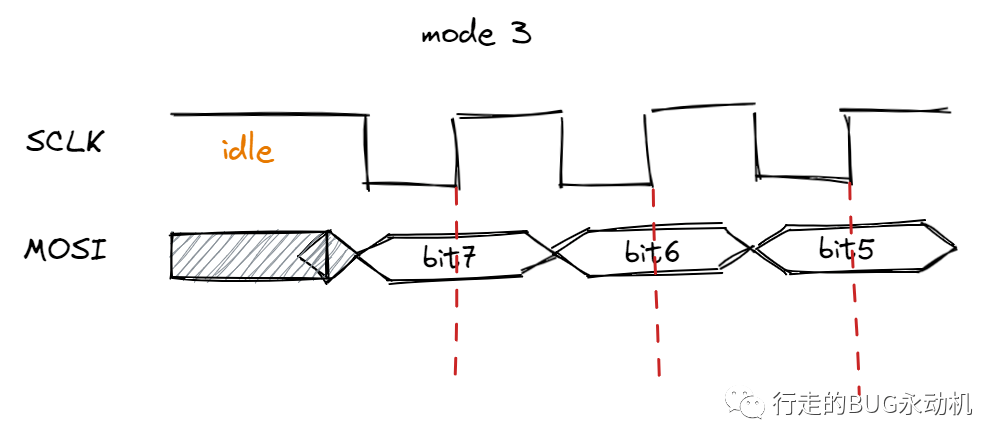

2.4 mode 3

mode 3表示:空闲的时候是高电平,在上升沿采样,如下图所示,在红色虚线处采样