一、基础知识

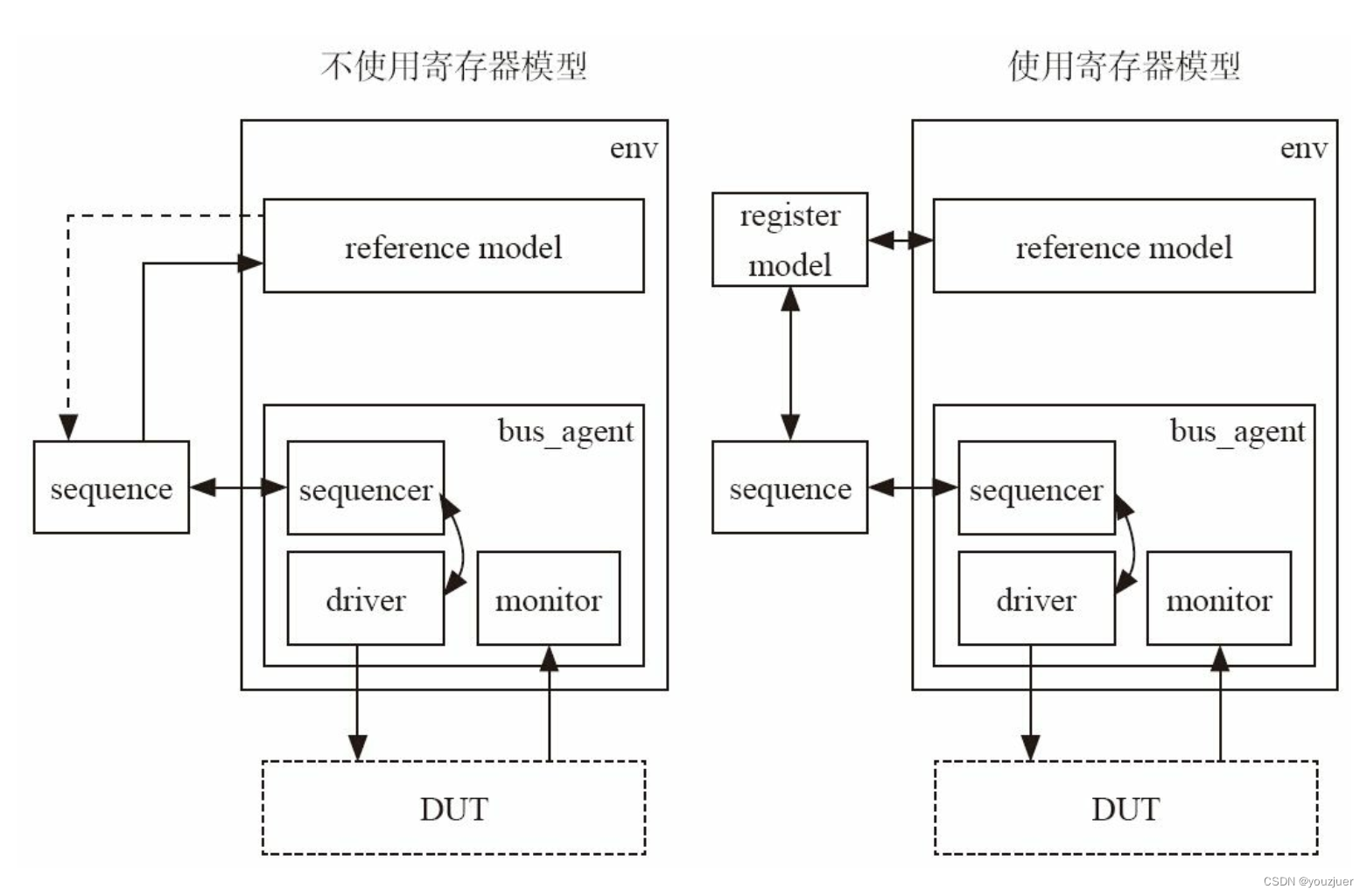

前门访问与后门访问是两种寄存器的访问方式。 所谓前门访问, 指的是通过模拟cpu在总线上发出读指令, 进行读写操作。 在这个过程中, 仿真时间( $time函数得到的时间) 是一直往前走的。而后门访问是与前门访问相对的概念。 它并不通过总线进行读写操作, 而是直接通过层次化的引用来改变寄存器的值。

目的:

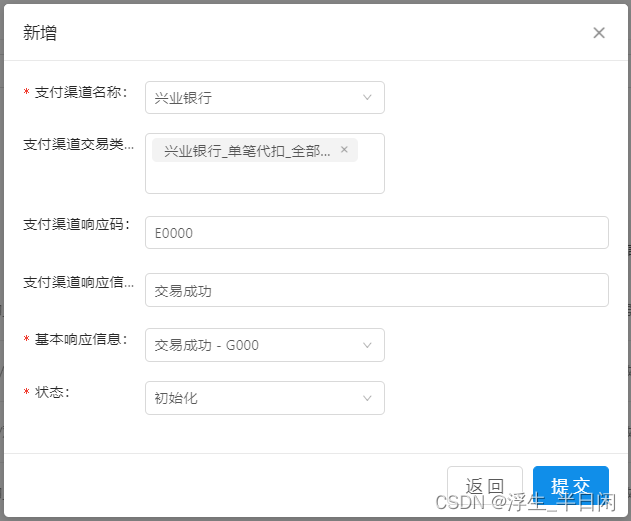

UVM寄存器模型的本质就是重新定义了验证平台与DUT的寄存器接口, 使验证人员更好地组织及配置寄存器, 简化流程、 减少工作量。

数据类型:

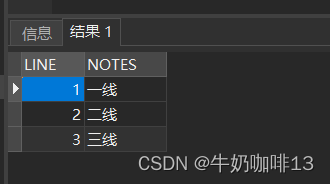

从小到大:uvm_reg_field < uvm_reg < uvm_reg_block < uvm_reg_map

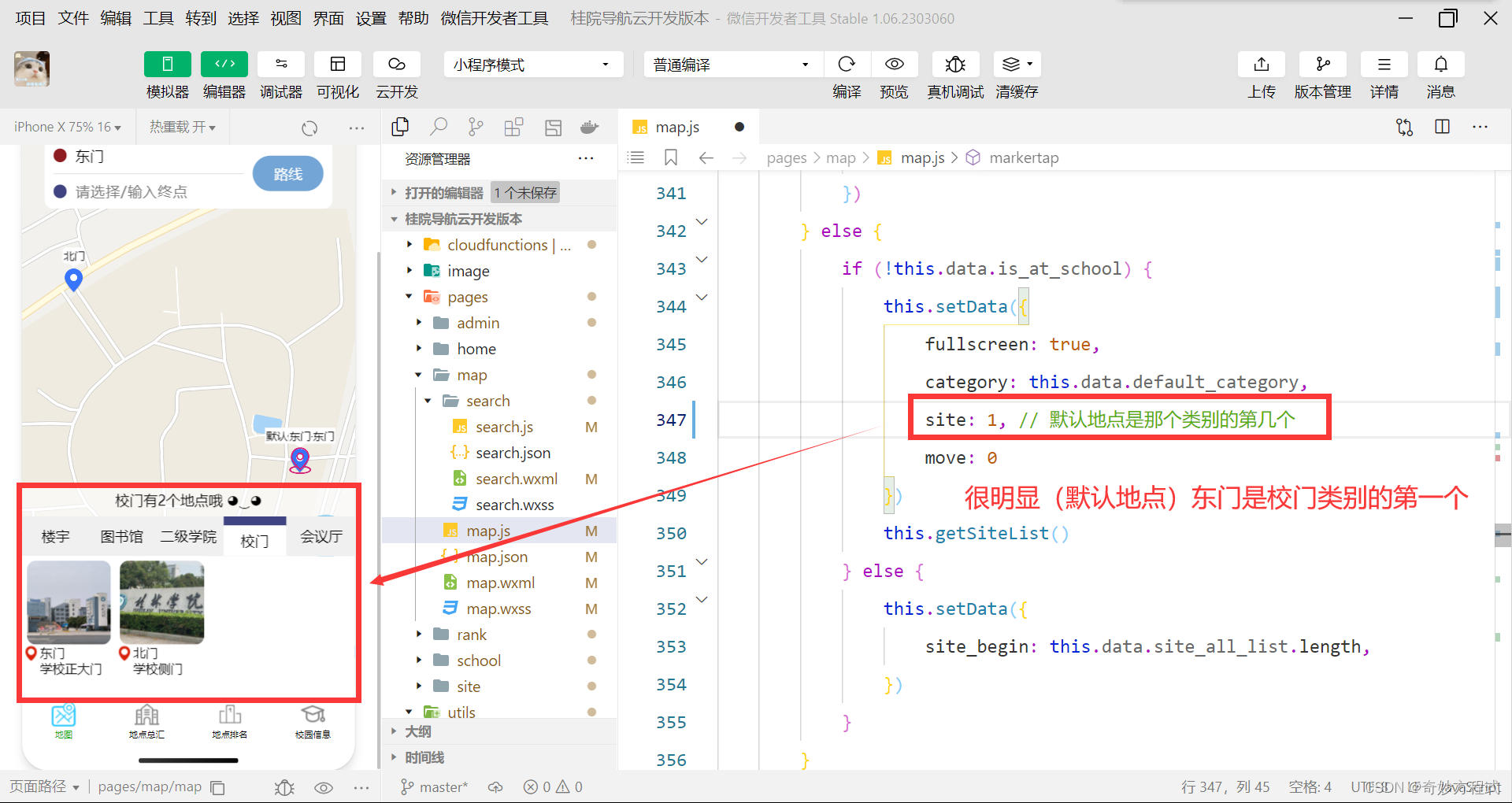

对于map来说(跟寄存器地址有关):

每个寄存器在加入寄存器模型时都有其地址, uvm_reg_map就是存储这些地址, 并将其转换成可以访问的物理地址( 因为加入寄存器模型中的寄存器地址一般都是偏移地址, 而不是绝对地址) 。 当寄存器模型使用前门访问方式来实现读或写操作时, uvm_reg_map就会将地址转换成绝对地址, 启动一个读或写的sequence, 并将读或写的结果返回。 在每个reg_block内部, 至少有一个( 通常也只有一个) uvm_reg