你的第一个基于Vivado的FPGA开发流程实践——二选一多路器

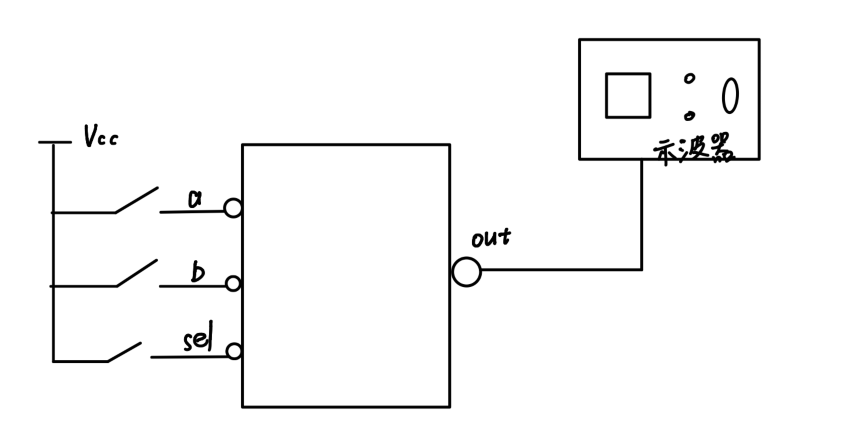

1 原理图

2 开发流程

- 首先我们先打开安装好的Vivado软件

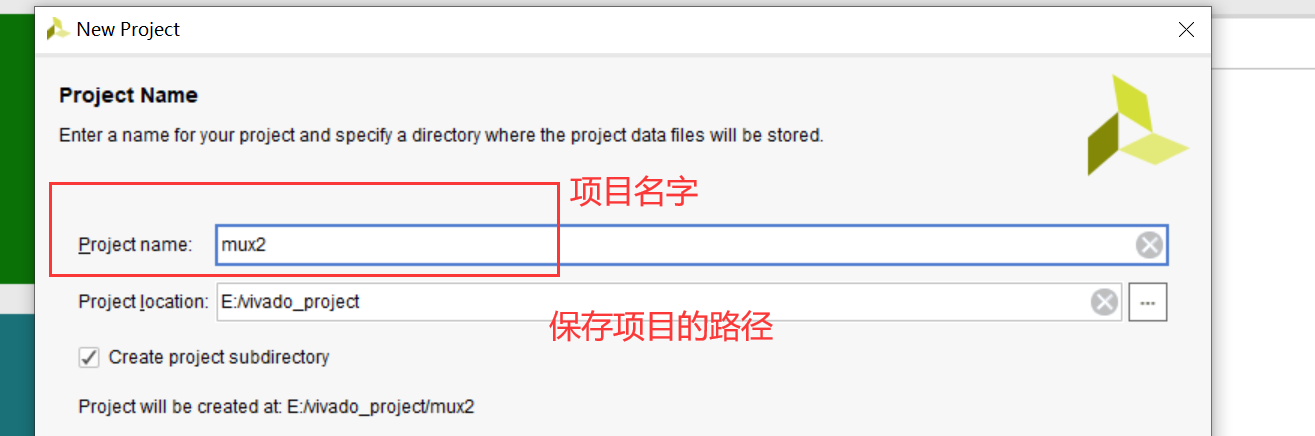

- 创建一个文件

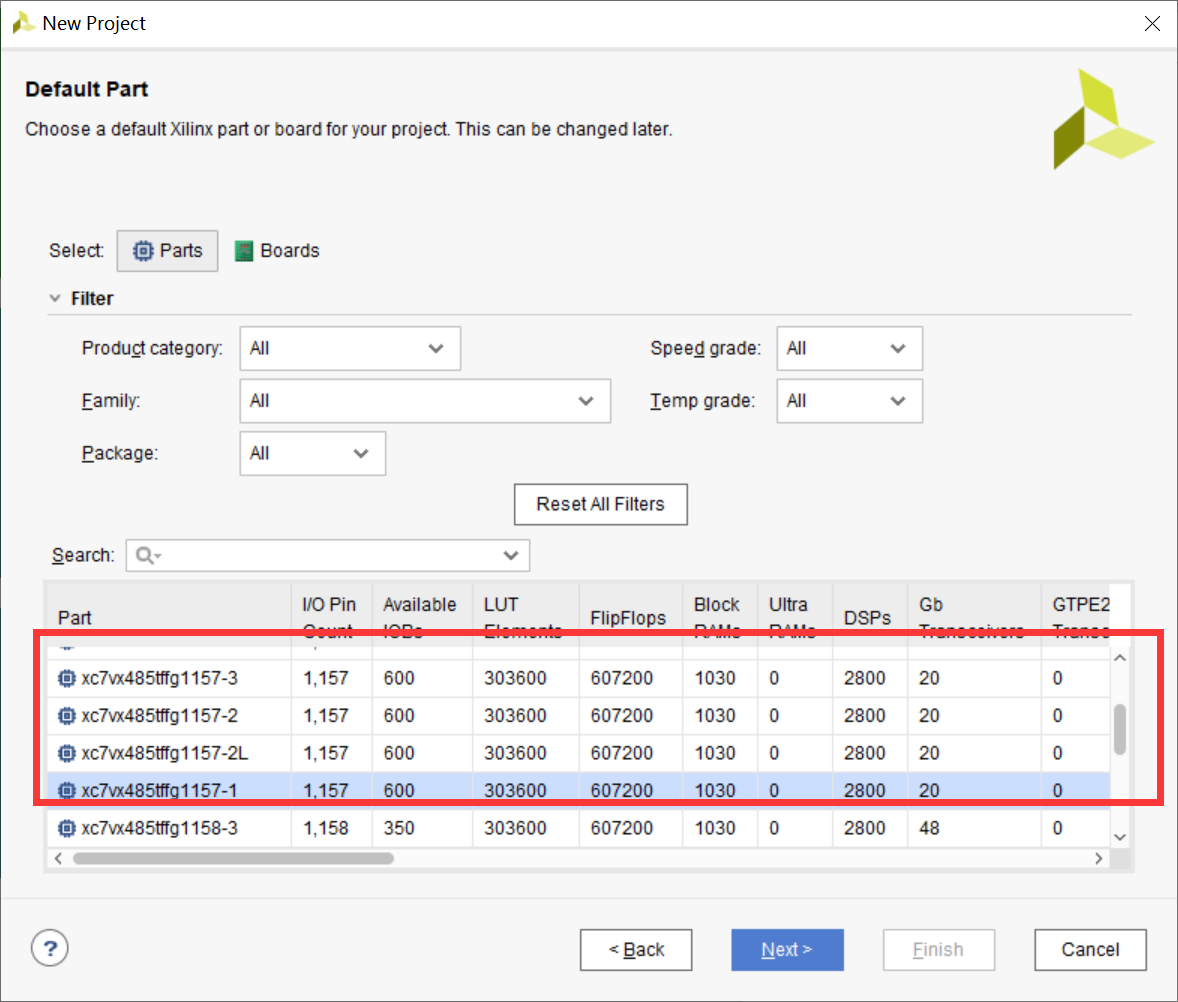

- 选择你的开发板

- 创建一个源文件

现在我们就可以根据原理使用Verilog代码实验这个功能了

module mux2( //端口列表

a,

b,

sel,

out

);

//交代端口类型

input a;

input b;

input sel;

output out;

//赋值

assign out = (sel==1)?a:b;

endmodule

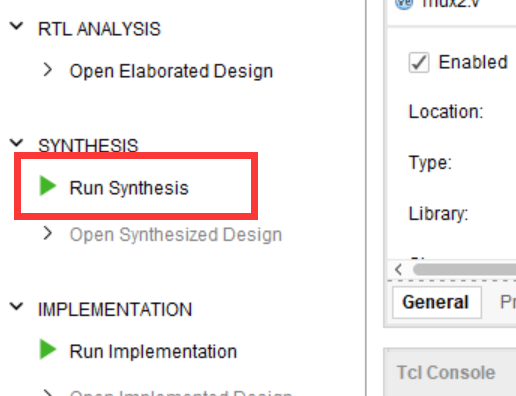

- 运行综合(Run Synthesis)

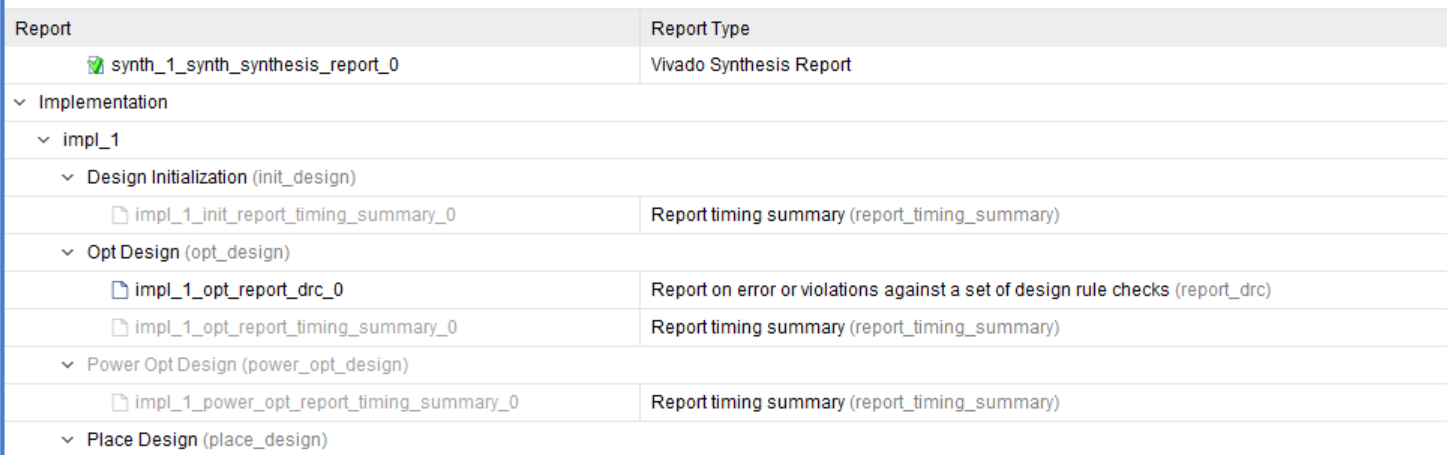

- 然后我们可以观察一下综合运行完生成的report

这里可以看出没什么问题,没有报错

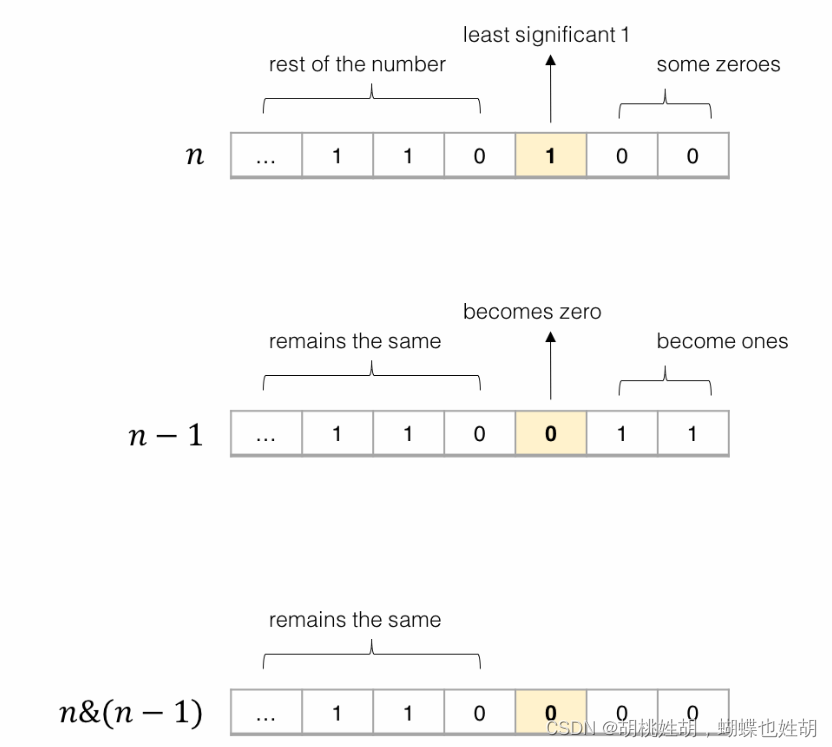

- 仿真的意义

首先我们需要用一张图说明仿真测试的原理/意义

现在开始编写仿真代码,我们首先要知道的是

a、b、sel 共有8组取值,分别是

| a | b | sel |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

| 1 | 1 | 1 |

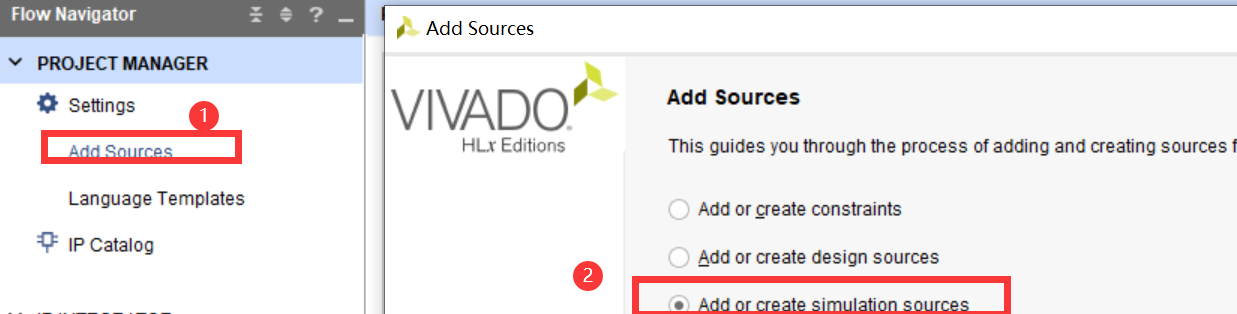

- 创建仿真文件

- 仿真代码

`timescale 1ns / 1ps

module mux2_tb(

//仿真中括号里不用写端口

);

//定义仿真文件中的变量

//输入

reg a;

reg b;

reg sel;

//输出

wire out;

mux2 UUT( //相当于把源文件的变量映射(例化)到仿真文件,mux2是源文件的名字,必须一致

.a(a), //源文件的a 对应到 仿真文件 是 a

.b(b),

.sel(sel),

.out(out)

);

initial begin

a=0;b=0;sel=0;

#200; //延迟200ns

a=0;b=0;sel=1;

#200; //延迟200ns

a=0;b=1;sel=0;

#200; //延迟200ns

a=0;b=1;sel=1;

#200; //延迟200ns

a=1;b=0;sel=0;

#200; //延迟200ns

a=1;b=0;sel=1;

#200; //延迟200ns

a=1;b=1;sel=0;

#200; //延迟200ns

a=1;b=1;sel=1;

#200; //延迟200ns

end

endmodule

- 功能仿真

我们可以根据左边的这些值 判断功能是否能达成

- 布局布线/运行实现(Run Implementation)

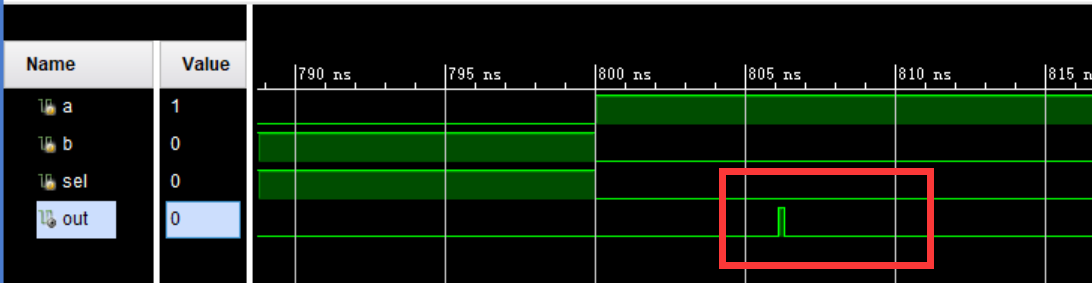

- 时序仿真——要在布局布线之后

通过时序仿真我们可以看到 out的变化滞后于信号的变化,这说明out的变化是有一定延迟的,这是合理的

我们还能看到毛刺,原理是(a、b、sel都在变,只要某一次变化中,其中一个的变化优先于另外两个,就会有毛刺)

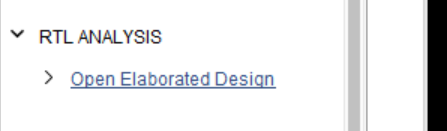

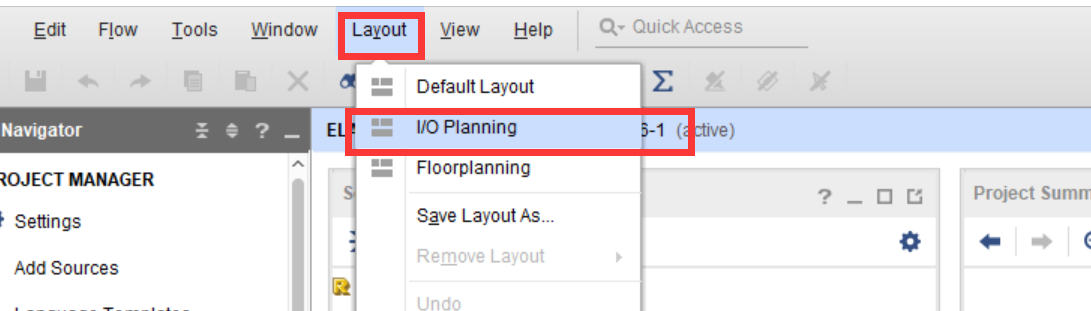

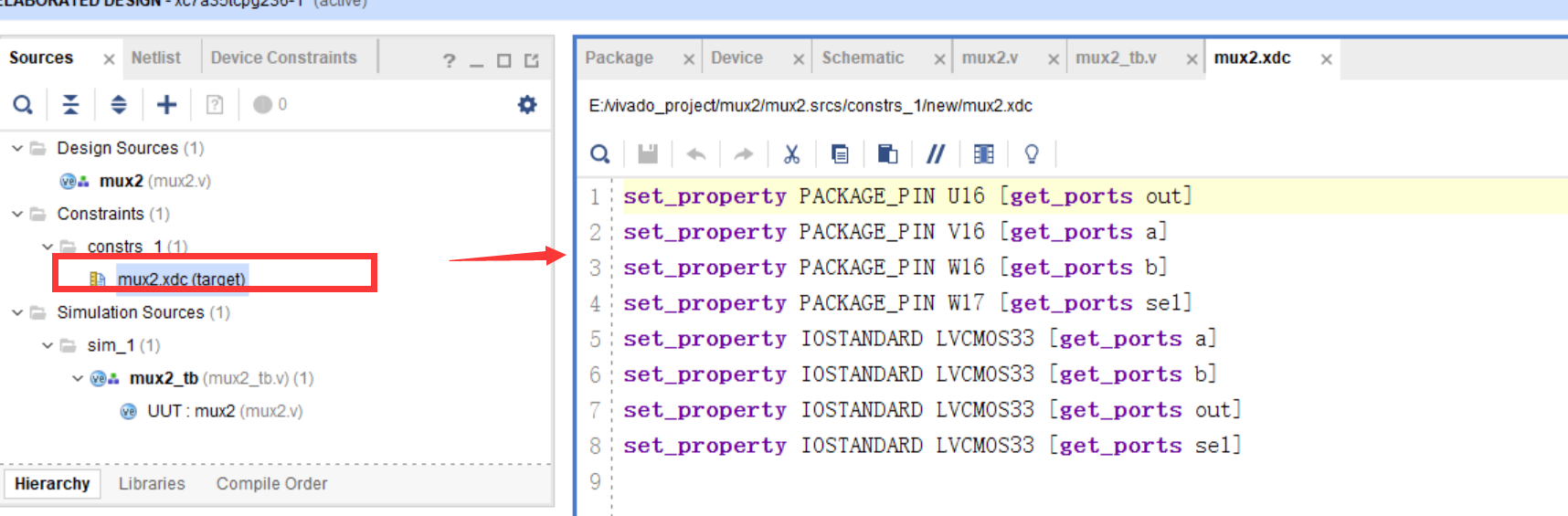

- 分配管脚

首先open设计

然后分配

选择合适的管脚(要看板子)

然后ctrl+s 保存管脚约束文件

就生成了这样的约束文件

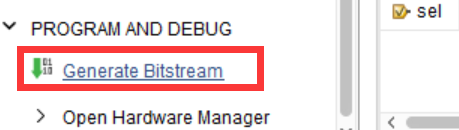

- 创建bit流文件

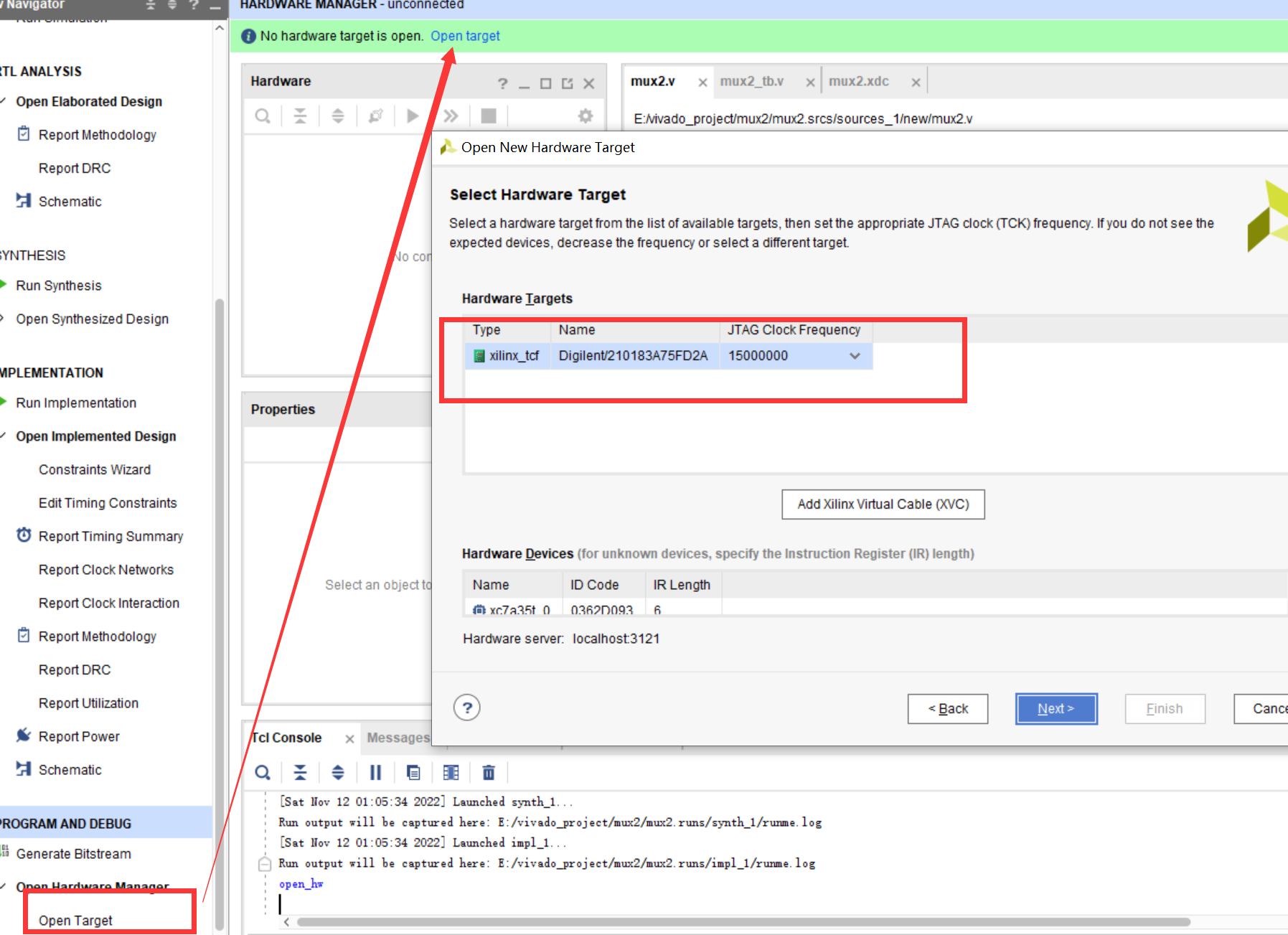

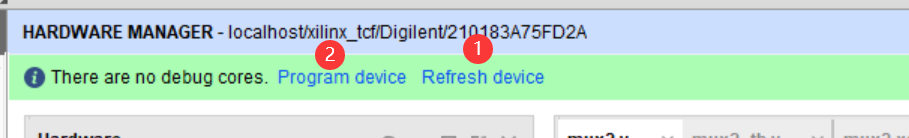

- 下载文件到板子

首先连接板子到电脑

然后refresh device 再 program device

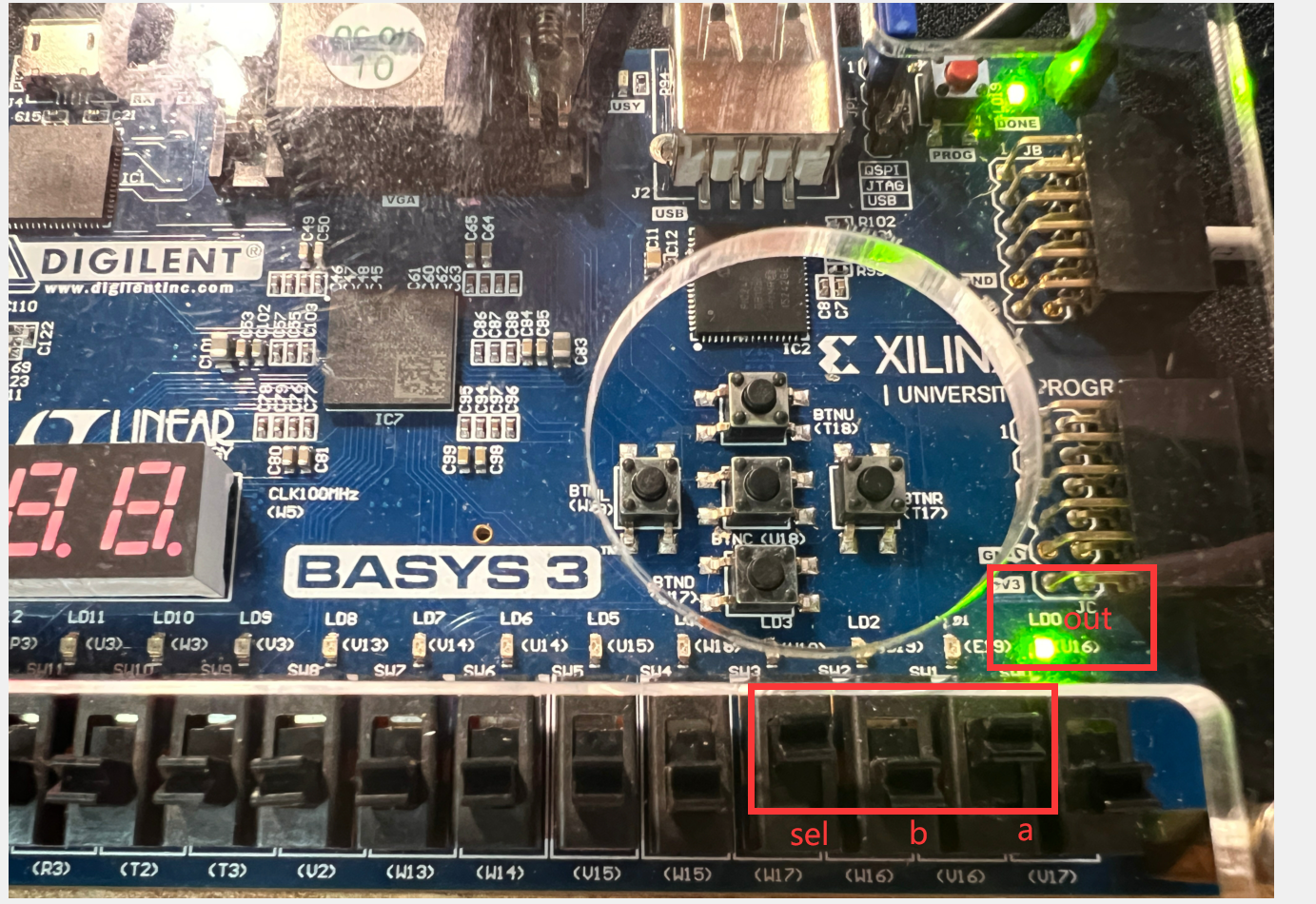

- 检验

图中展示的为 sel = 1 ,a = 1的情况 (out = a = 1 灯亮)

![[TCP/IP] Linux 搭建服务器局域网](https://img-blog.csdnimg.cn/5525d683a64a4d0085fc13319ef127d0.png#pic_center)