1.secondary pg pin的作用

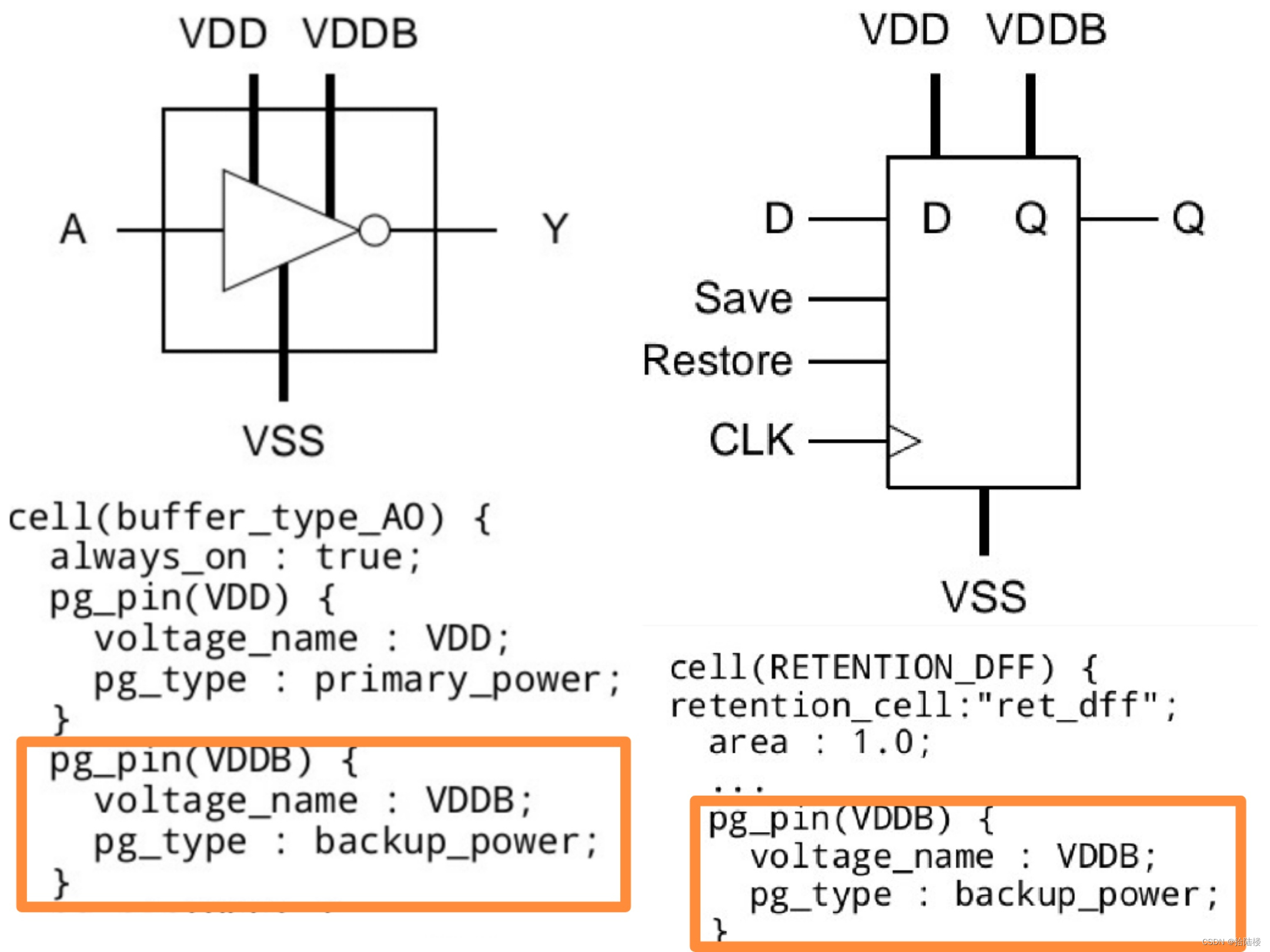

1) 作为备用电源(backup power),当主供电(primary power)断电后,让standard cell仍能保持正常运行或者至少保持输出不变,比如always on buf和retention reg。

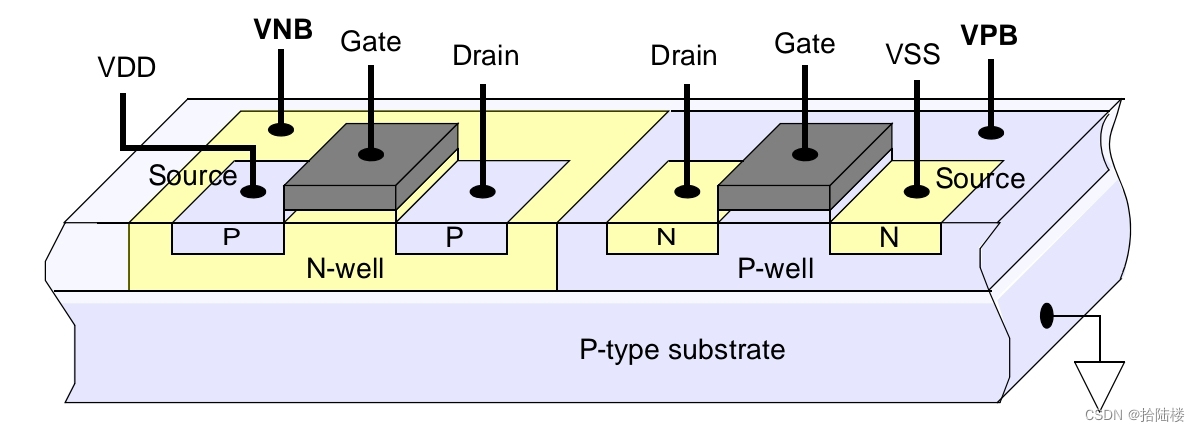

2)作为偏置阱电位(bias pin),与mos管源、漏极接不同电源,例如在可关断的power domain中,需要阱电位相对于供电电源来说始终处于always on的状态,这样standard cell的上电掉电都不会受影响,常见于带bias pin的tap cell。

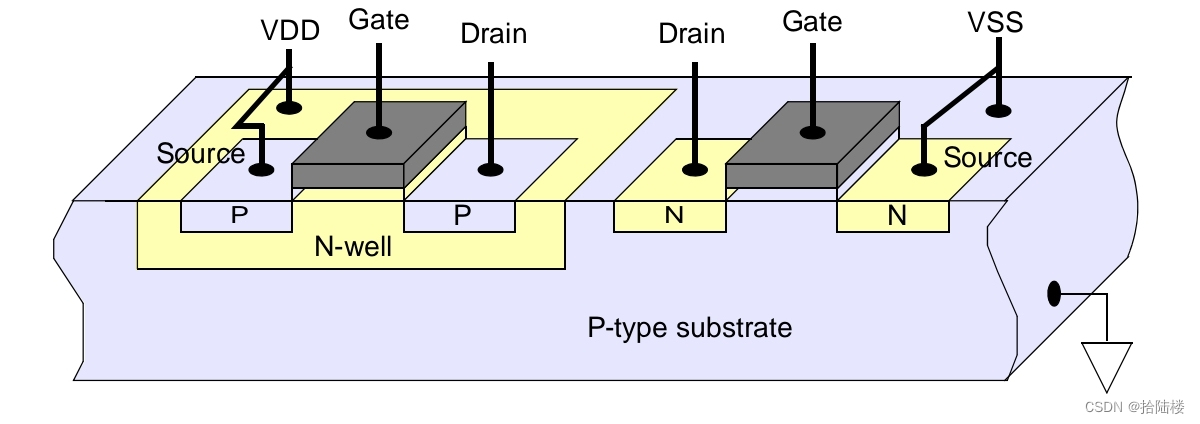

cmos管为四端器件(漏、栅、源、衬),一般情况下源(source)漏(drain)都是接衬底(nwell或p-sub),如下图例。

当然,衬底接偏置,不接源漏也是可以的,如下图例,通过改变衬底偏置电压可以控制mos管的开启关断的转换速度(与leakage power互相掣肘)。

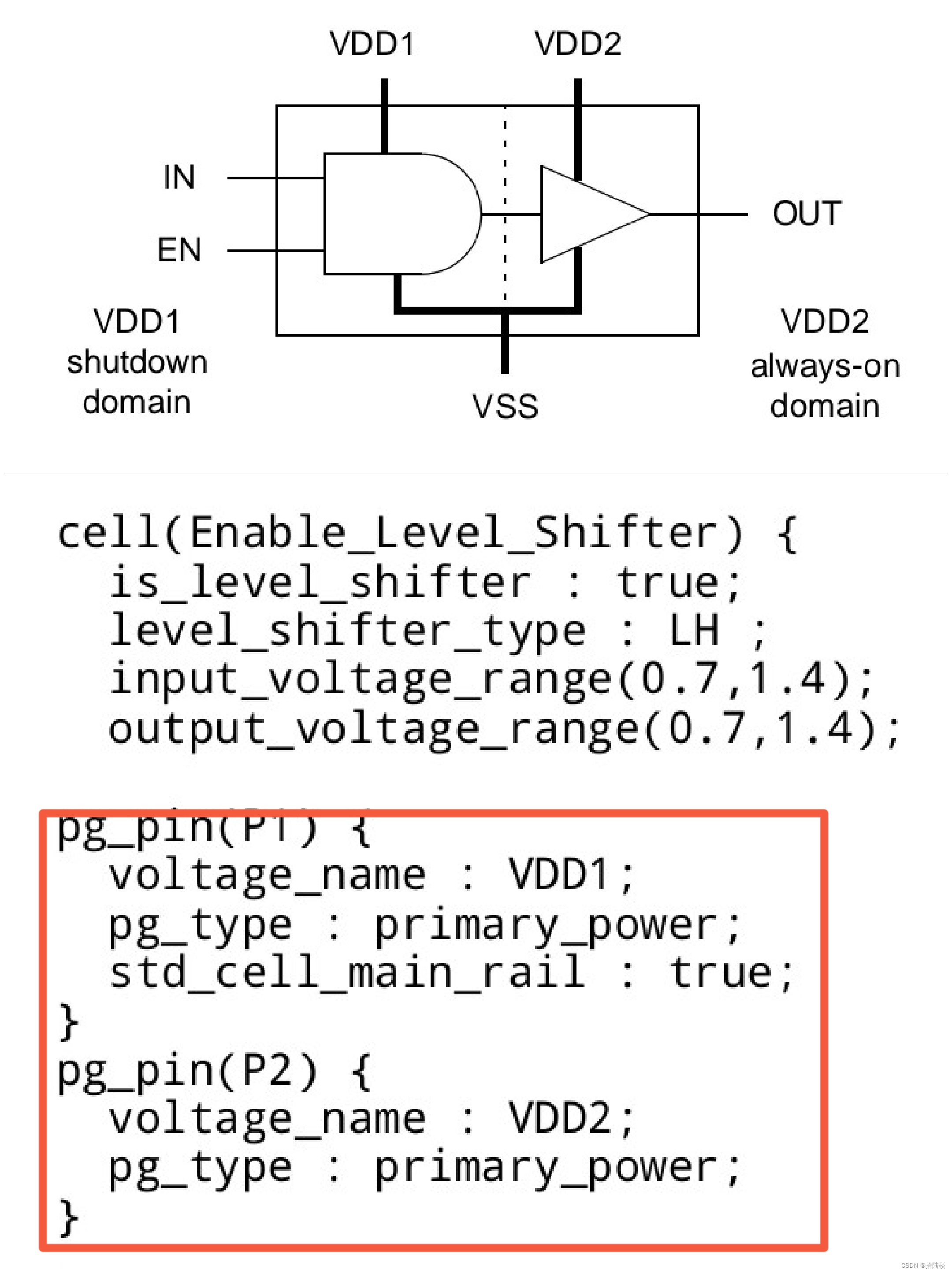

3)作为主电源(primary pin),负责standard cell正常工作中一部分电路的供电,比如level shifter。

2.secondary pg pin的连接

1) secondary power rail

在power plan阶段,针对secondary pg pin拉一条power rail,这种方法供电是最好的,缺点是同一row上其他类型cell放进去容易有drc,常用在level shifter上。

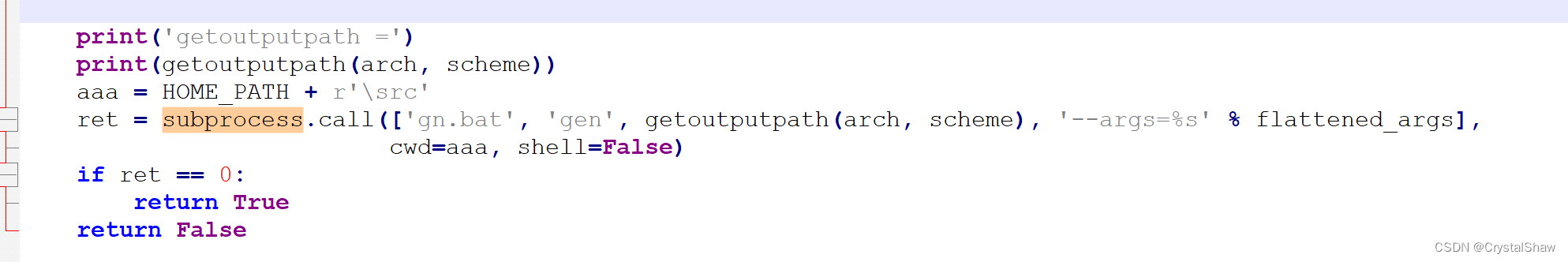

2)preroute

在preroute阶段,使用ndr rule绕线到power mesh上,这种方法使用居多。

set_app_options -name route.common.number_of_secondary_pg_pin_connections -value 50

connect_pg_net -net VDD [get_flat_pins -all */VNW]

set_routing_rule [get_nets VDD] -default_rule (-rule 2w2s)-max_routing_layer ME6 -max_layer_mode hard

route_group -nets VDD

3)signal route

使用signal route的方式绕线,连线比较乱,不推荐,应用场景上,有时候secondary pg pin的"is_secondary_pg"属性为false,ICC2里是无法改的,只能重新做ndm,其中一种方法是把secondary pg pin在LEF中改成“USE SIGNAL”,此时这个cell在ICC2中就不再是physical only的cell了,不过这种情况下更推荐另一种方法,在重做ndm时设置以下属性:

set_attribute [get_lib_pins */YAPCELL/VNW] is_secondary_pg true

set_attribute [get_lib_pins */TAPCELL/VNW] port_type nwell;#这里以tap cell为例

在绕线以后需要检查secondary pg pin的连接情况,一方面检查floating(check_pg_connectivity),一方面检查是否有绕线太长,再决定调整设置或者补power。

![[附源码]计算机毕业设计springboot软考刷题小程序](https://img-blog.csdnimg.cn/fb3d8bed9fd749edb1bfb20ebc6d4bf1.png)

![[附源码]Python计算机毕业设计Django电子相册管理系统](https://img-blog.csdnimg.cn/d3ad9bd6b6b54007ace2b9f776e4ca8d.png)

![[附源码]Python计算机毕业设计Django高校后勤保障系统](https://img-blog.csdnimg.cn/8d90f89c48124768b2cb8a1cbda4914d.png)