1 VHDL基本结构

1 实体 Entity:描述所设计的系统的外部接口信号,定义电路设计中所有的输入和输出端口

2 结构体 Architecture:描述系统内部的结构和行为

3 包集合 package:存放各设模块能共享的数据类型、常数和子程序等;

4 配置 configuration:指定实体所对应的结构体

5 库 library:存放已经编译的实体、结构体、包集合和配置

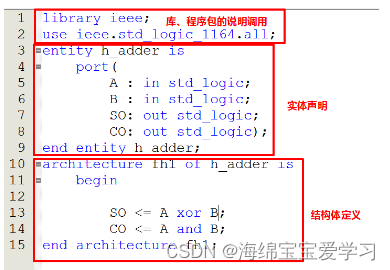

VHDL的基本设计的基本设计单元结构:程序包说明、实体说明和结构体说明三部分:

1.1 实体 Entity

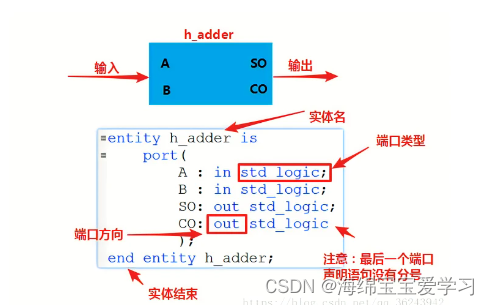

实体描述了设计单元的输入输出接口信号或引脚,是设计实体经封装后对外的一个通信界面。

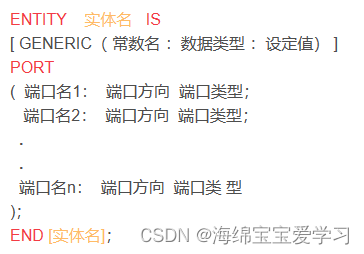

定义方式:

注意:实体名由设计者自由命名,用来表示倍设计电路芯片的名称,但是必须与VHDL程序的文件名称相同。要与文件名一致

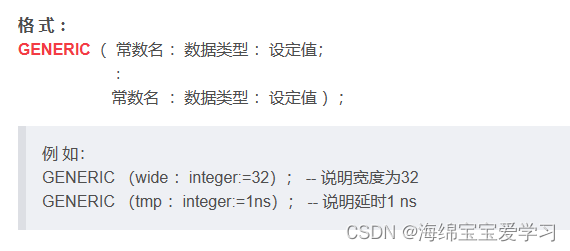

类属说明

类属为设计实体与外界通信的静态信息提供通道,用来规定端口的大小、实体中子元件的数目和实体的定时特性等

2 结构体

结构体定义了设计单元具有的功能,描述了该基本设计单元的行为、元件和内部的连接关系;

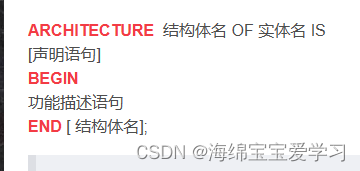

定义方式:

提示:

- 声明语句的作用:用于声明该结构体将用到的信号、数据类型、常熟、子程序和元件等。声明的内容是局部的。

- 功能描述语句:具有描述结构体的功能和行为。

一个实体可对应多个结构体,每个结构体代表该实体功能的不同实现方案或不同实现方式。同一时刻只有一个结构体起作用,通过configuration 决定用哪个结构体进行仿真或综合。

在结构体描述中,具体给出了输入、输出信号之间的逻辑关系。

3 VHDL语句

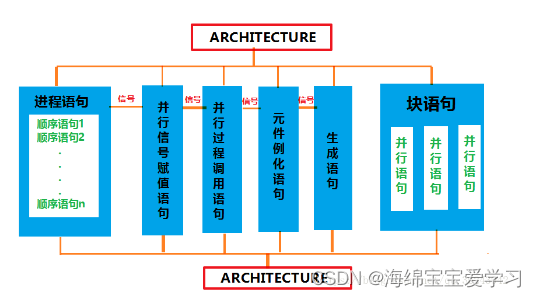

3.1 并行语句

在结构体中的执行是同时进行,执行顺序与书写顺序无关。如下图所示:

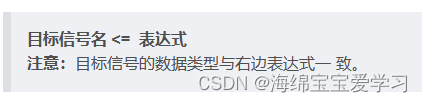

并行信号赋值

- 简单赋值语句

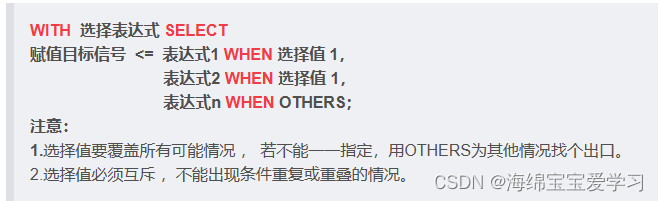

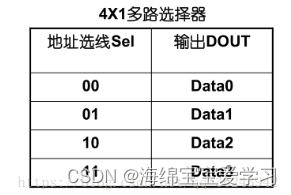

- 选择信号赋值语句

例子:

实现一个四乘一多路选择器,当选择信号为00 则输出信号为data0的数据,选择为01输出data1的信号,一次类推;

程序如下:

library ieee:

use ieee.std_logic_1164.all;

entity mux is

port(

data0,data1,data2,data3: in std_logic_vector(7 downto 0);

sel : IN std_logic_vector(1 downto 0);

dout: out std_logic_vector(7 downto 0);

);

end;

architecture dataflow of mux is

begin

with sel select

dout <= data0 when "00",

data1 when "01",

data2 when "10",

data3 when "11",

"00000000" when others;

end

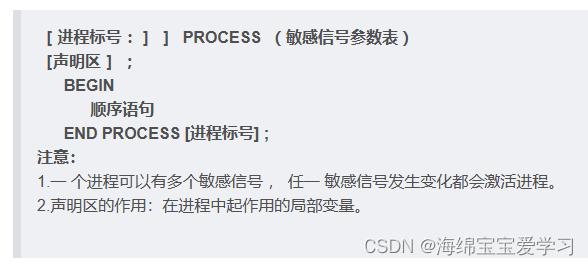

3.2 进程语句

进程语句定义顺序语句模块,用于将从外部获得的信号值,或内部的运算数据向其他的信号进行赋值。

- 进程本身是并行语句,但内部是顺序语句

- 进程只有在特定的时刻(敏感信号发生变化)才会被激活。

例子1:

把clock设为敏感信号,当clock上升沿时,输出时钟就进行取反一次。

程序如下:

library ieee;

use ieee.std_logic_1164.all

entity FreDevider is

port

(

Clock: in std_logic;

Clkout: out std_logic

);

end;

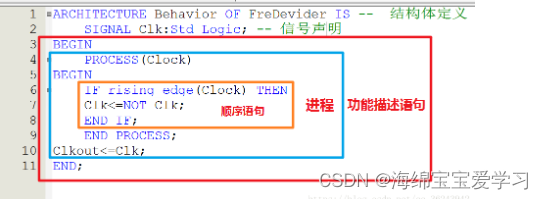

architecture Behavior of FreDevider is

Signal Clk:std_logic;

begin

process(C)

end

例子2:

本例子做一个自加器,每遇到一个clock的上升沿,num就自加1,加到3就自动清零,重新开始,循环及进行,还有一个复位按钮,只要检测是reset的值为1,num的数值就清零,重新开始计数。

代码如下:

library ieee;

use ieee.std_logic_1164.all;

entity Counter is

port(

reset: in std_logic; // 异步时钟复位信号

clock: in std_logic; // 时钟信号

num : buffer integer range 0 to 3

);

end;

architecture Behavior of counter is

begin

process(reset,clock)

begin

if reset="1" THEN

num <= 0;

elsif rising_edge(clock) THEN

if num = 3 THEN

num <= 0;

else

num <= num + 1;

end if;

end if;

end process;

end;

end;

进程的启动:

当process的敏感信号参数表中没有列出任何敏感信号时,进程通过wait语句启动;

例子:

architecture behavior of state is

begin

process -- 敏感信号列表为空

begin

wait until clock; -- 等待clock激活进程

if(drive = '1') then

case output is

when s1 => output <= s2;

when s2 => output <= s3;

when s3 => output <= s4;

when s4 => output <= s1;

end case;

end if;

end process;

end

end

进程的注意事项

1 进程本身是并行语句,但内部为顺序语句

2 进程在敏感信号发生变化时被激活,在使用了敏感表的进程中不能含 wait语句;

3 同一进程中对同一信号多次赋值,只有最后一次生效

4 在不同进程中,不可对同一信号进行赋值

5 一个进程不可同时对时钟上下沿敏感。

6 进程中的信号赋值在进程挂起时生效的,而变量赋值是即时生效的。

7 相对于结构体而言,信号具有全局性,是进程间进行并行联系的重要途经

8 进程为综合器支持,且其建模方式直接影响仿真和综合结果,综合后对应宇进程的硬件结构对进程中所有可读入信号都是敏感的。