概述

芯片的2 个SPI 接口模块SPI1 和SPI2,可配置为主设备或从设备,实现与外部的SPI 通信。

特点:

⚫ 全双工3线串行同步收发

⚫ 2路独立通道

⚫ 主从模式

⚫ 可编程时钟极性和相位

⚫ 可编程比特速率

⚫ 从模式最大频率为FAHBCLK/2

⚫ 传输结束中断标志

⚫ 写冲突错标志

⚫ 主模式错误检测、保护和中断标志

⚫ 支持DMA

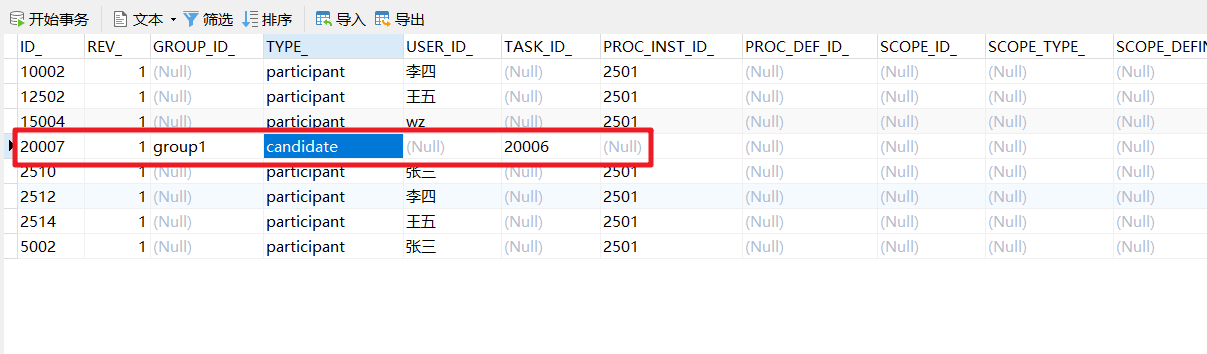

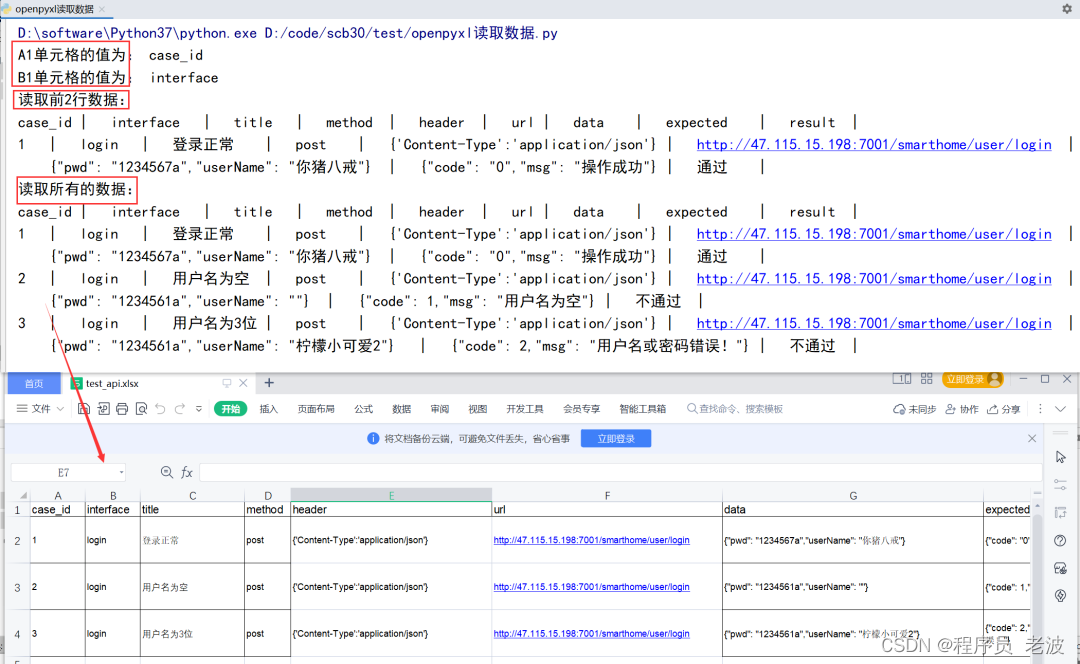

结构框图

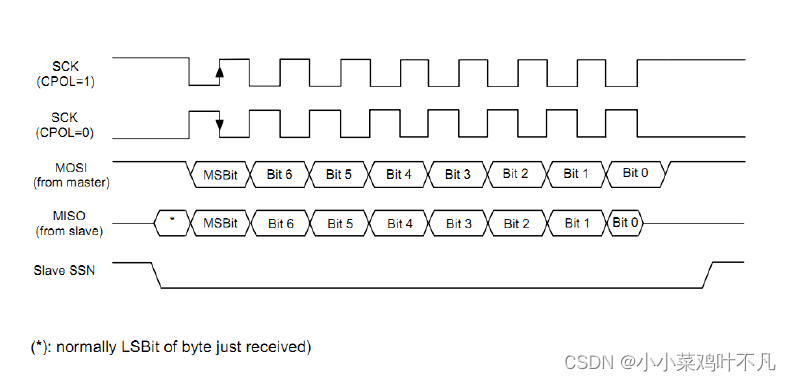

接口时序

为了兼容不同的SPI 外设, SPI 串行时钟的时序可以通过时钟相位选择位( SPCR.CPHA )和时钟极性选择位 (SPCR. 设置产生 4 种不同组合。为保证数据正确传输,主从器件的时序配置必需一致。当处于从器件模式或 SPI 系统使能位( SPCR.SPE )位为 0 时, SPI 的 SCK 引脚无串行时钟输出。

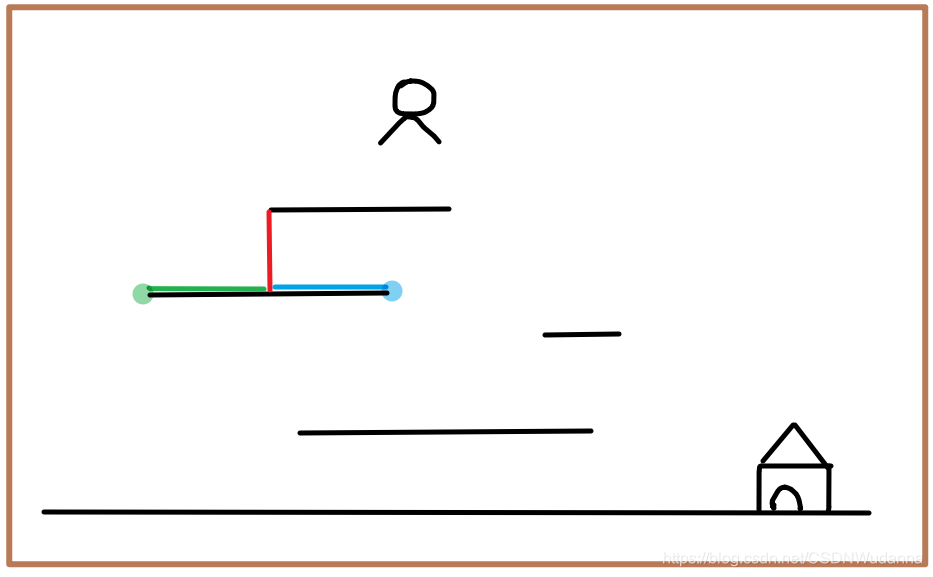

CPHA=0

CPHA=0时, SPI 模块在串行时钟的第一个跳变沿采样数据,即:

若CPOL=1 ,在串行时钟的下降沿采样数据

若CPOL=0 ,在串行时钟的上升沿采样数据。如图所示:

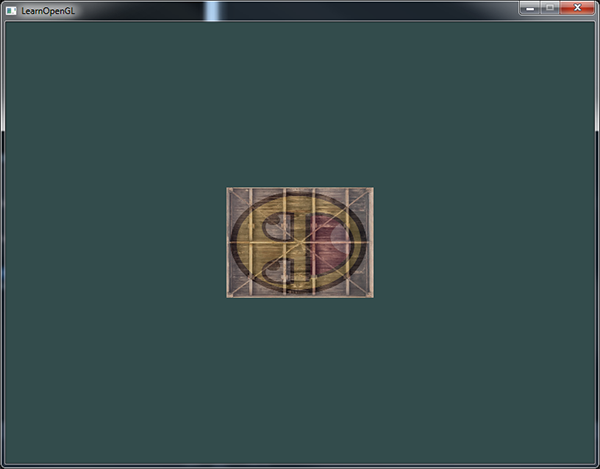

CPHA=1

CPHA=1时, SPI 模块在串行时钟的第二个跳变沿采样数据,即:

若CPOL=1 ,在串行时钟的上升沿采样数据

若CPOL=0 ,在串行时钟的下降沿采样数据。如图所示: