文章简介

本系列文章主要针对FPGA初学者编写,包括FPGA的模块书写、基础语法、状态机、RAM、UART、SPI、VGA、以及功能验证等。将每一个知识点作为一个章节进行讲解,旨在更快速的提升初学者在FPGA开发方面的能力,每一个章节中都有针对性的代码书写以及代码的讲解,可作为读者参考。

第十一章:按键消抖

之前的章节讲解了呼吸灯、状态机、top-down 设计,本章将这些知识点进行串联起来,设计要求如下:

①在开发板上完成自动售货机的实验,投币的动作通过按键实现,当按1次按键(按下到抬起算一次),算作投币1次;

②按下一次按键,led 灯亮一个,按下两次按键后,led 灯亮两个,当按三次按键后,用呼吸灯充当出可乐的效果,呼吸灯持续十秒后熄灭,状态回到初始状态。

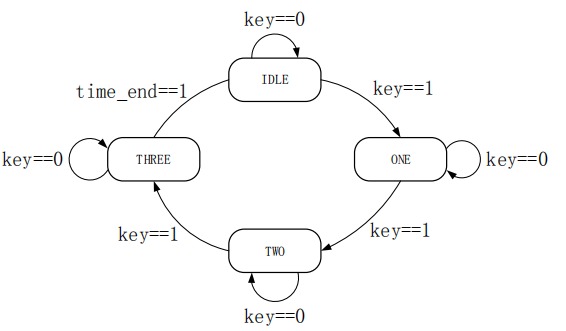

根据上面的要求,先画出对应的状态转移图如图 1 所示。

图 1 状态转移图

根据图 1 所示的状态转移图可以描述出该状态机,IDLE 状态、ONE 状 态、TWO 状态、THREE 状态的跳转条件均是 key(按键),THREE 状态进入 IDLE 状态的条件为十秒钟结束。在 IDLE 状态 led 灯全灭,ONE 状态 led 灯亮一个, TWO 状态 led 灯亮两个,THREE 状态 led 灯进入呼吸状态。

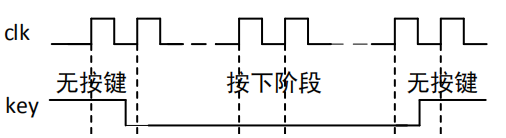

一般情况下,我们从按下按键到松开基本需要大于几十毫秒的时间,系统时钟的周期处于纳秒级,因此我们按下一次按键会被大于十万个时钟的上升沿采集到,然而我们希望的是按下一次按键只被一次上升沿采集到,不然会被认为按了多次按键,所以我们需要对我们的按键进行处理。假设按键在没被按下时为高电平,被按下时处于低电平,如图 2 所示的波形图。

图 2 按键波形图

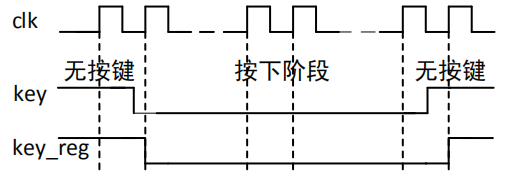

由图 2 分析可知在 key 被按下时有且仅有一个 key 的上升沿和一个 key 的下降沿,我们可以通过检测 key 的上升沿或者下降沿来确定按键被按下一次, 这就涉及到边缘检测,具体方法如图 3 所示,可以用 clk 的上升沿将 key 延时一 个周期产生 key_reg,通过 key 和 key_reg 的值同时判断 key 的上升沿或下降 沿。由图 3 可知,当用 clk 的上升沿检测到 key 等于 1 的同时 key_reg 等于 0, 此时则为 key 的上升沿,若 key 等于 0 的同时 key_reg 等于 1 则为 key 的下降 沿。

图 3 边缘检测

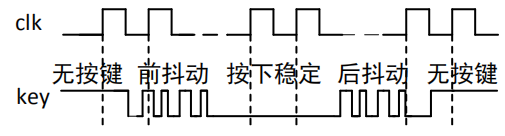

由图 3 可知根据 key 的上升沿或下降沿可确定按键按了一次,然而事实却不允许我们这么做。图 4 给出了一个按键的模型,当不按下按键 s 时,a、b 两点 是断开的,按下按键 s 时线路才接通,然而当按下按键时,会存在物理上的抖动现象,此时 a、b 两点会在断开和接通之间反复的一段时间,就会出现图 5 所 示的抖动、稳定的波形。

图 4 按键模型

图 5 按键抖动

图 5 所示前抖动为按下时产生的抖动,后抖动为按键松开时造成的抖动, 前、后抖动持续时间一般均为 5~10ms,在有抖动的情况下,key 会被 clk 上升沿采集到很多的上升沿和下降沿,因此用 key 的上升沿和下降沿判断按键一次就不成立了,我们需要寻找新的方法。

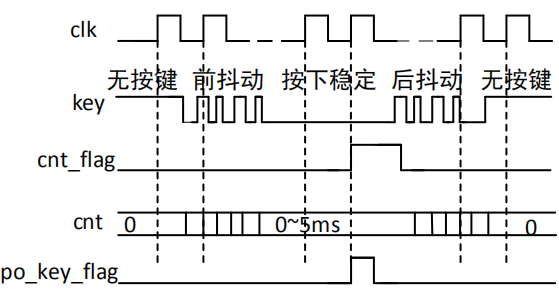

我们知道按键被按下时 key 值为低电平(0),在抖动期间 key 既有高电平也有低电平,我们可以使用 clk 的上升沿计算 key 连续为低电平的时间,期间当检 测到 key 为高电平时,则从头开始计数,当计数超过 5~10ms 时,我们可以认定按键有被按下的时候,此时我们可以产生一个 clk 周期为高电平的标志,当该标 志位高电平认为有一次按键即可,具体波形如图 6 所示。

图 6 按键消抖波形图

此处我们认为 key 值有连续性的 5ms 时为按键被按下,时钟周期为 50MHz, 即 20ns,可以算出 5ms 占 250000 个 clk 周期,也就是说 cnt 从 0 计数到 249999 为 5ms,当 cnt 等于 249999 时可以将 po_key_flag 拉高一个周期,由于按键时间长短无法确定,因此 cnt 有可能多次达到 249999 这个值,会造成 po_key_flag 多次被拉高,这样又会出现按下一次键被当成按下多次,所以在 图 6 中出现了 cnt_flag 变量,在遇到 cnt 等于 249999 时,cnt_flag 就会被置高,直到遇到 key 等于高电平时才会被拉低,这样我们就可以将第一个 cnt 等 于 249999 和后面的区分开,那么我们也可以用 cnt 和 cnt_flag 共同控制在一次按键中,保证 po_key_flag 有且仅有一个时钟周期的高电平。根据波形图可得到如下所示的代码。

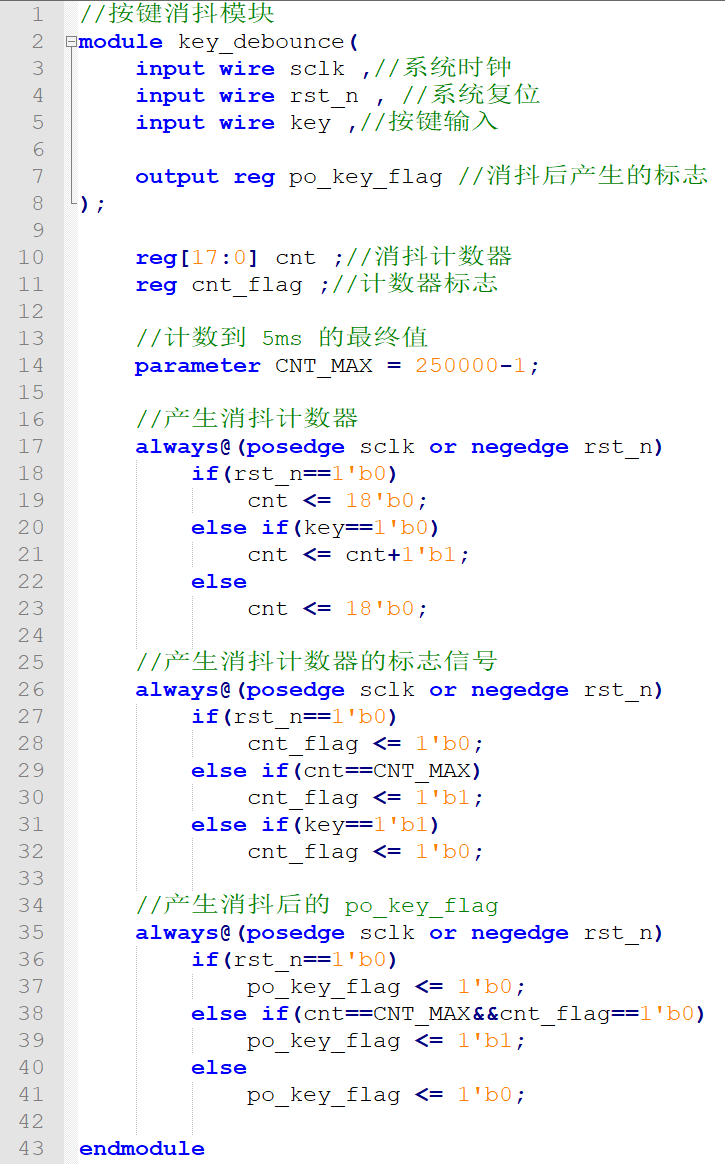

代码示例:

代码解析:

①第 17 行的 always 块实现了一个计数器,当 key 键按下(值为 0)的时候开始计数,当检测到按键松开(值为 1)的时候计数器归零,这样在抖动时候,该计数器会出现计数、归零循环的一个过程,直到 key 值一直 为 0,即按键持续被按下并且抖动过程结束,计数器才会持续计数到 5ms;

②第 26 行的 always 块产生一个标志,当检测到 cnt 第一次等于 5ms 的时候,该标志则被置为高电平,这样就可以将 cnt 第一次等于 5ms 和之后 的 cnt 等于 5ms 区分开,直到 key 松开(值为 1)时,该标志才被置为低电平;

③第 34 行的 always 块实现产生整个按键过程中的一个时钟周期高电平的标志,当 cnt 计数到 5ms 时,为了确保只有一次的 po_key_flag 有效, 因此此处条件中不仅需要 cnt==5ms,而且需要 cnt_flag==0。至此,实现了按键的消抖处理,在此基础上就可以很好地实现最初的要求了。

在第十二章中将对Verilog HDL 中数码管进行讲解。

往期回顾

FPGA入门系列1--模块书写&电路综合

FPGA入门系列2--仿真验证

FPGA入门系列3--wire与reg

FPGA入门系列4--赋值语句

FPGA入门系列5--运算符号

FPGA入门系列6--判断语句

FPGA入门系列7--时钟分频

FPGA入门系列8--Top_Down设计

FPGA入门系列9--状态机及do文件