以下是本人在自己在设计PCIe中常遇到的一些知识,对他们进行了简单整理一下,包括基本定义、传输速率、layout要求等。比如作为硬件工程师要了解芯片架构,哪些PCIe接口可以使用,使用这些PCIe要做什么,需要使用PCIe x1还是x2等。当硬件工程师设计完接口之后,layout工程师拿到原理图,开始进行PCB设计。那就涉及到PCIe的layout设计要求,包括阻抗、layout的长度、过孔的数量等。再layout设计完成之后,为了保证信号的质量,对于这种高速信号还要进行信号完整性仿真,查看layout是否满足要求。这时就需要搭建PCIe的仿真链路,这可能需要IBIS、PCB的S参数、SI的spec等。

1.PCIe基本定义:

PCI-Express(peripheral component interconnect express)是一种高速串行计算机扩展总线标准。PCIe属于高速串行点对点双通道高带宽传输,所连接的设备分配独享通道带宽。PCI Express也有多种规格,从PCI Express x1到PCI Express x32,能满足将来一定时间内出现的低速设备和高速设备的需求。PCI-Express的接口是PCIe 3.0接口,其比特率为8Gbps,约为上一代产品带宽的两倍,并且包含发射器和接收器均衡、PLL改善以及时钟数据恢复等一系列重要的新功能,用以改善数据传输和数据保护性能。PCI Express总线链路支持任何两个端点之间的全双工通信。

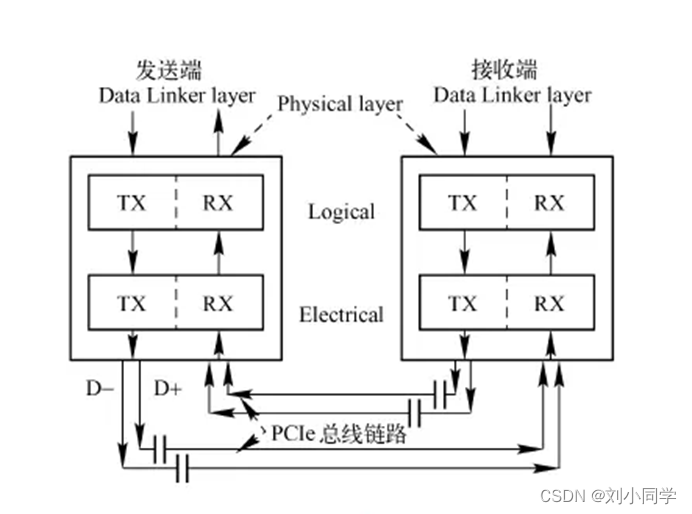

2. PCIe通道:

通道(lane)由两个差分信号对组成,一对用于接收数据(RX),另一对用于发送数据(TX),还有一对差分的参考时钟(CLK)。 因此,每个通道由四条线数据线组成。在概念上,每条通道用作全双工字节流,在链路端点之间的两个方向同时传输8位“字节”格式的数据包。物理PCI Express链路可能包含1个到32个通道,更精确地包括1,2,4,8,12,16或32个通道。通道计数用“×”前缀( 例如“×8”表示八通道卡或插槽),×16是常用的最大尺寸。

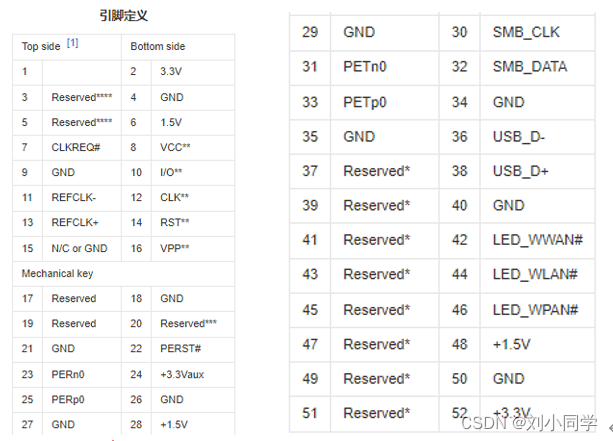

3.Mini PCIe:

基于PCI Express的PCI Express迷你卡(也称为Mini PCI Express,Mini PCIe,Mini PCI-E,mPCIe和PEM)是Mini PCI外形尺寸的替代品。Mini PCI-E连接器,该产品广泛用笔记本电脑主板,如E-PC、Netbook,及无线网卡,固态硬盘等设备。引脚定义:

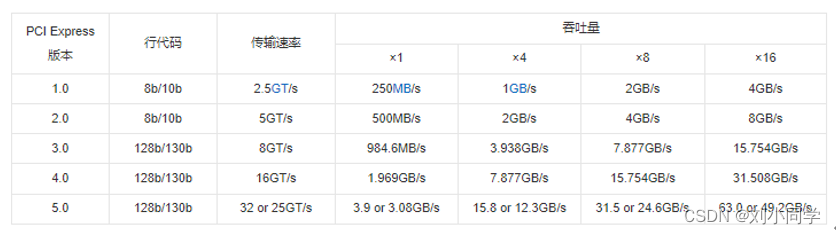

4. PCIe版本:

2022年1月12日,PCI-SIG 组织正式发布了 PCIe 6.0 标准,速度达到了 64 GT / s。2022年6月22日,发布和维护 PCIe 标准的联盟 PCI-SIG 宣布推出最新一代 PCIe 规范 PCIe 7.0 或 PCIe Gen 7 。最新一代 PCIe 带宽翻了一番,在一条通道 (x1) 上单向实现 128GT / s 或 128Gbps 总吞吐量。

5. PCIe编码方式:

6.单位:

GT/s:即Giga Transmission per second,千兆传输/秒,每一秒内传输的次数。

Gbps:即Giga Bits Per Second ,千兆位/秒。

GT/s 与Gbps 之间不存在成比例的换算关系。

1GB/s = 8Gbps = 8Gbit/s

bit 位:位是计算机中存储数据的最小单位,指二进制数中的一个位数,其值为“0”或“1”。

byte 字节:字节是计算机存储容量的基本单位,一个字节由8位二进制数组成。

7. PCIE带宽计算

吞吐量 = 传输速率 * 编码方案,现行的PCI-e2.0 协议支持 5.0 GT/s,即每一条Lane 上支持每秒钟内传输 5G个Bit;编码方式是 8b/10b 的编码方案,即每传输8个Bit,需要发送10个Bit。那么,PCIe 2.0协议的每一条Lane支持 5 * 8 / 10 = 4 Gbps = 500 MB/s 的速率。,一条PCIe 2.0 x16的通道,x16的可用带宽为 4*16 = 64 Gbps = 8 GB/s,双向带宽高达16GB/s。

8.PCIe信号定义:

PERST#信号:该信号为全局复位信号,由处理器系统提供,处理器系统需要为PCle插槽和PCle 设备提供该复位信号。PCle设备使用该信号复位内部逻辑。当该信号有效时,PCle设备将进行复位操作。PCle总线定义了多种复位方式,其中Cold Reset和Warm Reset 这两种复位方式的实现与该信号有关。

WAKE#信号:当PCIe 设备进入休眠状态,主电源已经停止供电时,PCle 设备使用该信号向处理器系统提交唤醒请求,使处理器系统重新为该PCIe 设备提供主电源Vcc。

CLKREQ#信号:插件卡驱动的低电平有效开漏信号,请求PCI Express参考时钟可用(有效时钟状态)以允许 PCI Express接口发送/接收数据。

CLK_P/ CLK_N#信号:低电压差分信号。系统板需要提供一个符合PCIe基本规范的通用架构的参考时钟

TX/ RX#信号:信号双向传输信号;

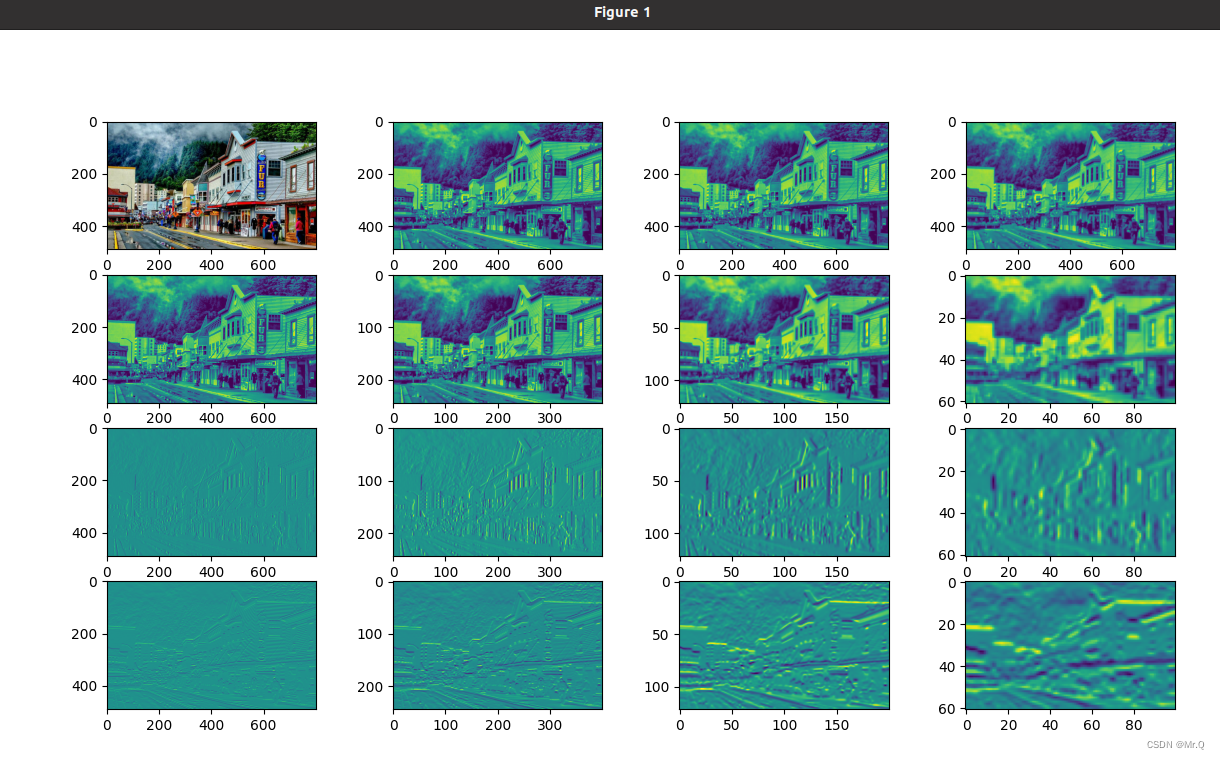

9.PCIe Simulation:

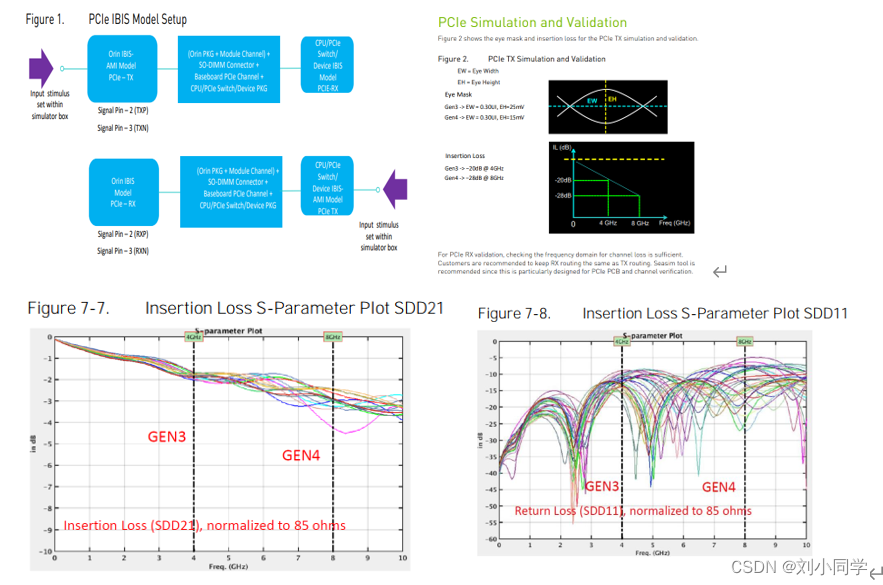

PCIe的信号完整性仿真需要前期准备的工作:芯片的IBIS模型(IBIS-AMI)、芯片的PKG、提取PCB走线的S参数、连接器的S参数、SI的Spec等。以下是参考Orin_NX_Orin_Nano_Signal_Integrity_Simulation:

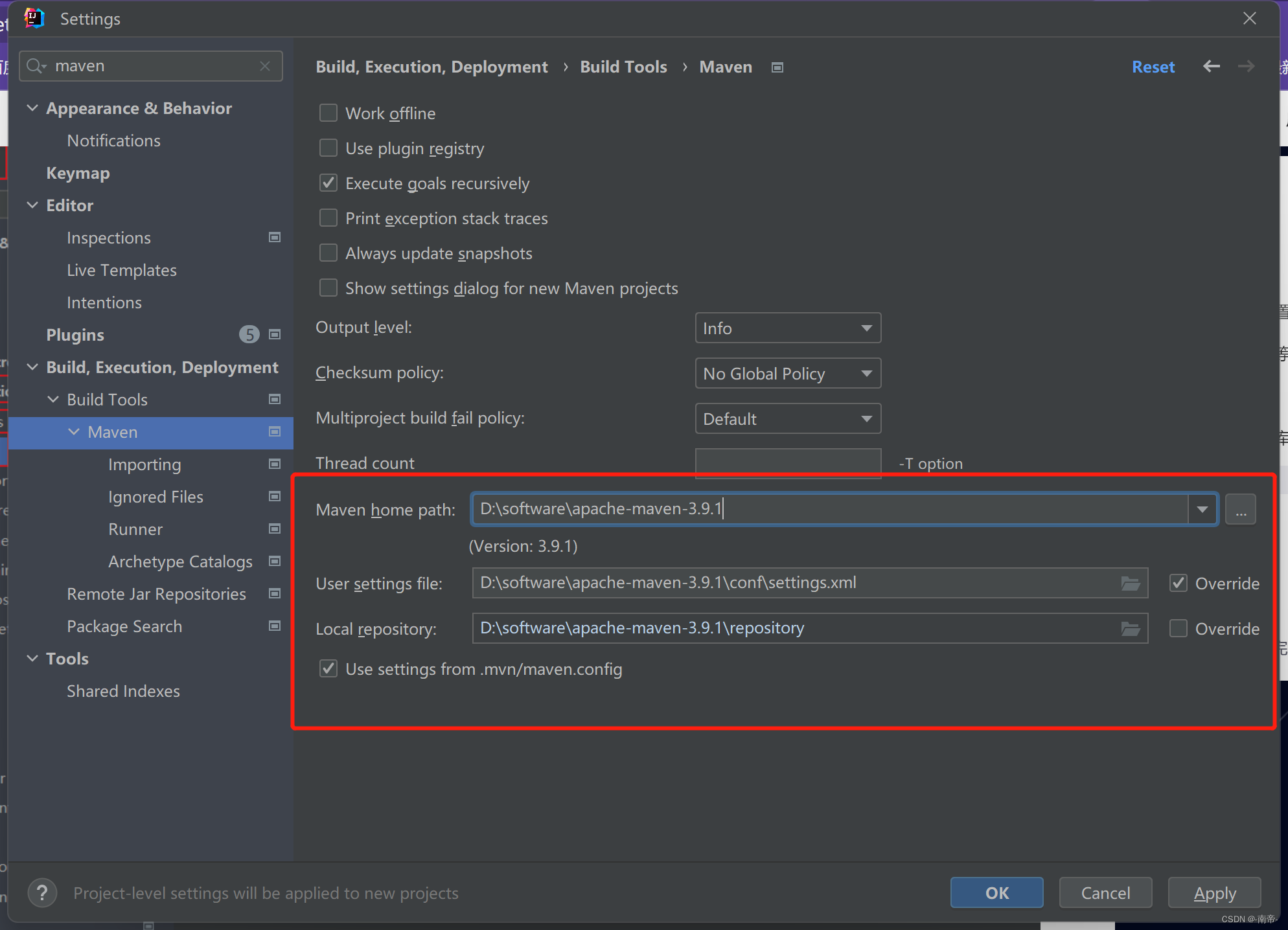

10. PCIe layout要求:

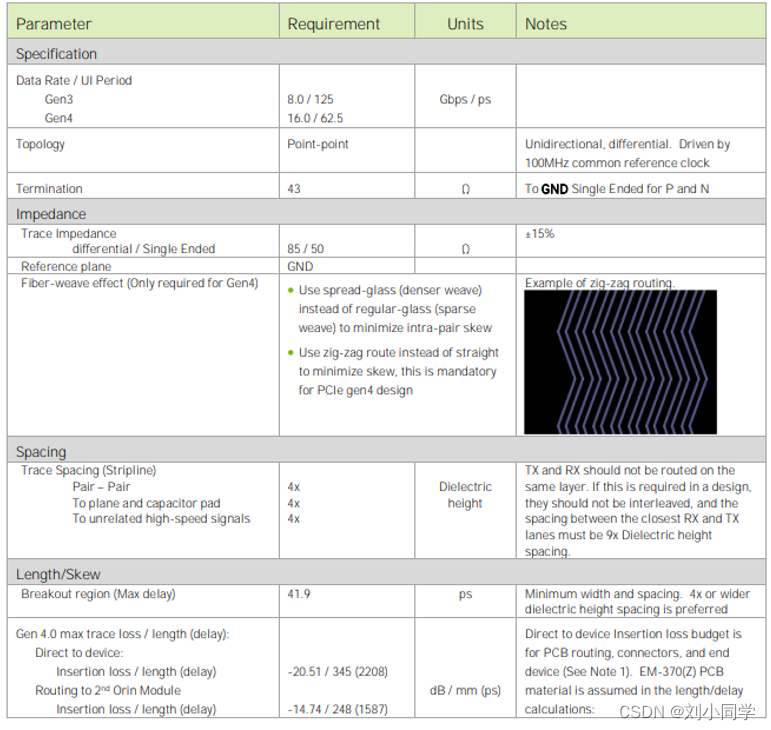

PCIe对于PCB设计方面,要求还是比较严格。首先是差分阻抗的要求:85 / 50欧姆,±15%。还有就是走线的最大打孔数量:4(Use micro via or back drilled via - no via stub allowed.)等等。以下是Jetson_Orin_NX_Series_and_Orin_Nano_Series_Design_Guide:

11.参考网址:

https://pcisig.com/

https://baike.baidu.com/item/pcie/2167538?fr=aladdin

https://blog.csdn.net/weixin_41808082/article/details/124377320?spm=1001.2014.3001.5501

https://developer.nvidia.com/embedded/downloads#?tx=$product,jetson_orin_nx

以上资料主要是本人在PCB设计中和网络搜索整理而成

如有雷同或错误,希望各位大神留言指正,感谢!!!

![[MySQL / Mariadb] 数据库学习-Linux中二进制方式安装MySQL5.7](https://img-blog.csdnimg.cn/c0223722813d4283a2ec85cc7a54b9e1.png)