最近要用APT32F110x做一些开发,顺便学习一下。

APT32F110x 是由爱普特推出的基于平头哥(T-Head Microsystems)CPU 内核开发的 32 位高性能低成本单片机。

APT32F1104x基于嵌入式 Flash 工艺制造,内部丰富的模拟资源,包括模拟比较器、LCD 控制器,面向的应用为工业控制,小家电,消费电子设备,可穿戴设备等应用。

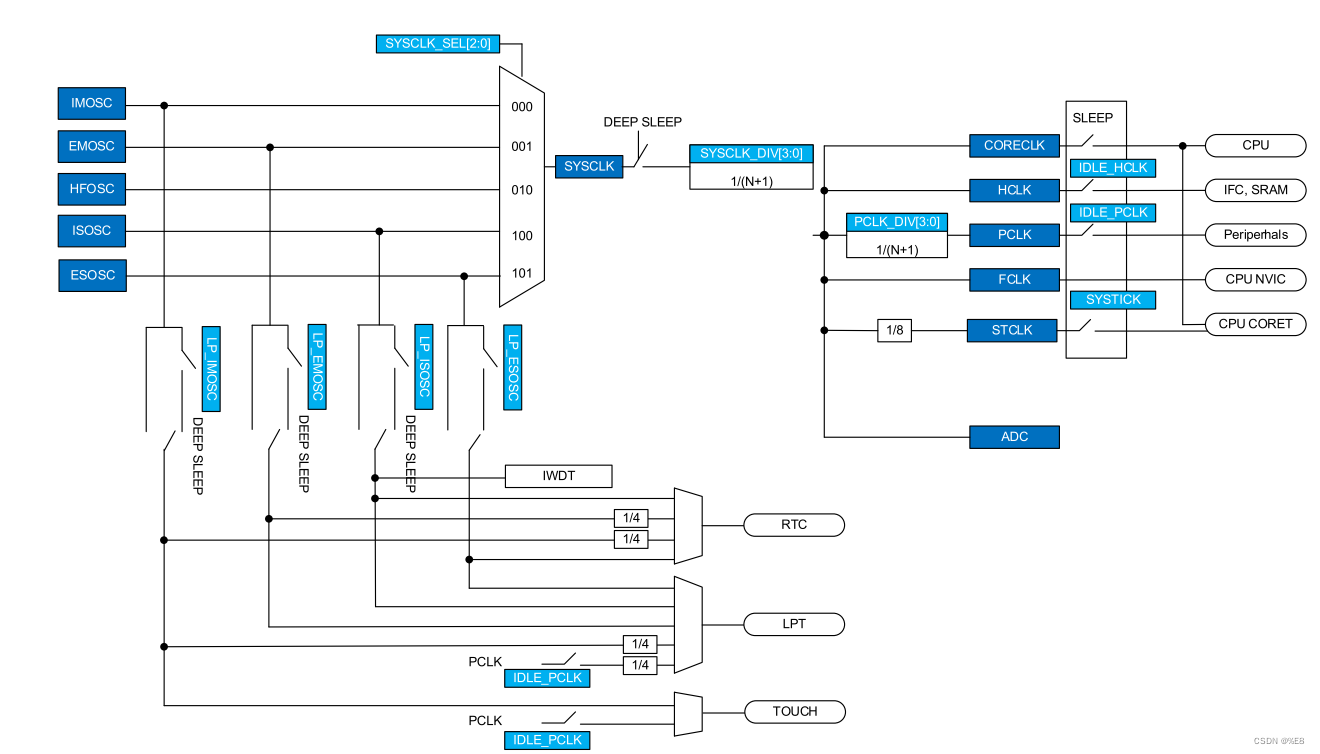

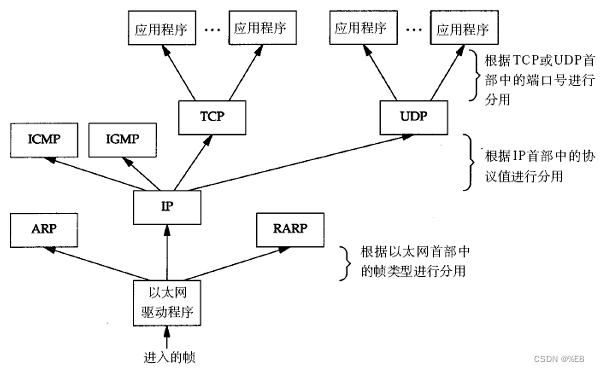

APT32F1104x的系统时钟源选择和 HCLK/PCLK 频率管理

支持多种时钟源作为系统时钟运行:

- 内部低速振荡器(IMOSC)为缺省时钟源:5.556MHz/4.194MHz/2.097MHz/131.072KHz

- 内部高速振荡器(HFOSC):48MHz

- 外部主晶振(EMOSC):0.4MHz ~ 24MHz/32.738KHz

- 外部 RTC 晶振(ESOSC):32.768KHz

- 内部超低功耗振荡器(ISOSC):27KHz

可编程 CPU 时钟(HCLK)和外设时钟(PCLK)

外部时钟失效监测(Clock Fail Monitor),支持时钟去抖选项

可选择的系统内部时钟源输出(CLO)

时钟结构如下图:

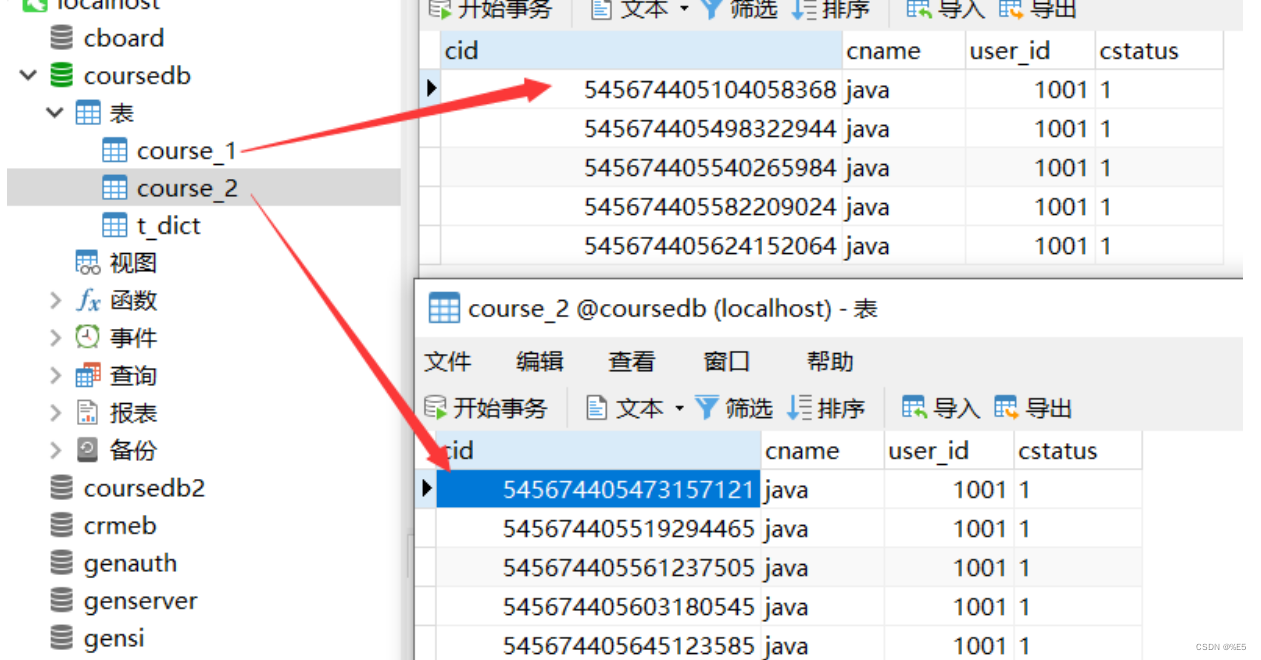

爱普特提供了demo,其时钟设置在board_config.c中的:

csi_clk_config_t tClkConfig =

{SRC_HFOSC, HFOSC_48M_VALUE, SCLK_DIV1, PCLK_DIV1, 5556000, 5556000};

//{SRC_EMOSC, 20000000, SCLK_DIV1, PCLK_DIV2, 5556000, 5556000};

//{SRC_IMOSC, IMOSC_5M_VALUE, SCLK_DIV1, PCLK_DIV2,5556000, 5556000};

//{SRC_HFOSC, HFOSC_48M_VALUE, SCLK_DIV1, PCLK_DIV1,5556000, 5556000};

//{SRC_IMOSC, IMOSC_4M_VALUE, SCLK_DIV1, PCLK_DIV1,5556000, 5556000};

//{SRC_IMOSC, IMOSC_2M_VALUE, SCLK_DIV1, PCLK_DIV1,5556000, 5556000};

//{SRC_IMOSC, IMOSC_131K_VALUE, SCLK_DIV1, PCLK_DIV1,5556000, 5556000};

//{SRC_ESOSC, ESOSC_VALUE, SCLK_DIV1, PCLK_DIV1,5556000, 5556000};

csi_clk_config_t的结构则定义在sys_clk.h:

typedef struct {

cclk_src_e eClkSrc; //clock source

uint32_t wFreq; //clock frequency

hclk_div_e eSdiv; //SDIV

pclk_div_e ePdiv; //PDIV

uint32_t wSclk; //SCLK

uint32_t wPclk;

}csi_clk_config_t;结构字段的具体解释:

cclk_src_e eClkSrc; //对应的是SYSCLK_SEL[2:0]

uint32_t wFreq; //clock frequency, 输入时钟的频率,比如内部低速振荡器(IMOSC)的:5.556MHz/4.194MHz/2.097MHz/131.072KHz

hclk_div_e eSdiv; //SCLK的分频,即SYSCLK_DIV的值, 由“wTargetSclk = wFreq/g_wHclkDiv[tClkConfig.eSdiv];”中的“g_wHclkDiv”决定,取决于g_wHclkDiv的索引值是多少

pclk_div_e ePdiv; //PCLK分频,即PCLK_DIV, 实际值是“tClkConfig.wPclk = tClkConfig.wSclk/(0x1<<tClkConfig.ePdiv);”

uint32_t wSclk; //SYSCLK,设置无意义,实际由“tClkConfig.wSclk = wTargetSclk;”决定,csi_sysclk_config中会重新赋值

uint32_t wPclk; //PCLK,设置无意义,实际由”tClkConfig.wPclk = tClkConfig.wSclk/(0x1<<tClkConfig.ePdiv);“决定,csi_sysclk_config中会重新赋值

![阶段二38_面向对象高级_网络编程[UDP单播组播广播代码实现]](https://img-blog.csdnimg.cn/3ad5a6179b9a40fca28227ddb8eb5362.png#pic_center)