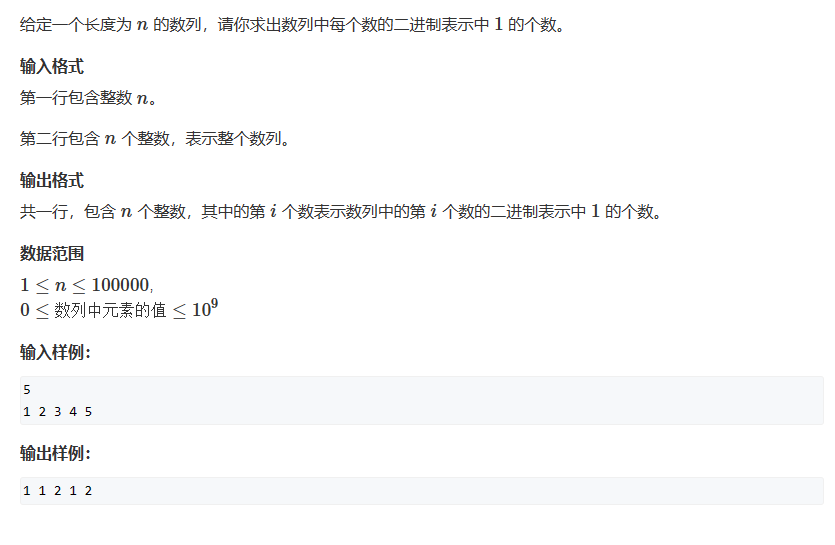

以下说明来自ug900:在 Vivado 仿真器中以批处理或脚本模式进行仿真 具体可以内容可自行查找

其中代码运行截图为自己实践的实例·

Note: xelab, xvlog and xvhdl are not Tcl commands. The xvlog, xvhdl, xelab are Vivado-independent compiler executables. Hence, there is no Tcl command for them.

注意,xelab, xvlog and xvhdl不是 Tcl 命令。xvlog, xvhdl, xelab 是独立于 Vivado 的编译器可执行文件。 因此,它们没有 Tcl 命令。

若对应命令需要帮助,可以用xxx -help

解析设计文件,xvhdl 和 xvlog

xvhdl:

此命令分析 VHDL 源文件并将分析的转储存储到 HDL 中 磁盘上的库。

xvlog:

The xvlog command is the Verilog parser. The xvlog command parses the Verilog source file(s) and stores the parsed dump into a HDL library on disk.

该命令是Verilog解析器。该 xvlog 命令解析 Verilog 源文件,并将解析的转储存储到 HDL 磁盘上的库。

使用方式

Usage: xvlog [options] file

后面给出的是需要解析的HDL文件

示例:

–sv指定输入的文件用sv模式编译,–work给定了对应存储库的名字为mylib,最后给出需要解析的HDL文件为src文件夹中所有的.v .sv文件。

可选项-和–

通常而言,-说明参数是字符形式,后面接的是单字母命令。- -说明参数是字符串形式,对应相应单-命令的全称两者是等价的,如 xx -h 和 xx --help。

此命令中间有很多的可选项,不清楚的话可以去ug900中查,也可以直接命令行里输入xvlog -h或–help。

ug900的指令可选项列表

xelab 详细阐述和生成设计快照

使用 Vivado 仿真器进行仿真分两个阶段进行:

在第一阶段,模拟器编译器 xelab 将 HDL 模型编译为快照,快照以模拟器可以执行的形式表示模型。

在第二阶段,模拟器加载并执行(使用命令)快照以模拟模型。在非项目模式下,您可以通过跳过第一阶段并重复第二阶段来重复使用快照。xsim

当模拟器创建快照时,它会根据模型中排名靠前的模块的名称为快照分配一个名称。但是,您可以通过将快照名称指定为编译器的选项来覆盖默认值。快照名称在目录或 SIMSET 中必须是唯一的;重复使用快照名称(无论是默认名称还是自定义名称)都会导致使用该名称覆盖以前构建的快照。

重要:在同一目录或 SIMSET 中,不能用相同的快照名运行两个模拟

使用方式

Usage: xelab [options] [libname.]unitname

其中必须xelab命令后面跟的就是[libname.]unitname(设计的顶层),中间有很多的可选项,不清楚的话可以去ug900中查,也可以直接命令行里输入xelab -h,他会给出所有可选项和示例等。

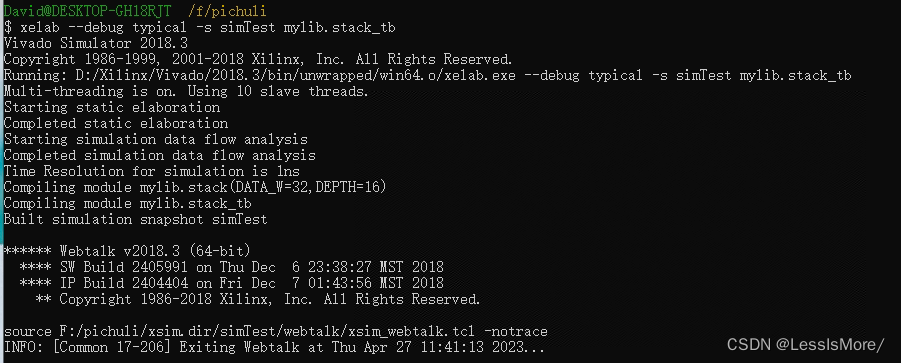

示例:

以下指令编译了模块(编译为快照?),创建了快照mylib.stack_tb

以下是多了两个参数

-s [ --snapshot ] arg:Specify the name of design snapshot

指定了快照名simTest,所以后面指令显示的快照名就是simTest,没有指定就是默认的顶层mylib.stack_tb

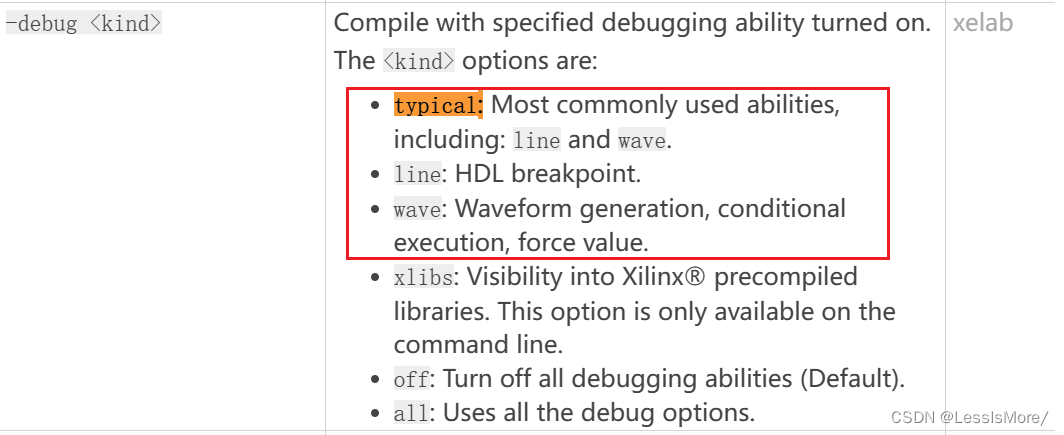

–debug参数如下:

static elaboration

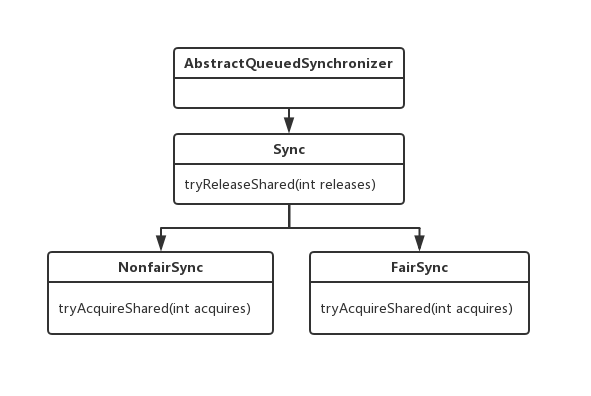

指令执行中涉及了static elaboration,可以参考文章:elaborate

analyze: (xvlog做的)读入RTL代码,分析每个文件的语法是否正确。(这个时候每个module还是独立的,没有instance的关系)

elaborate: 用analyze已经读入的RTL代码来构建hierarchy。顶层是可以设置的。这个时候整个design的层次就有了,instance的关系也明确了。

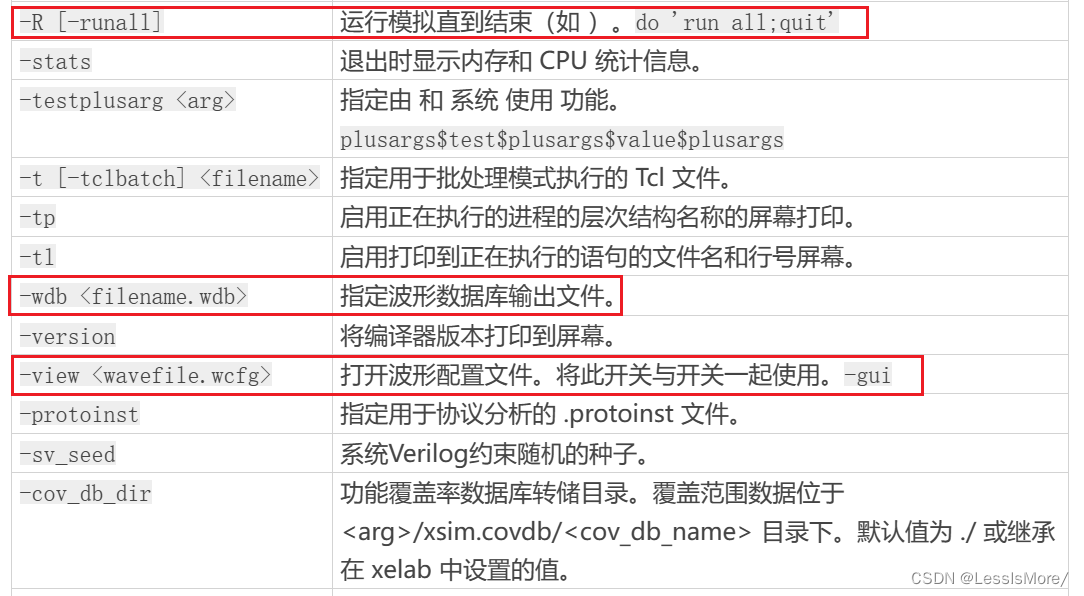

xsim模拟设计快照

该命令加载模拟快照以执行批处理模式模拟,或提供工作区 (GUI)或基于 Tcl 的交互式模拟环境。

语法:xsim

示例:

该指令会打开vivado的仿真波形界面,将波形添加后可以运行查看结果。

总结※

总之我理解的这三个指令就是:

1、xvlog会analyze解析HDL文件;

analyze: 读入RTL代码,分析每个文件的语法是否正确。(这个时候每个module还是独立的,没有instance的关系)

2、xelab会将 HDL 模型编译为快照,快照以模拟器可以执行的形式表示模型(就是之前提到的第一阶段),其中有elaborate (用analyze已经读入的RTL代码来构建hierarchy。顶层是可以设置的。这个时候整个design的层次就有了,instance的关系也明确了)来构建模块间的层次结构,并且会分析各模块数据流;

3、xsim模拟器加载并执行(使用命令)快照以模拟模型(第二阶段),就是进行仿真,这个仿真可以存波形文件多次调用。

![[论文分享] VOS: Learning What You Don‘t Know by Virtual Outlier Synthesis](https://img-blog.csdnimg.cn/916709f806c447a0b037abc0063a654e.png)