学习步骤:

如果我要学习并行存储器,我会采取以下几个步骤:

-

了解并行存储器的基本概念和原理。学习并行存储器的前提是要对存储器的基本原理有所了解,包括存储器的分类、工作原理、读写时序等。

-

学习并行存储器的特点和应用。并行存储器在高性能计算、图形图像处理等领域具有广泛的应用,学习并行存储器的特点和应用可以帮助我们更好地理解其在实际应用中的作用和优势。

-

学习并行存储器的组成和结构。了解并行存储器的组成和结构可以帮助我们更深入地理解其工作原理和性能表现。

-

掌握并行存储器的读写时序和操作流程。并行存储器的读写时序和操作流程比较复杂,需要耐心地进行学习和实践,熟悉这些内容对于理解并行存储器的工作原理和性能表现至关重要。

-

学习并行存储器的性能评估和优化方法。对于高性能计算和图形图像处理等领域的应用,性能是非常关键的因素。学习并行存储器的性能评估和优化方法可以帮助我们更好地发挥并行存储器的性能优势。

-

实践并行存储器的应用。最后,通过实践并行存储器的应用,例如开发并行存储器相关的软件或应用程序,可以巩固自己的学习成果,并更好地理解并行存储器的实际应用和性能表现。

学习目标:

我的学习目标如下:

-

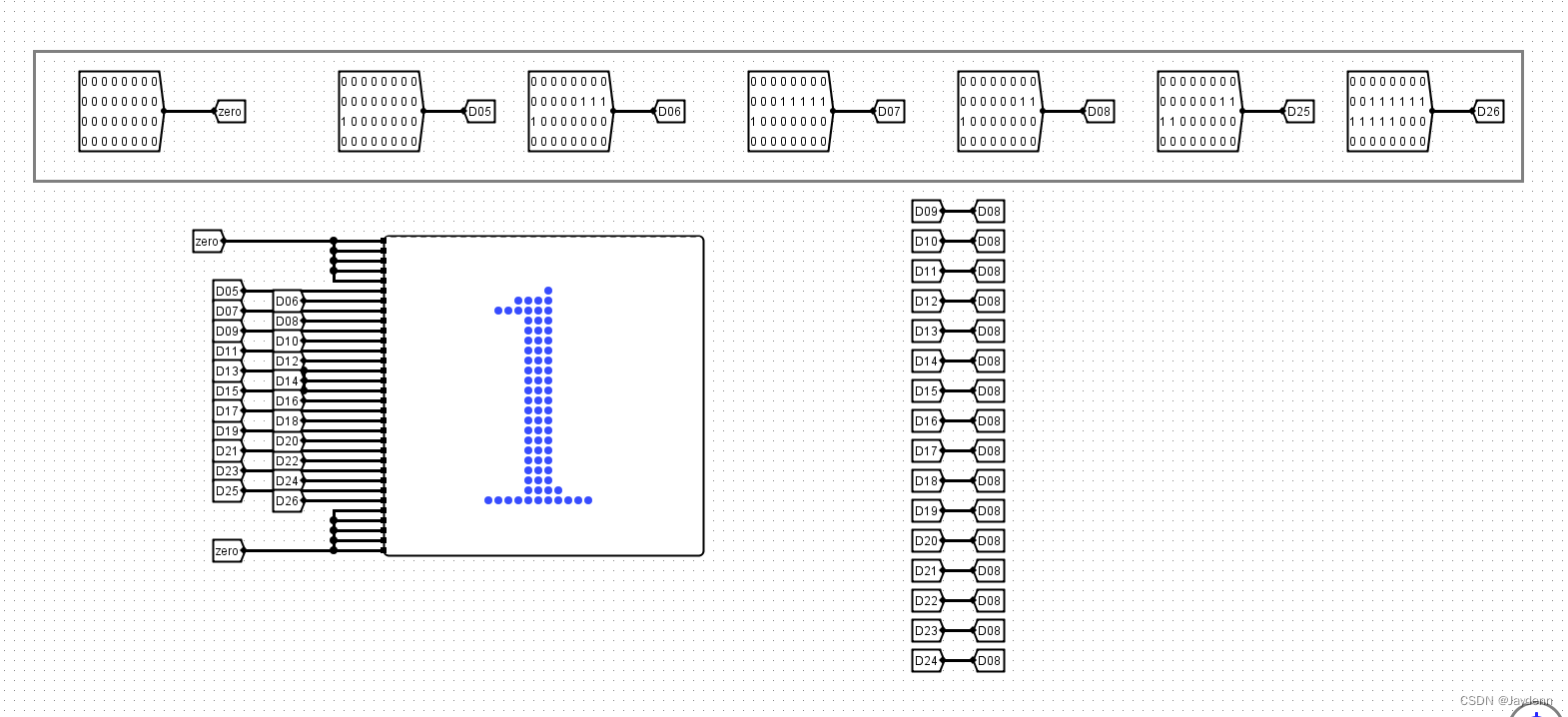

理解并行存储器的基本原理和结构,包括并行存储器的并行性、存储单元的排列方式以及数据的存储和访问方式等。

-

了解并行存储器的主要类型,包括静态并行存储器(SPM)、动态并行存储器(DPM)以及快速存储器(SSM)等,分析各种存储器的特点和适用场景。

-

掌握并行存储器的读写时序和接口,包括并行存储器的数据输入输出、地址输入、使能信号和时钟信号等,并了解其电气特性和性能参数。

-

学习并行存储器的设计和优化方法,包括存储器的布局、存储单元的编址方式、并行存储器的并行度和并行度优化等。

-

理解并行存储器在现代计算机系统中的应用,包括并行处理器、图形处理器和大规模集成电路等领域的应用。

-

进行实践操作,编写测试程序,测试并行存储器的读写性能,加深对并行存储器的理解。

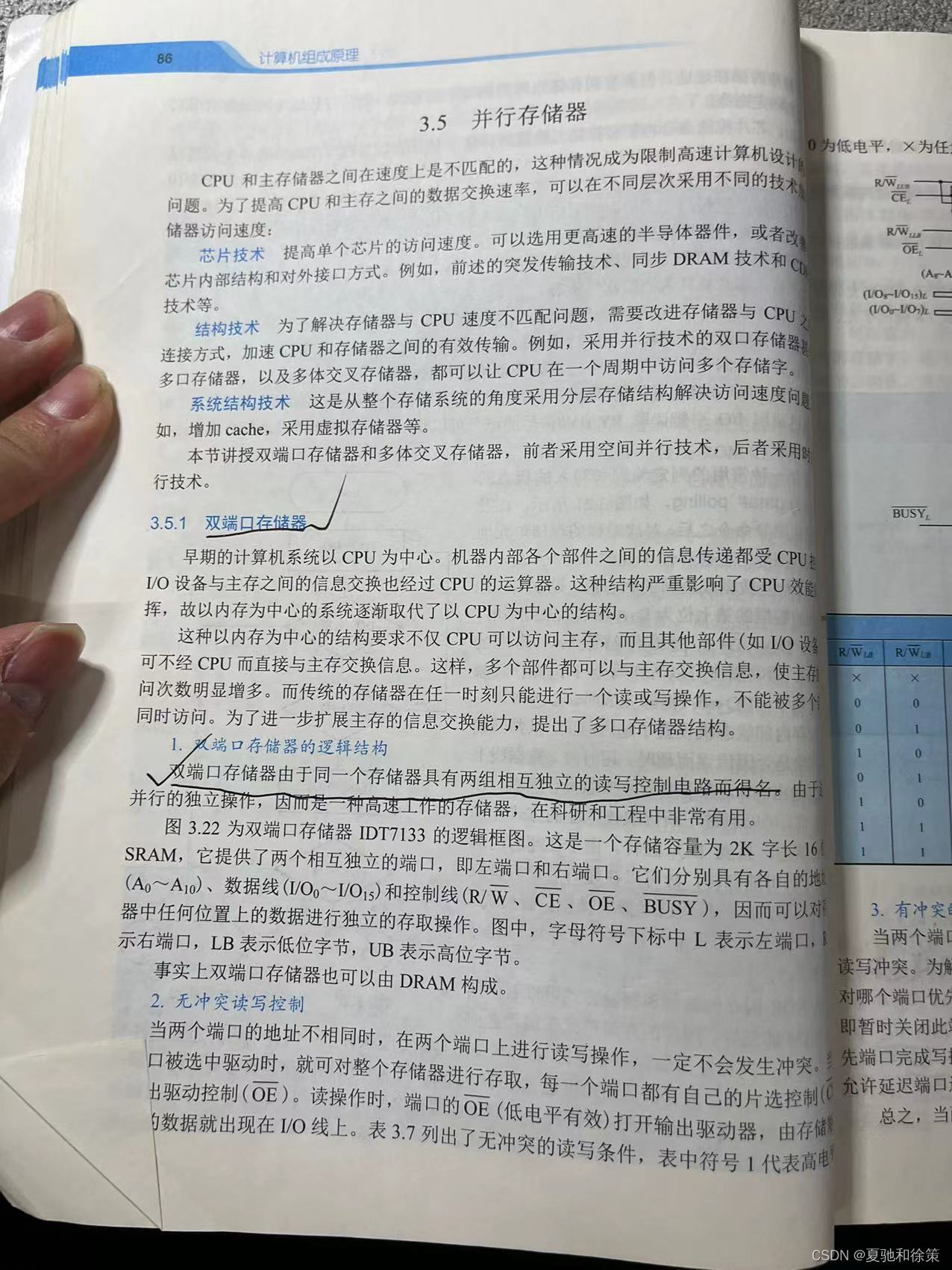

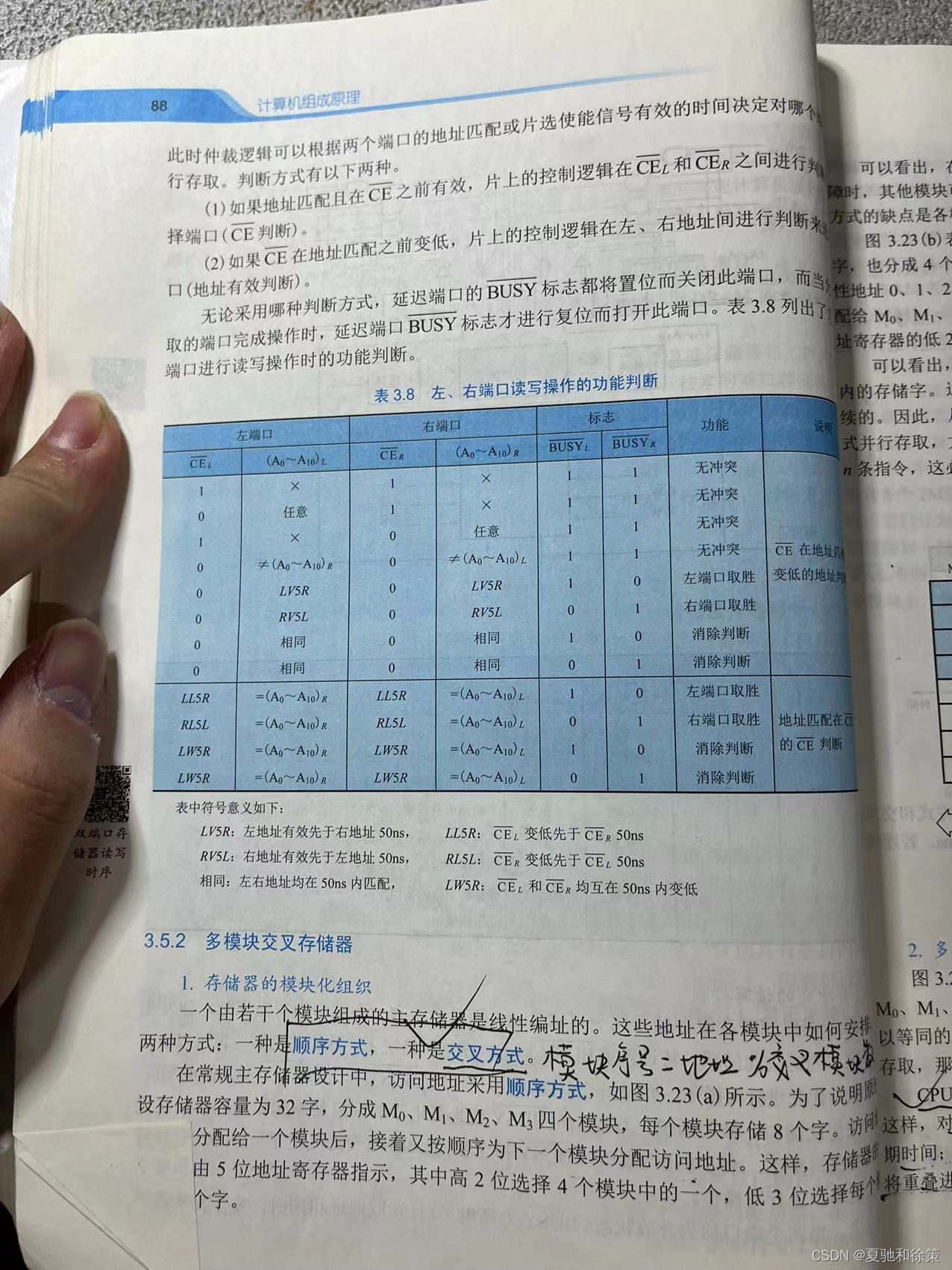

3.5.1 双端口存储器

双端口存储器是一种具有两个数据输入/输出端口的存储器,可以在同时进行读写操作。它通常用于多处理器系统中,其中多个处理器需要同时访问同一块存储器,或者需要同时读取和写入不同的存储位置。

双端口存储器可以分为同步和异步两种类型。

同步双端口存储器是在时钟的同步下进行读写操作的,每个端口都有一个时钟输入,数据输入和输出都与时钟同步。同步双端口存储器的操作可以保证在时序上的一致性。

异步双端口存储器没有时钟输入,每个端口的读写操作是异步的。异步双端口存储器通常需要使用一些特殊的控制信号来实现同步操作,如读写锁定信号、地址锁定信号等。

双端口存储器可以通过硬件或软件方式实现。硬件实现通常使用两个单端口存储器,每个存储器被连接到不同的数据线和地址线上,以实现双端口存储器的功能。软件实现则使用逻辑电路来模拟双端口存储器的功能。

双端口存储器在多处理器系统中具有重要的应用,可以实现数据共享和数据传输等功能。它还可以用于视频处理和图像处理等需要同时读写多个数据的应用中。

3.5.2 多模块交叉存储器

双端口存储器是一种具有两个数据输入/输出端口的存储器,可以在同时进行读写操作。它通常用于多处理器系统中,其中多个处理器需要同时访问同一块存储器,或者需要同时读取和写入不同的存储位置。

双端口存储器可以分为同步和异步两种类型。

同步双端口存储器是在时钟的同步下进行读写操作的,每个端口都有一个时钟输入,数据输入和输出都与时钟同步。同步双端口存储器的操作可以保证在时序上的一致性。

异步双端口存储器没有时钟输入,每个端口的读写操作是异步的。异步双端口存储器通常需要使用一些特殊的控制信号来实现同步操作,如读写锁定信号、地址锁定信号等。

双端口存储器可以通过硬件或软件方式实现。硬件实现通常使用两个单端口存储器,每个存储器被连接到不同的数据线和地址线上,以实现双端口存储器的功能。软件实现则使用逻辑电路来模拟双端口存储器的功能。

双端口存储器在多处理器系统中具有重要的应用,可以实现数据共享和数据传输等功能。它还可以用于视频处理和图像处理等需要同时读写多个数据的应用中。

重点:

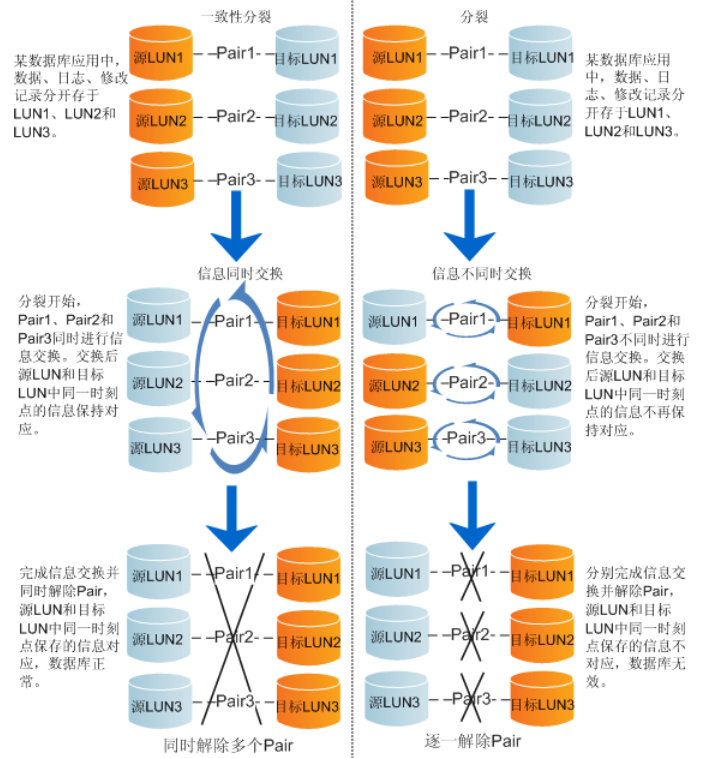

并行存储器是计算机中常用的一种高速存储器,主要包括双端口存储器和多模块交叉存储器两种类型。总结其重点、难点和易错点如下:

重点:

- 双端口存储器的原理、读写时序和应用场景;

- 多模块交叉存储器的原理、读写时序和容错设计;

- 存储器的并行性和并行操作的优化。

难点:

- 并行存储器的逻辑结构和控制信号的设计,需要对存储器硬件实现有深入的了解;

- 多模块交叉存储器的容错设计较为复杂,需要考虑模块间通信、错误检测和纠正等问题;

- 并行操作的优化需要考虑多种因素,如访存顺序、并行度、数据依赖等。

易错点:

- 对存储器读写时序的理解不清,容易导致数据错误;

- 对存储器逻辑结构的理解不深入,容易导致设计缺陷;

- 对存储器并行操作的优化不当,容易导致性能瓶颈或数据错误。