一、实验目的:

1.熟悉可编程逻辑器件的设计工具Quartus II 软件的使用。

2.熟悉FPGA开发实验系统的软件环境,掌握各个菜单和图标的作用和功能。

二、实验内容

(1)以74160实现八进制计数器为例,学Quartus II 软件的使用。熟悉输入、编译、仿真等过程。

(2)练习Quartus II 软件的使用,熟悉输入、编译、仿真等过程。

1)用74160实现同步八进制计数器

2)试用74138附加必要的门电路实现1位全加器

三、实验测试参数表格及步骤

1)用CT74160实现同步八进制计数器

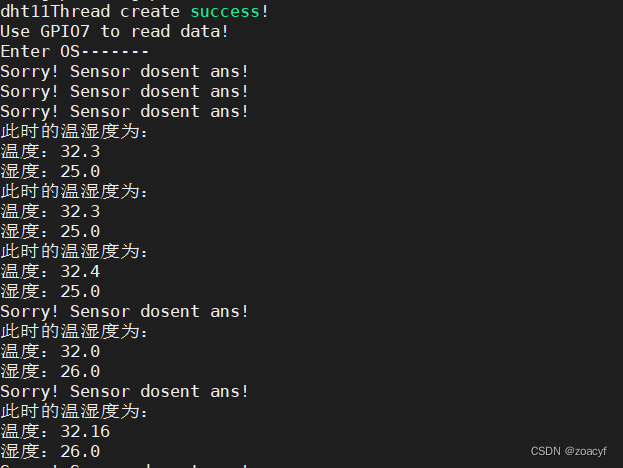

图一 74160仿真功能原理图

图二 74160功能波形图

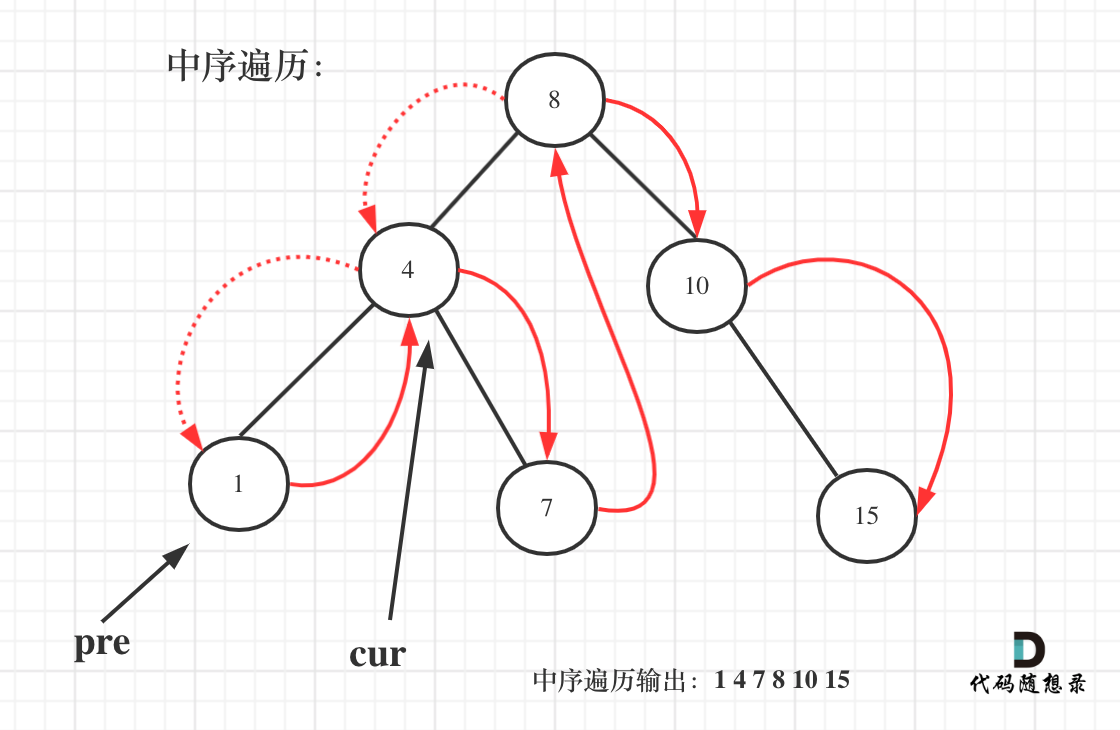

逻辑功能分析:当ENP和ENT接高电平,LDN和CLRN也接高电平时,根据时钟CP的波形,CT74160开始从000计数,当计数到111时,输出的值进行与非后,传给异步清零端LDN的值为0,LDN执行清零操作,最后CT74160从000开始计数,实现8进制计数器的功能。

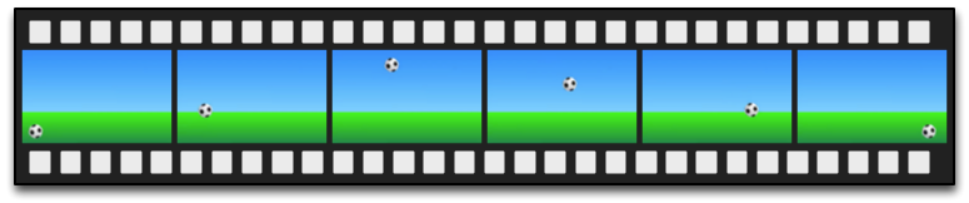

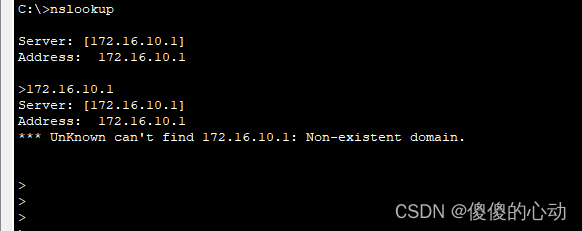

2)用CT74LS138译码器附加必要的门电路实现1位全加器

图三 CT74LS138译码器改编的全加器

图四 改编的全加器功能波形图

逻辑功能分析:

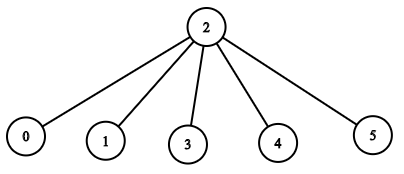

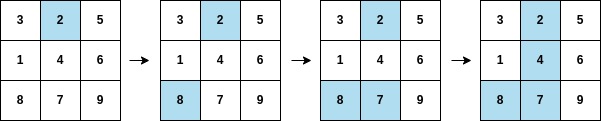

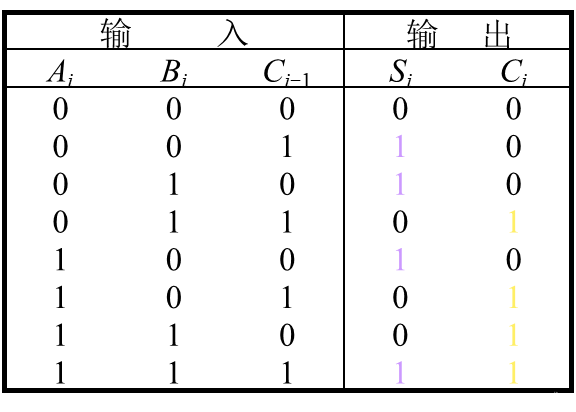

图五 全加器真值表

CT74LS138译码器在G2AN和G2BN低电平有效,G1高电平有效,这样配置该译码器才能正常工作。

根据全加器和译码器(输出低电平有效)的真值表,写出对应的函数式。根据分析,选出所需要的门电路,最后画出电路图。

如图三,图四,图五所示,被加数为Ai ,加数为Bi ,低位进位数为Ci-1 (仿真时Ci-1不通过,用Ci1代替)。输出本位和为 Si ,向高位的进位数为Ci。通过真值表,先画出其组合逻辑电路的电路图,后再在Quartus II上画出原理图。

由图五的波形图所知,上图所画原理图正确,且符合全加器的真值表。

![[架构之路-158]-《软考-系统分析师》-13-系统设计 - 高内聚低耦合详解、图解以及技术手段](https://img-blog.csdnimg.cn/img_convert/1b5eb161416b6c7a9e0917256b5f6f17.png)