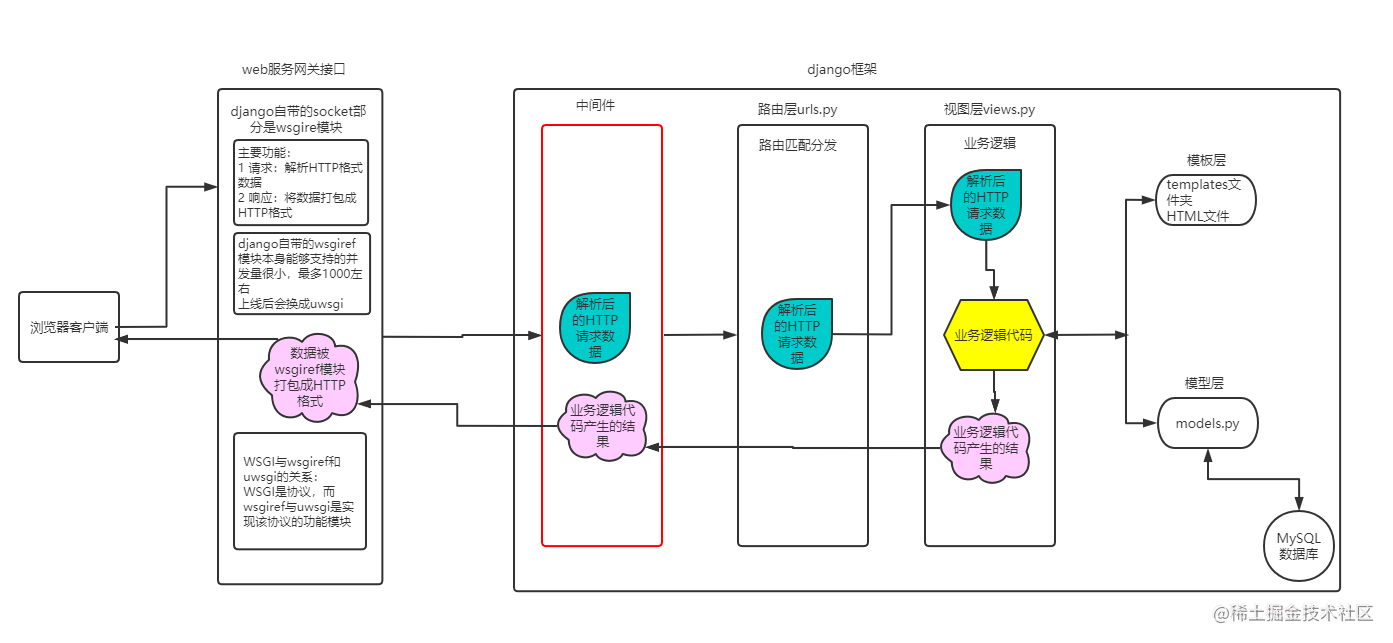

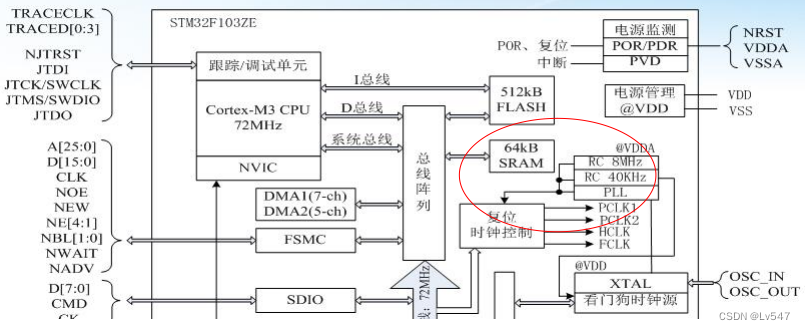

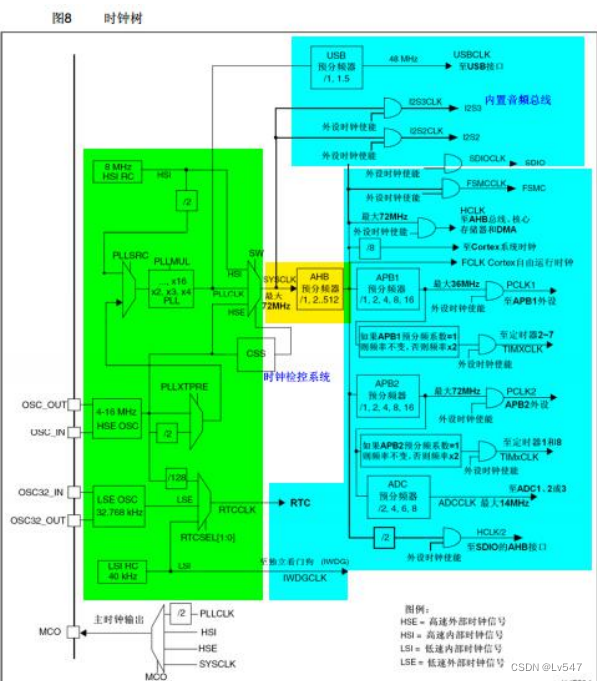

此图说明了STM32的时钟走向,从图的左边开始,从时钟源一步步分配到外设时钟。

时钟源分类

从时钟频率来说,分为高速时钟和低速时钟,高速时钟是供给芯片主体的主时钟,而低速时钟只是供 给芯片中的RTC(实时时钟)及独立看门狗使用。

从芯片角度来说,时钟源分为内部时钟与外部时钟 ,内部时钟是由芯片内部RC振荡器产生的,起振较快,所以时钟在芯片刚上电的时候,默认使用内部高速时钟。而外部时钟信号是由外部的晶振输入的 ,在精度和稳定性上都有很大优势,所以上电之后再通过软件配置,转而采用外部时钟信号。

STM32有以下个时钟源

高速外部时钟(HSE):以外部晶振作为时钟源,晶振频率 可取范围4—16Mhz,一般采用8Mhz。

高速内部时钟源(HSI):由内部RC振荡器产生,频率为 8Mhz,但不稳定。

低速外部时钟源(LSE):以外部晶振为时钟源,主要供给 RTC模块,一般采用32.768khz

低速内部时钟源(LSI):由内部RC振荡器产生,也主要供 给RTC模块,频率大约为40Khz

PLL为锁相环倍频输出,其时钟输入源可选择为HSI/2、HSE 或者HSE/2。倍频可选择为2~16倍,但是其输出频率最大不 得超过72MHz

SysCLK、HCLK、FCLK、PCLK1、PCLK2:

从时钟树的分析,看到经过一系列的倍频、分频后得到几个与开发密切相 关的时钟:

1)SYSCLK:系统时钟,是STM32大部分器件的时钟来源,可来源于三个时钟 源(HIS/HSE/PLL),由AHB预分频器分频分配到各个部件。

2)HCLK:由AHB预分频器直接输出得到,它是高速总线AHB的时钟信号,提 供给存储器、DMA及Cortex内核,是内核运行的时钟(cpu主频)。

3)FCLK:同样由AHB预分频器输出得到,是内核的“自由运行时钟” , “ 自由”表现在它不依赖HCLK,即使HCLK停止,FCLK也继续运行,它的存在 可以保证,在处理器休眠时也能采样到中断和跟踪休眠事件

4)PCLK1:外设时钟,由APB1预分频器输出得到,最大频率为36Mhz,提供 给低速外设

5)PCLK2:外设时钟,由APB2预分频器输出得到,最大频率72Mhz,提供给 高速外设

时钟管理寄存器

时钟控制寄存器(RCC_CR)

时钟配置寄存器(RCC_CFGR)

时钟中断寄存器(RCC_CIR)

(详细说明参加STM32参考手册)