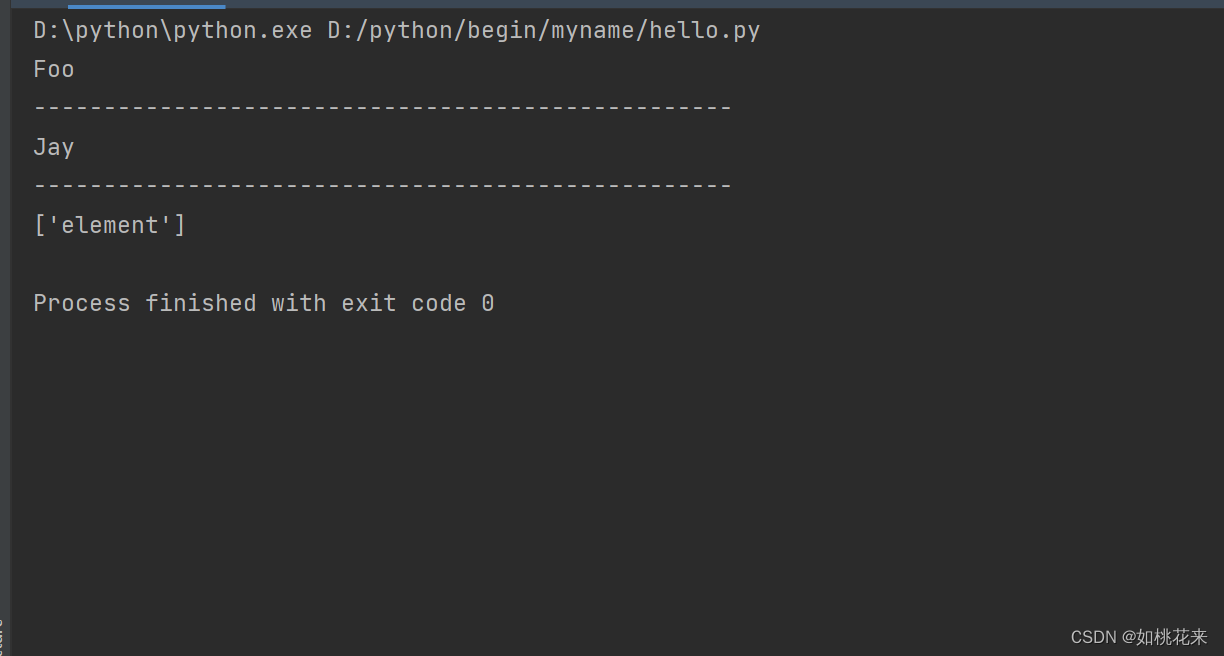

STM32系列产品命名规则

以stm32f103zet6为例

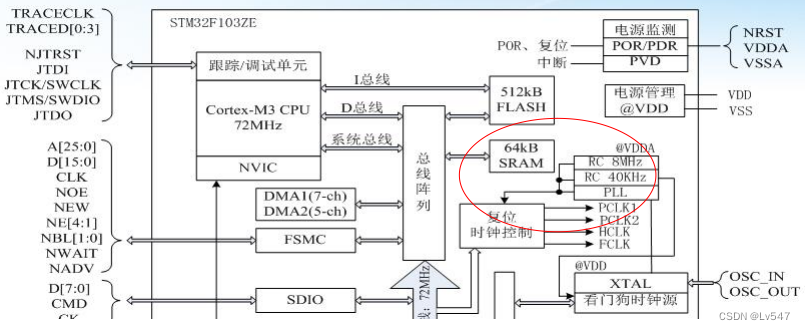

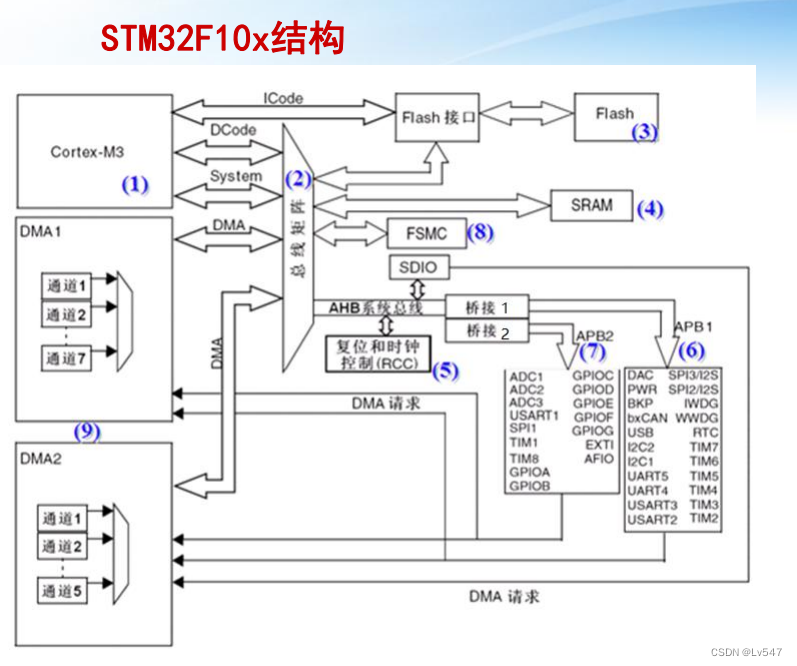

Stm32微控制器架构

模块

• 处理器核心

• 存储器

• 时钟电路、系统总线

• 外设(硬件单元):I/O接口、通信接口、定时器 、ADC和DAC, ……

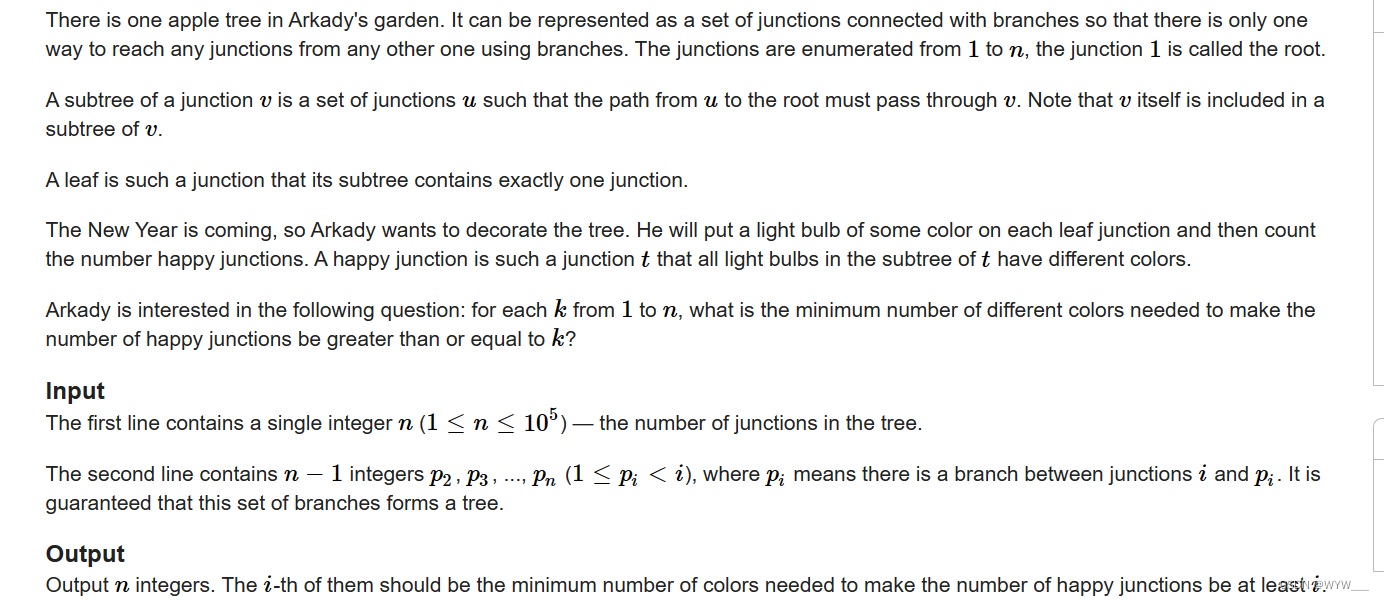

系统结构

哈佛存储结构

• 独立的指令总线(I-bus),将CM3内核的指令总 线与FLASH指令接口相连,用于指令预取

总线矩阵(Bus Matrix)

提供多种数据通道

• 数据总线(D-bus):将CM3内核的数据总线与 FLASH数据接口相连,用于常量加载和调试

• 系统总线(System):将CM3内核的系统总线与总 线矩阵相连,协调内核与DMA访问

• DMA和SRAM

通过AHB-APB桥连接2个先进外设总线APB

• APB2可全速工作于72MHz,但APB1限制在36MHz

• 外设连接在APB上

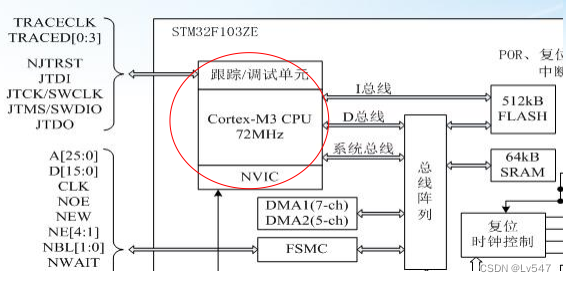

STM32F系列具体结构

1.Cortex-M3 CPU内核

STM32F103ZET6集成了Cortex-M3内核CPU,工作频率为72MHz ,与CPU紧耦合的为嵌套向量中断控制器NVIC和跟踪调试单 元,其中,调试单元支持标准JTAG和串行SW两种调试方式; 16个外部中断源作为NVIC中断控制器的一部分。CPU通过指 令总线直接到FLASH取指令,通过数据总线和总线阵列与 FLASH和SRAM交换数据,DMA可以直接通过总线阵列控制定时 器、ADC、DAC、SDIO、I2S、SPI、I2C和UART。

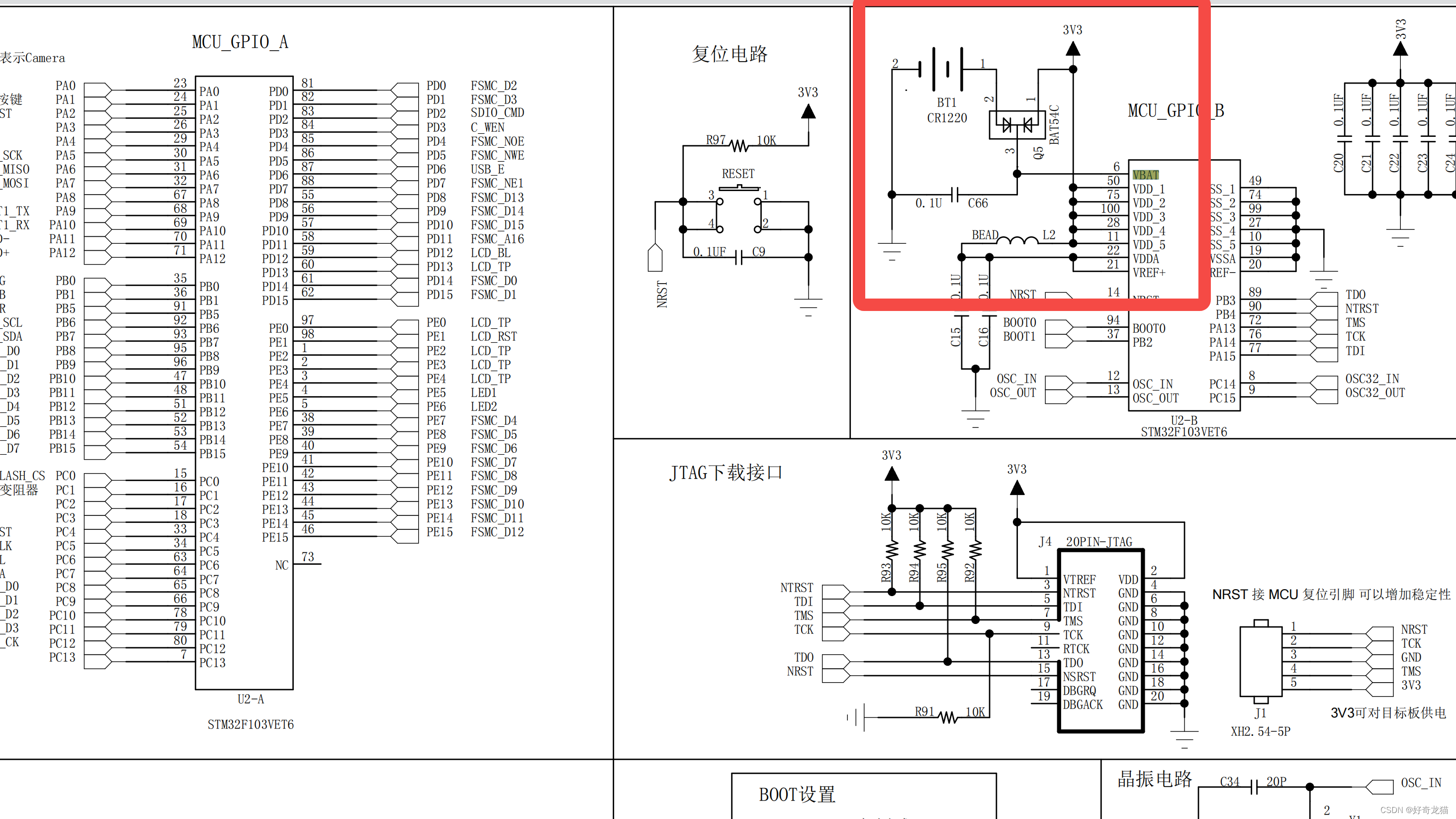

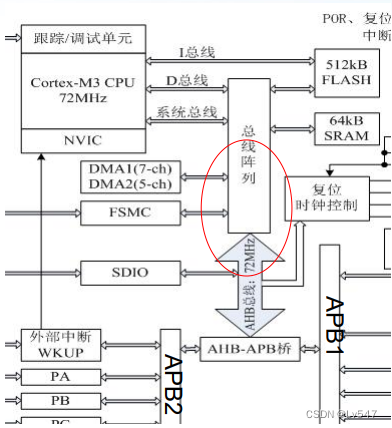

2.总线矩阵

• FLASH通过FLASH接口 连接CPU。

• 静态存储器SRAM通过总 线矩阵连接CPU

• 静态存储器控制器(FSMC) 直接与总线阵列相连接

• Cortex-M3内核CPU通过总 线 阵 列 和 高 性 能 总 线 (A H B)以及A H B-A P B (高级外设总线)桥与两 类 A P B 总 线 相 连 接 , 即 APB1总线和APB2总线。

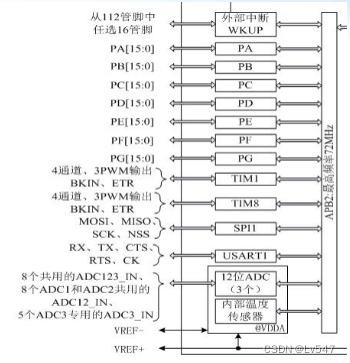

3.高速外设挂在APB2总线上

其中,APB2总线工作在 72MHz下,与它相连的 外设有外部中断与唤醒 控制、七个通用目的输 入输出口(PA、PB、PC 、PD、PE、PF和PG)、 定时器1、定时器8、 SPI1、USART1、3个ADC 和内部温度传感器。其 中,3个ADC和内部温度 传感器使用VDDA电源。

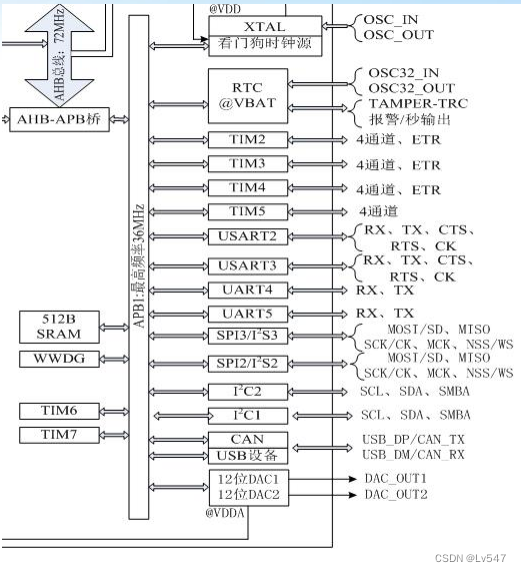

4.低速外设挂在APB1总线上

APB1总线最高可工作在36MHz 频率下,与APB1总线相连的 外设有看门狗定时器、定时 器6、定时器7、RTC时钟、定 时器2、定时器3、定时器4、 定时器5、USART2、USART3、 UART4、UART5、SPI2(I2S2 )与SPI3(I2S3)、I2C1与 I2 C2、CAN、USB设备和2个 DAC。其中,512B的SRAM属于 CAN模块,看门狗时钟源使用 VDD电源,RTC时钟源使用 VBAT电源。

5.复位和时钟控制RCC

• STM32芯片为了实现低功耗,设计一个功能完善但却非常复 杂的时钟系统

• 各个功能模块都有专用的工作时钟源,通过管理这些时钟源 使得这些模块处于工作状态还是低功耗状态。

• 系统复位时,外设时钟默认关闭,使用任何外设前,需要开 启对应的时钟