雅特力公司的MCU有着性能超群,价格优越的巨大优势,缺点是相关资料少一些,我们可以充分利用ST的现有资源来开发它。

我用雅特力的STM32F437开发板,使用原子 stm32f407的开发板自带程序,测试串口程序,原设定串口波特率为115200,但是输出乱码,波特率改成230400,串口输出正常。

于是决心修改一下,时钟配置。主要参考《STM32f4xx中文参考手册.PDF》和RM_AT32F435-F437_CH_V2.03.pdf 。

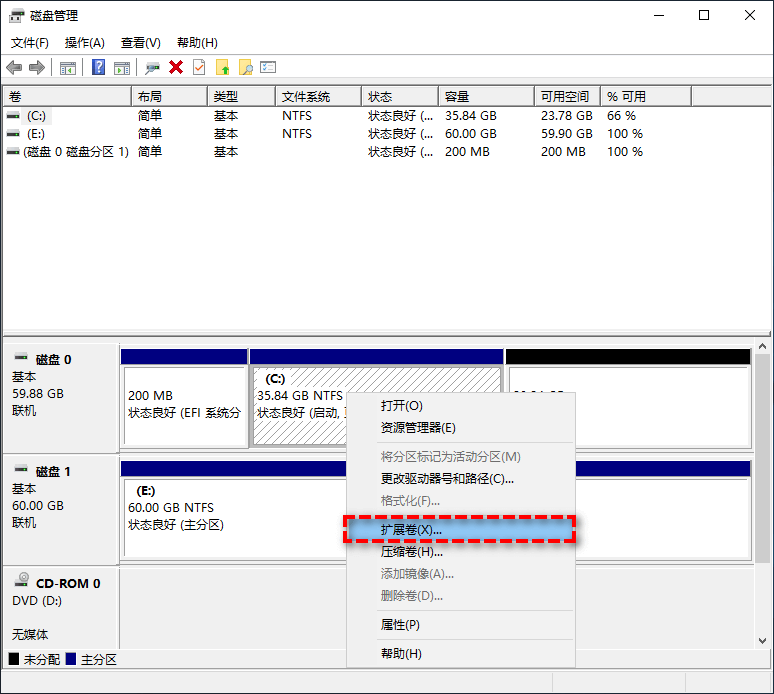

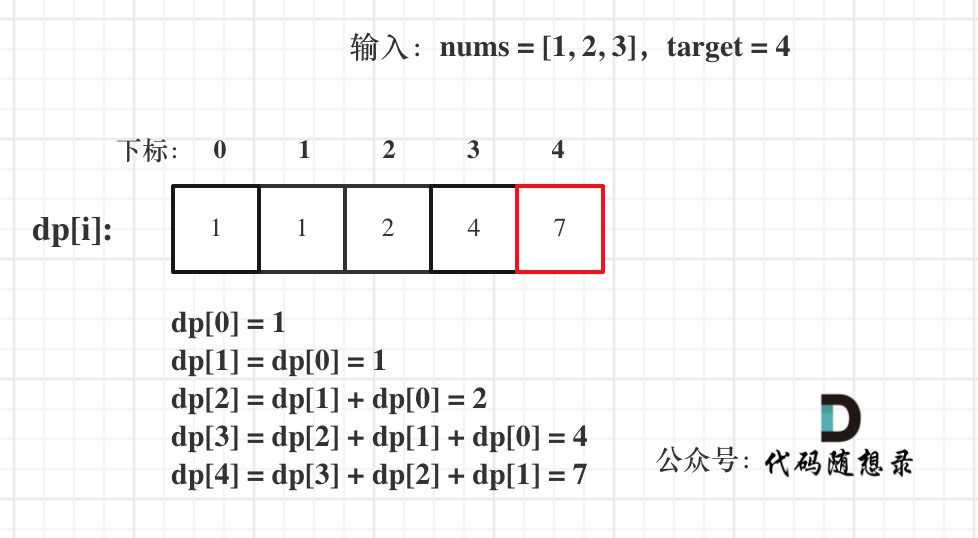

主要问题出现在RCC PLL配置寄存器(RCC_PLLCFGR)

STM32F4XX的RCC PLL配置寄存器

AT32F407RCC PLL配置寄存器

可以看到 PLL_P 只能是4/8/16/32

#define PLL_P 4 //定义为4

看到了他们的配置不同,下面开始修改代码

(1)修改SystemInit()函数。

void SystemInit(void)

{

/* FPU settings ------------------------------------------------------------*/

#if (__FPU_PRESENT == 1) && (__FPU_USED == 1)

SCB->CPACR |= ((3UL << 10*2)|(3UL << 11*2)); /* set CP10 and CP11 Full Access */

#endif

/* Reset the RCC clock configuration to the default reset state ------------*/

/* Set HSION bit */

RCC->CR |= (uint32_t)0x00000001;

/* Reset CFGR register */

RCC->CFGR = 0x00000000;

/* Reset HSEON, CSSON and PLLON bits */

RCC->CR &= (uint32_t)0xFEF6FFFF;

/* Reset PLLCFGR register */

//RCC->PLLCFGR = 0x24003010;

RCC->PLLCFGR = 0x00033002;//AT32F437

/* Reset HSEBYP bit */

RCC->CR &= (uint32_t)0xFFFBFFFF;

/* Disable all interrupts */

RCC->CIR = 0x00000000;

#if defined (DATA_IN_ExtSRAM) || defined (DATA_IN_ExtSDRAM)

SystemInit_ExtMemCtl();

#endif /* DATA_IN_ExtSRAM || DATA_IN_ExtSDRAM */

/* Configure the System clock source, PLL Multiplier and Divider factors,

AHB/APBx prescalers and Flash settings ----------------------------------*/

SetSysClock();

/* Configure the Vector Table location add offset address ------------------*/

#ifdef VECT_TAB_SRAM

SCB->VTOR = SRAM_BASE | VECT_TAB_OFFSET; /* Vector Table Relocation in Internal SRAM */

#else

SCB->VTOR = FLASH_BASE | VECT_TAB_OFFSET; /* Vector Table Relocation in Internal FLASH */

#endif

}修改配置寄存器初始值,防止硬件错误。

2.修改SetSysClock()中的配置代码

//stm32f407 原代码

/* Configure the main PLL */

RCC->PLLCFGR = PLL_M | (PLL_N << 6) | (((PLL_P >> 1) -1) << 16) |

(RCC_PLLCFGR_PLLSRC_HSE) | (PLL_Q << 24);

//修改成如下代码

/* Configure the main PLL */

RCC->PLLCFGR = PLL_M | (PLL_N << 6) | (((PLL_P >> 2) +1) << 16) |

(RCC_PLLCFGR_PLLSRC_HSE) | (PLL_Q << 24);3.修改 RCC_GetClocksFreq()和void SystemCoreClockUpdate(void)函数

将原代码:

pllp = (((RCC->PLLCFGR & RCC_PLLCFGR_PLLP) >>16) +1 ) *2;

改成如下代码

pllp = (((RCC->PLLCFGR & RCC_PLLCFGR_PLLP) >>16) -1 )* 4;4. 修改延时函数,我目前的时钟是336MHZ

delay_init(336); //延时初始化

经这样修改,串口输出和延时输出正常工作。

可以看到还有PLLQ 是不一样的,抽空处理一下,请大家期待下期!

![[Spring]初始导读](https://img-blog.csdnimg.cn/3d146fc95f02453a948cdc8e7ef47a40.png)