文章目录

- 前言

- 一、AXI(Advanced eXtensible Interface)

- 1、定义

- 2、信号

- 2.1 全局信号

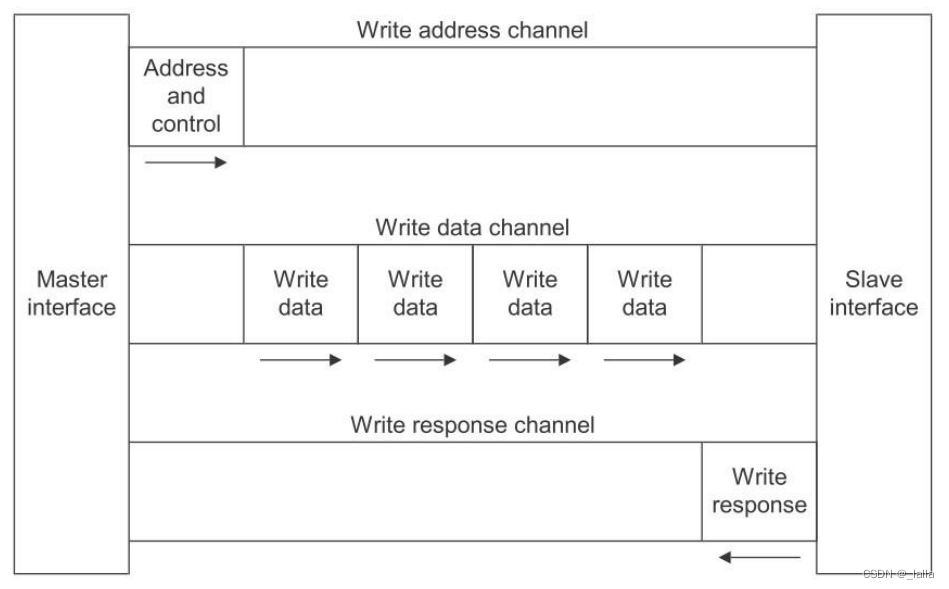

- 2.2 写数据通路

- 2.3 写地址通道

- 2.4 写回复通道

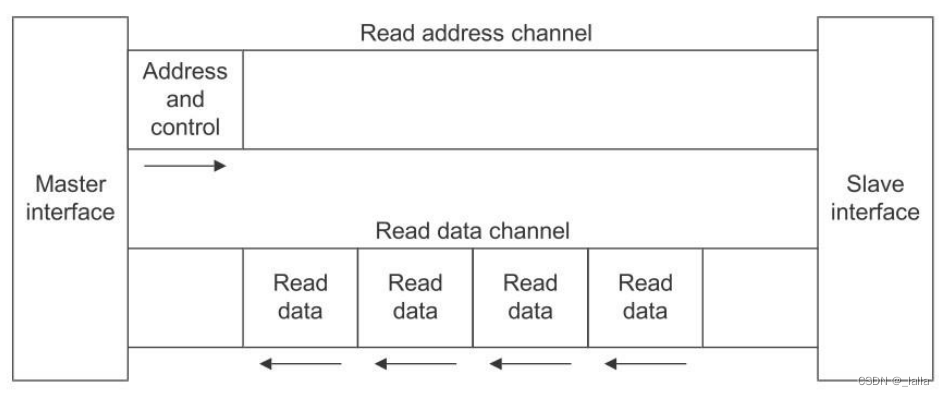

- 2.5 读数据通道

- 2.6 读地址通道

- 2.7 低功耗接口信号

- 3、AXI-Lite协议特点

- 4、读写时序图

- 4.1 读burst

- 4.2 读重叠burst

- 4.3 写burst

- 5、握手信号

- 5.1 VALID 先变高 READY 后变高

- 5.2 READY 先变高 VALID 后变高

- 5.3 VALID 和 READY 信号同时变高

- 6、不同数据通道的约束关系

- 6.1 读操作约束

- 6.2 写操作约束

前言

2023.3.25

2023.4.23

一、AXI(Advanced eXtensible Interface)

1、定义

AXI:高级可拓展接口

- 高性能、高带宽、低延迟

- 单向通道体系结构

- 独立的地址和数据通道

- 支持多项数据交换。通过并行执行burst操作,极大地提高了数据吞吐能力。

2、信号

这里介绍的信号是AXI-Lite版本的信号

2.1 全局信号

ACLK:时钟

ARESETn:低电平复位信号

2.2 写数据通路

WVALID:写有效,主机发送,握手信号

WREADY:写就绪,从机响应,握手信号

WDATA:数据

WSTRB:字节通道有效信号

2.3 写地址通道

AWVALID:握手信号

AWREADY:握手信号

AWADDR:地址信号

AWPROT:传输的特权等级和安全等级

2.4 写回复通道

BVALID:握手信号

BREADY:握手信号

BRESP:反馈信号

2.5 读数据通道

RVALID:握手信号

RREDAY:握手信号

RDATA:读数据

RRESP:反馈信号

2.6 读地址通道

ARVALID:握手信号

ARREADY:握手信号

ARADDR:读地址信号

ARPROT:传输的特权等级和安全等级

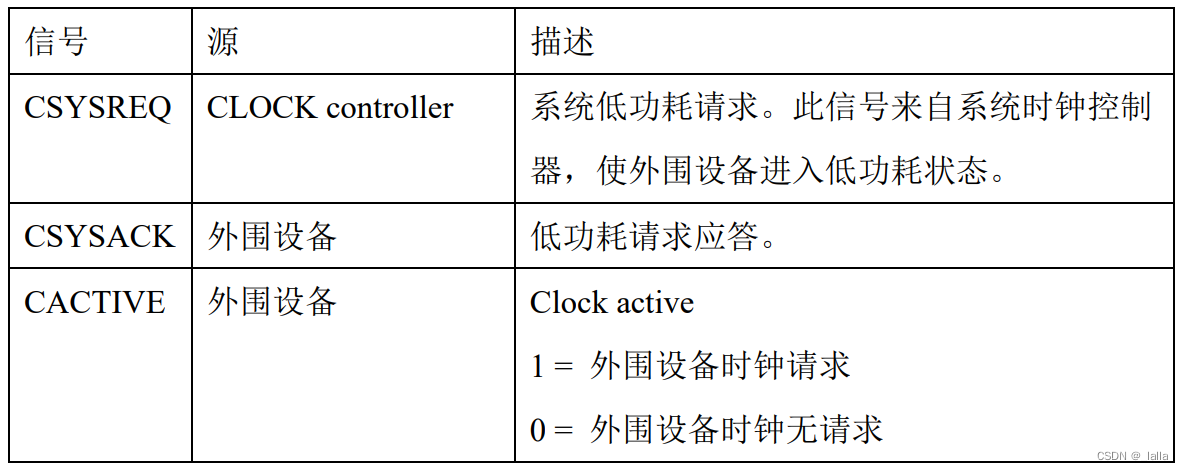

2.7 低功耗接口信号

3、AXI-Lite协议特点

- burst length的长度恒定1

- 数据的访问或读取操作需要使用数据总线的全部

- 所有的操作都是Non-modifiable和Non-bufferable的

- 不支持排他性访问

4、读写时序图

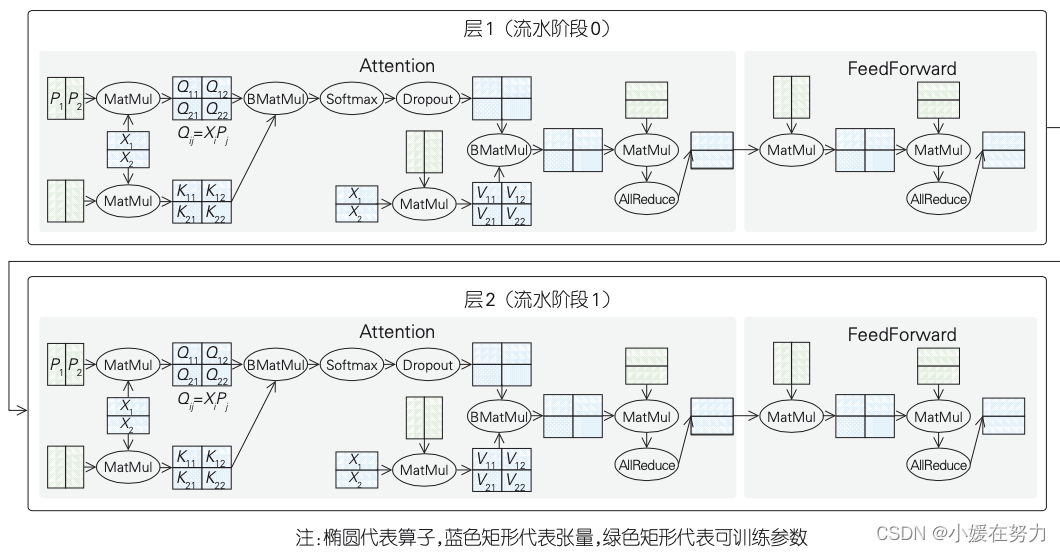

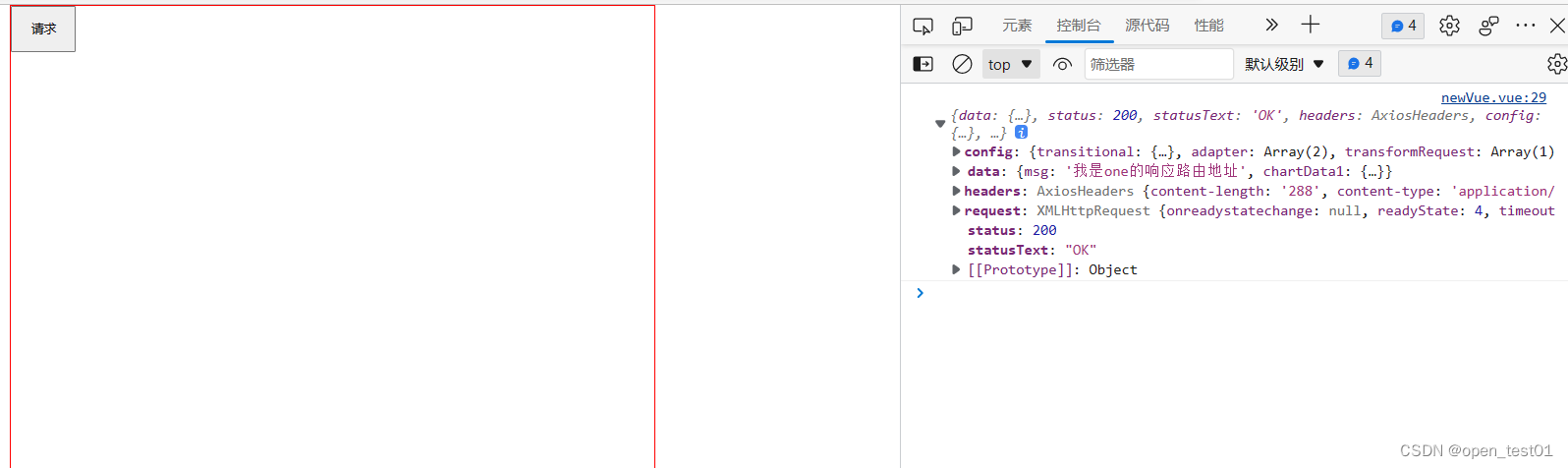

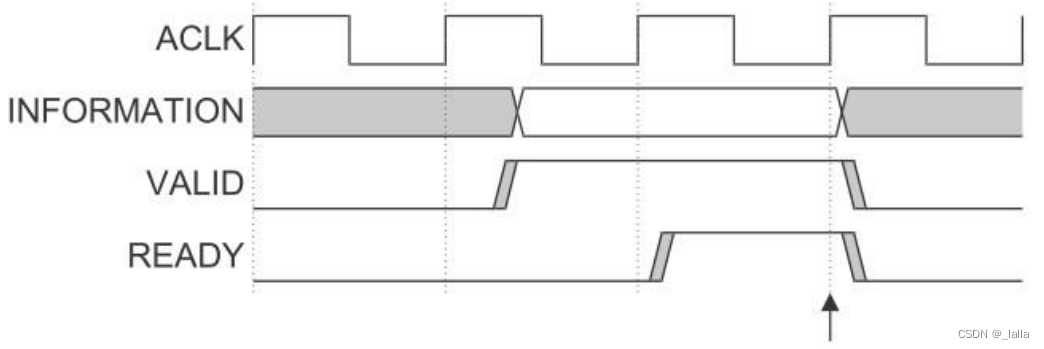

全部 5 个通道使用相同的 VALID/READY 握手机制传输数据及控制信息。

传输源产生 VLAID 信号来指明何时数据或控制信息有效。

目地源产生 READY信号来指明已经准备好接受数据或控制信息。

传输发生在 VALID 和 READY 信号同时为高的时候。

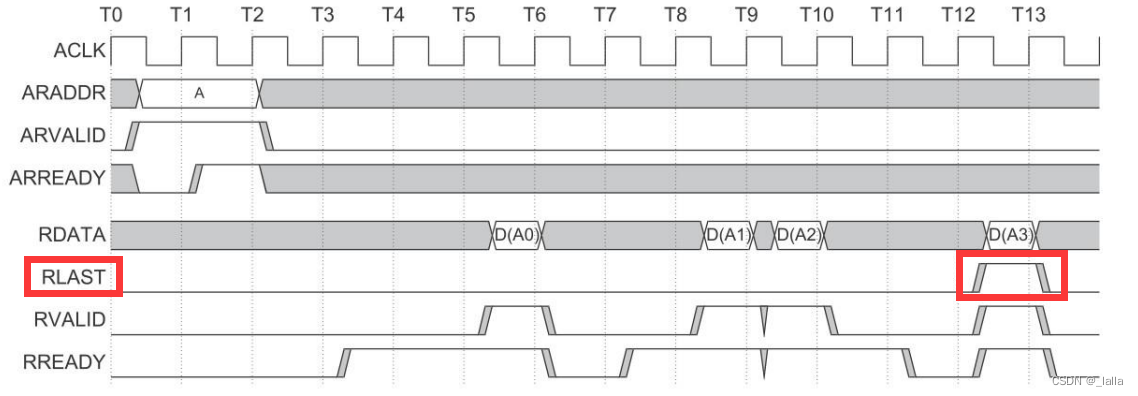

4.1 读burst

RLAST:表示最后一个传输的数据

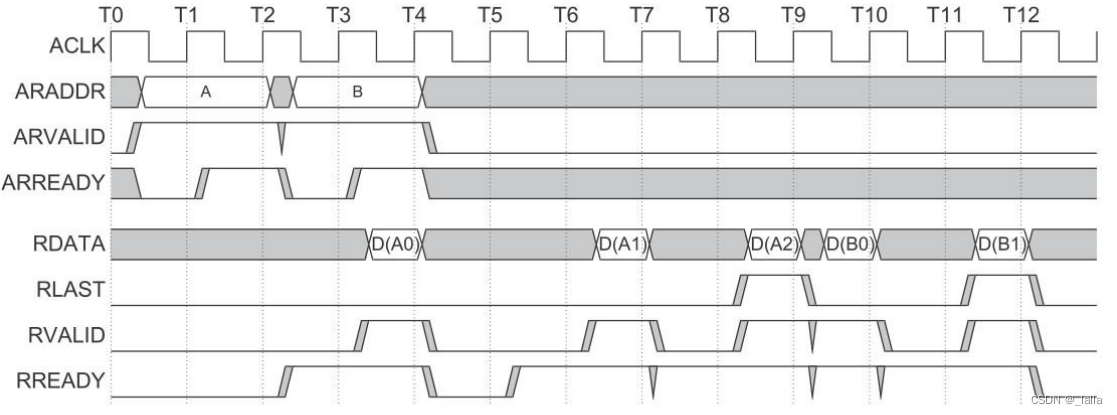

4.2 读重叠burst

主机一开始传送了两个地址给设备。设备在完全处理完第一个地址的数据之后才开始处理第二个地址的数据。

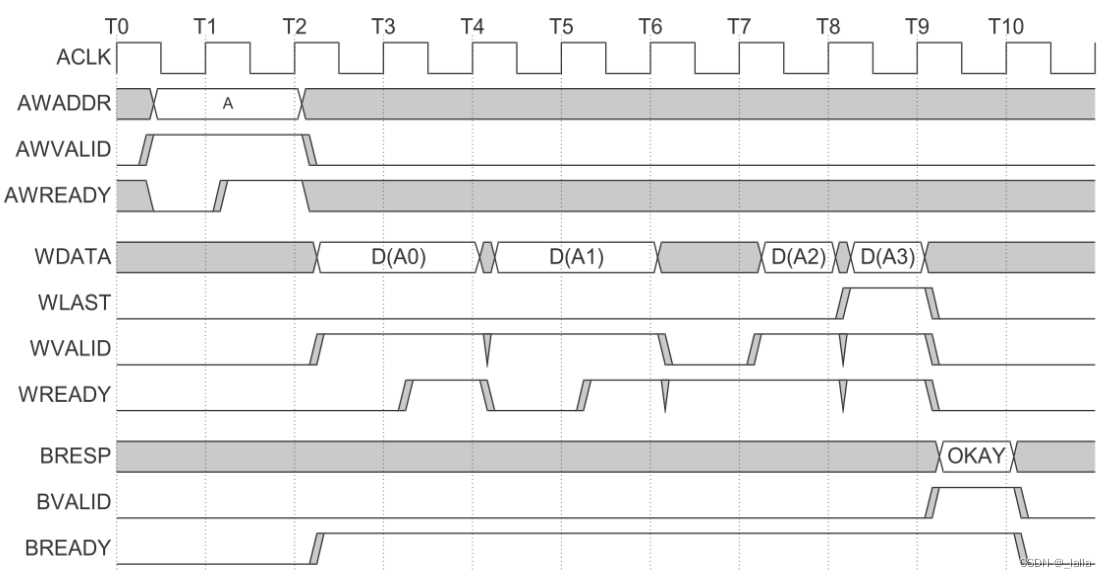

4.3 写burst

5、握手信号

-

valid和ready同时为高的时候进行数据传输

-

VALID信号一旦拉高,除非READY信号拉高接收数据完成,不会主动变低,否则的话表面此次传输失败了

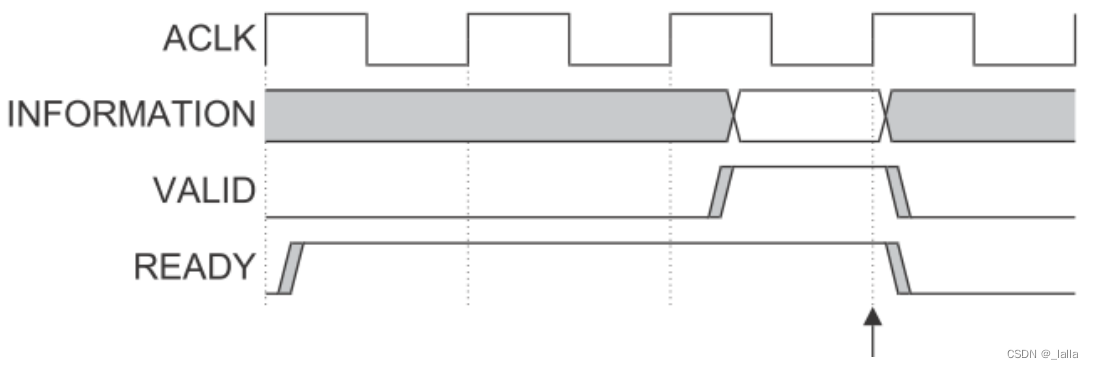

5.1 VALID 先变高 READY 后变高

主机数据先有效,后从机可以接收数据时,拉高ready

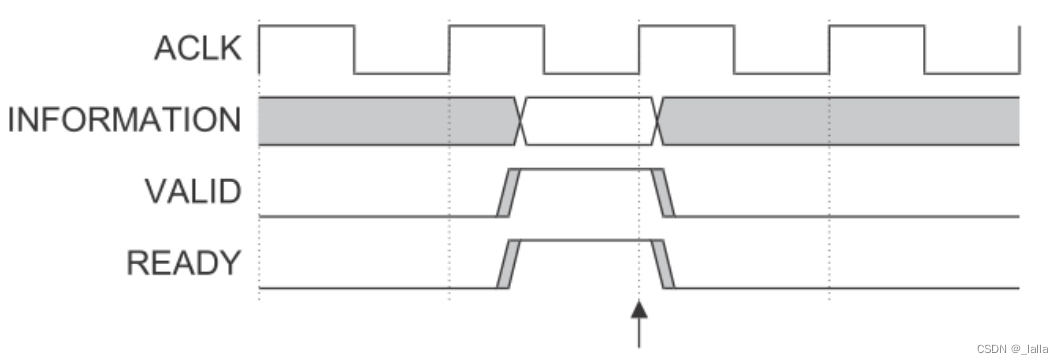

5.2 READY 先变高 VALID 后变高

从机先准备好接收数据了,后主机数据才有效

5.3 VALID 和 READY 信号同时变高

表明数据有效的同时也可以进行采样

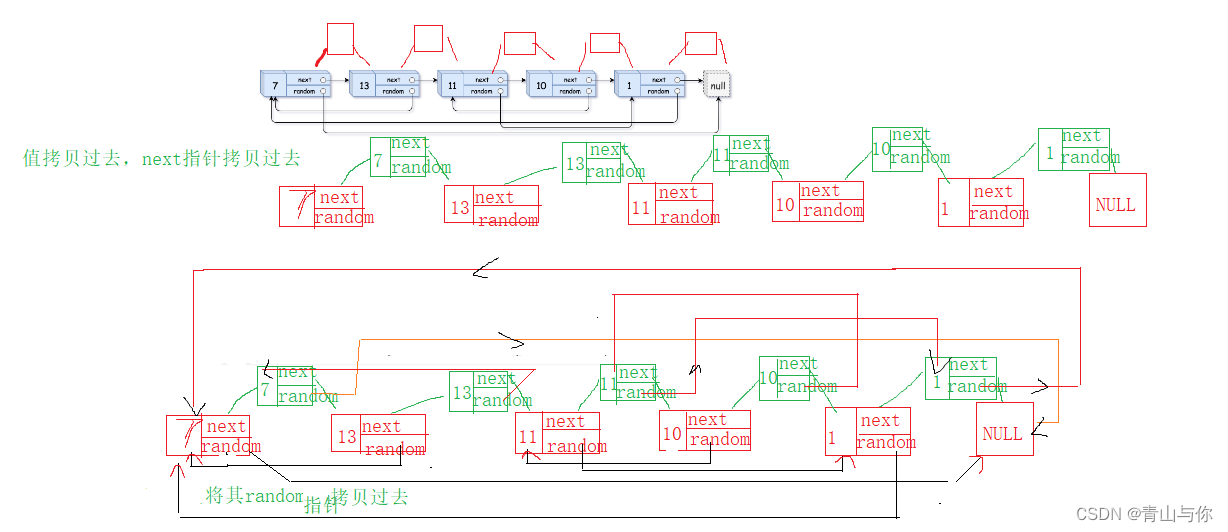

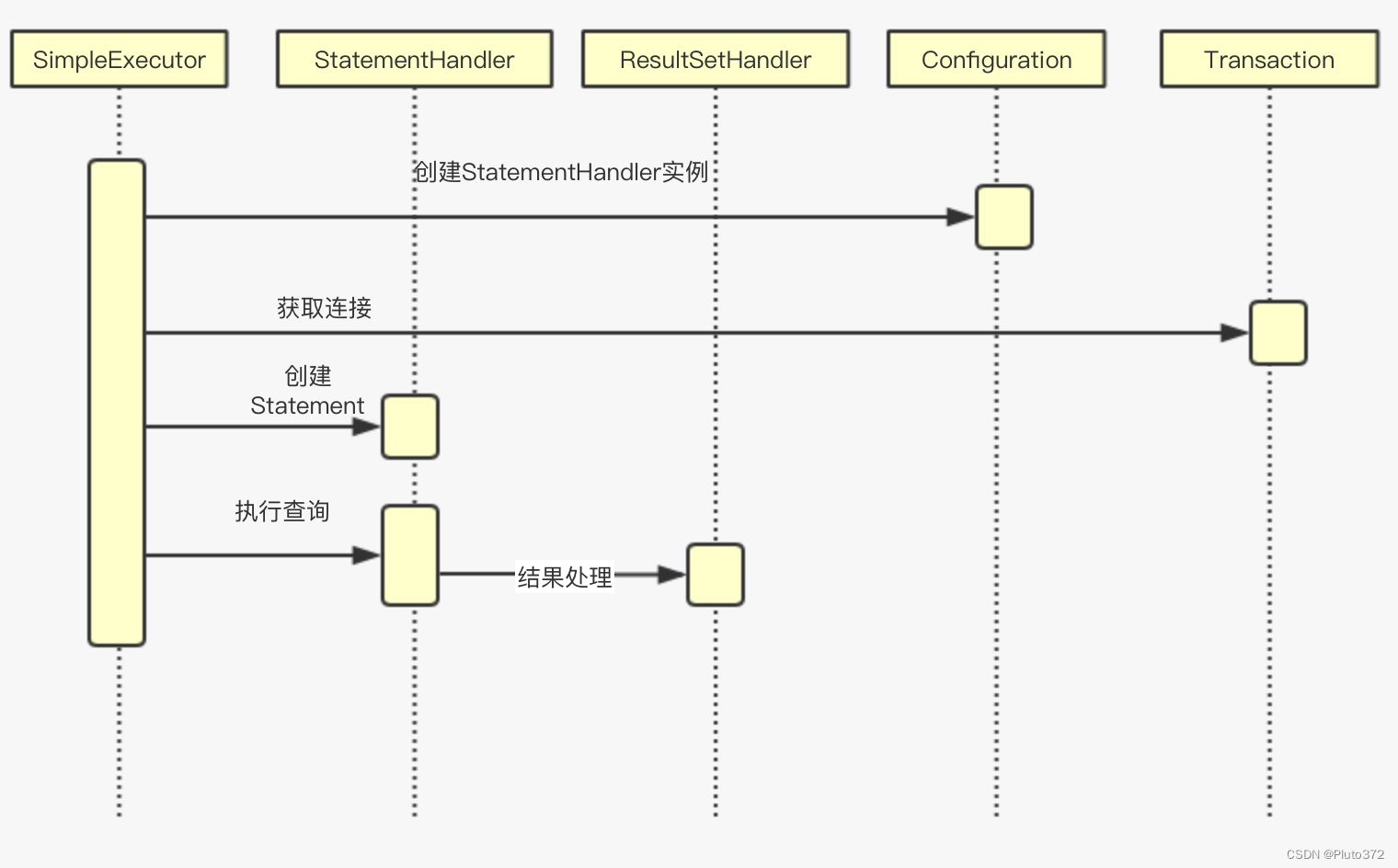

6、不同数据通道的约束关系

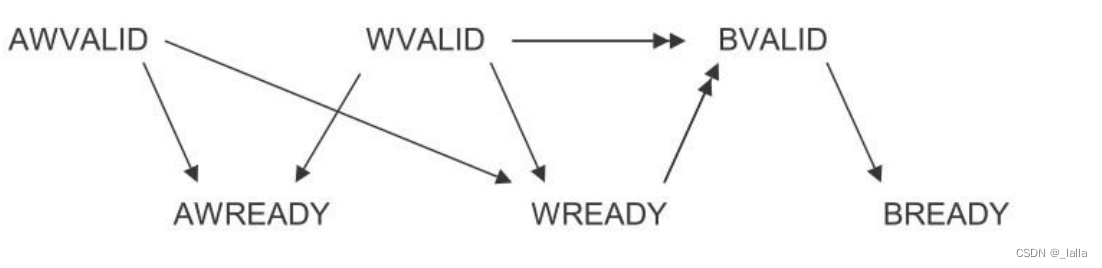

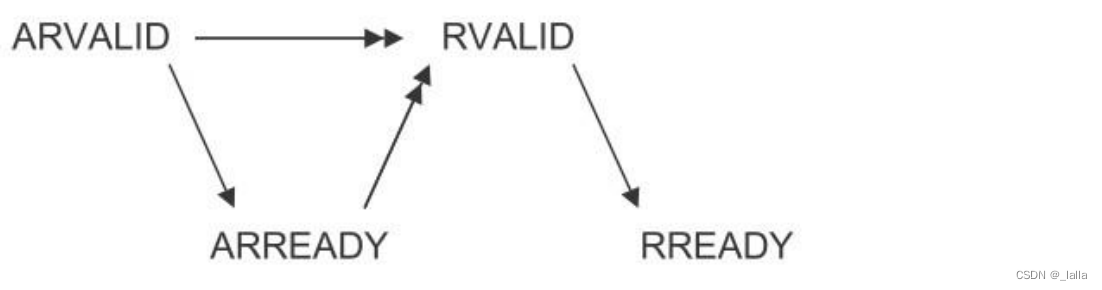

单箭头表示两者的先后顺序没有要求,双箭头表示前者必须先于后者

6.1 读操作约束

6.2 写操作约束

写回复通路的信号传递一定晚于写数据通路