我们把用于存储数据的电路叫做存储器,按照到 CPU 距离的远近,存储器主要分为寄存器、缓存和主存。我们就来重点分析这三种存储器的特点、原理,以及应用场景。

存储器是由基本的存储单元组成的,要想搞清楚存储器原理,我们还要先搞明白基本的存储单元是什么,它又是怎么工作的,我们先按寄存器、缓存和主存的顺序,逐个分析。

首先,我们来看寄存器的存储单元是什么样的。

寄存器存储单元

组合逻辑电路是指,输出仅由输入信号的状态决定的电路。而时序逻辑电路是指,电路的输出值同时依赖于电路过去的状态和现在的输入,所以时序逻辑电路中含有用于记忆电路状态的存储单元。接下来,我们就从最简单的具有存储功能的电路开始,逐步将它扩展成相对复杂的存储电路,以此来深度拆解存储电路的运行原理。

RS 锁存器

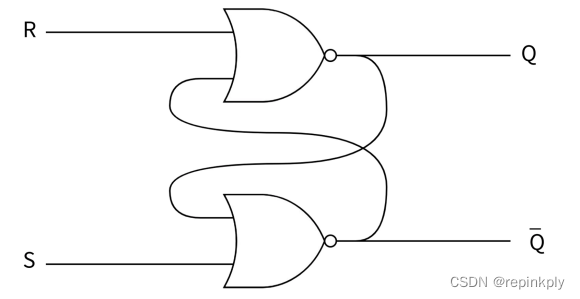

我们把具有存储信息能力的电路,称为存储器。其中,RS 锁存器 (Latch) 是最简单的一种存储器电路,它可以存储一个比特,如下图所示:

上图中的电路由两个或非门组成,它的特点是,图上方的或非门的输出作为图下方的或非门的输入,反过来,图下方的或非门的输出,也是图上方的或非门的输入。我来分析一下这个电路的特点,你就能理解这个电路是如何完成一个比特的存储的。

一开始,输入端 R 和 S 都是低电压,代表 0,上方的或非门输出为 0,下方的或非门输出为 1,这是一种合法状态。或者下方的或非门的输出为 0,上方的或非门的输出为 1,这也是一种合法状态。也就是说这个电路在 R 和 S 都为 0 的时候,有两种合法的稳定状态。

如果此时,S 变成高电压,也就是 1,那么下方或非门的输出就变成 0,进而导致上方或非门的输出变成 1,也就是 Q 变成 1。这个时候,如果 S 又变成低电压的话,因为上方或非门的输出为 1,所以下方或非门的输出仍然保持为 0。而输入端 R 仍然为 0,这就使得上方或非门的两个输入端都为 0,进而 Q 的高电压可以得到保持。

于是,我们就看到了神奇的一幕:输入端 S 变为 1 以后,可以将输出端 Q 变成 1,但是当S 变为 0 以后,输出端仍然保持 1。这就说明这个电路可以存储 1。

//未完待续....

后面再写....

![观察者设计模式(Observer Design Pattern)[论点:概念、组成角色、相关图示、示例代码、框架中的运用、适用场景]](https://img-blog.csdnimg.cn/2494a74a45d9427eb407be9fa6702265.png)