文章目录

- 前言

- 一、简要介绍

- 1、优点

- 2、缺点

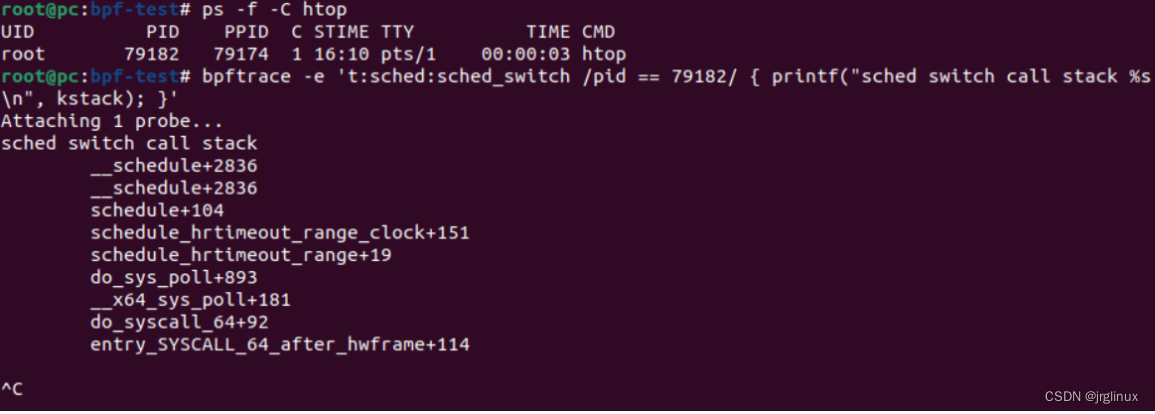

- 二、信号线和连接方式

- 1、四根信号线

- 2、连接方式

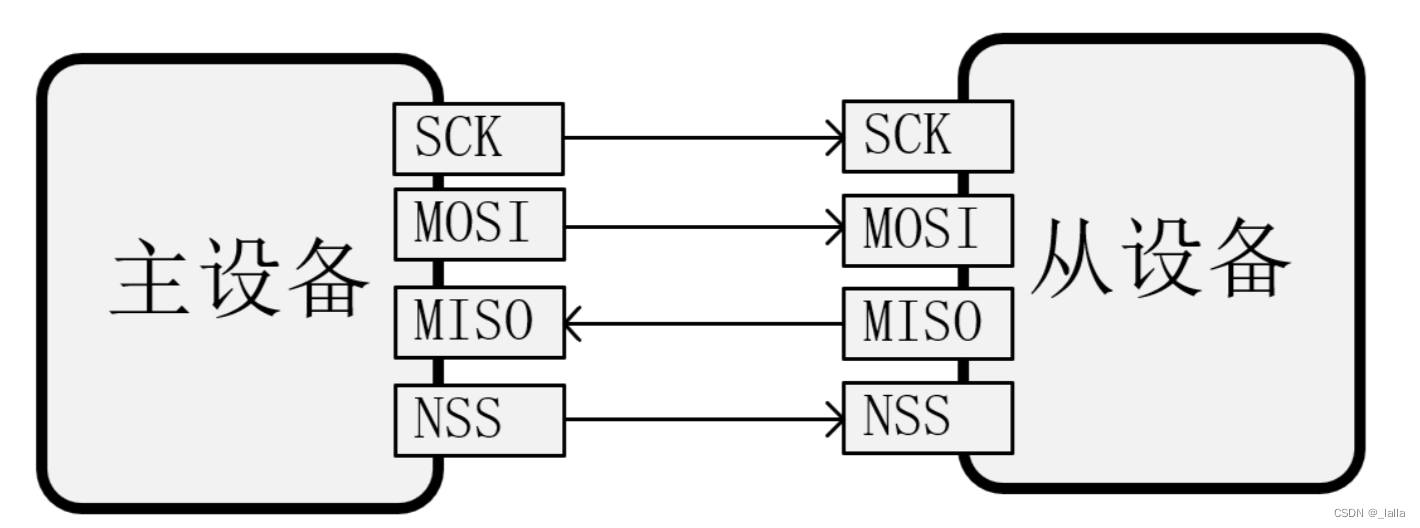

- 2.1 多NSS形式

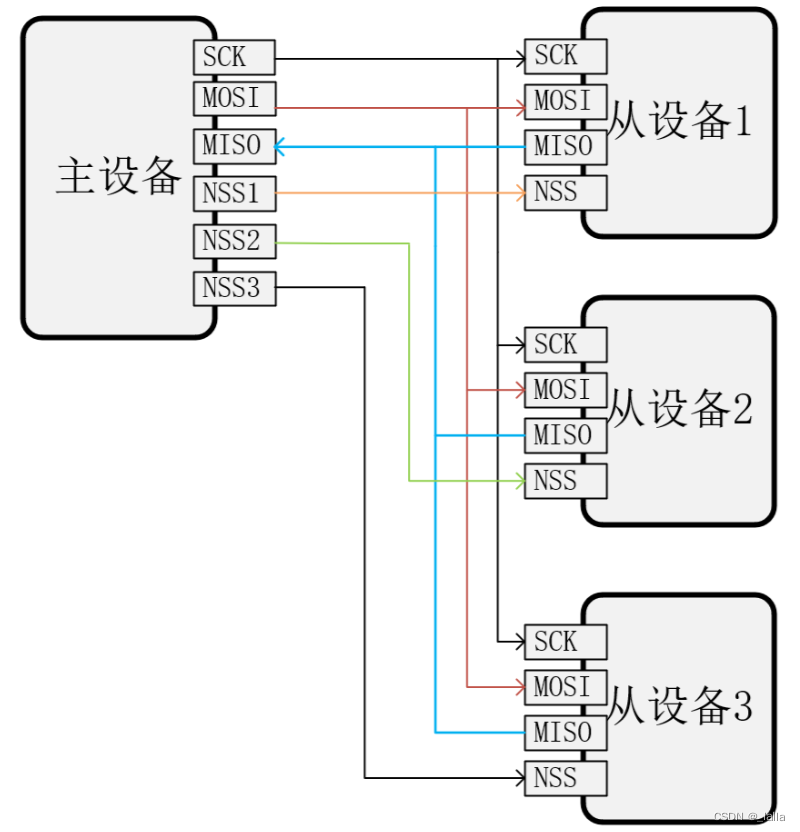

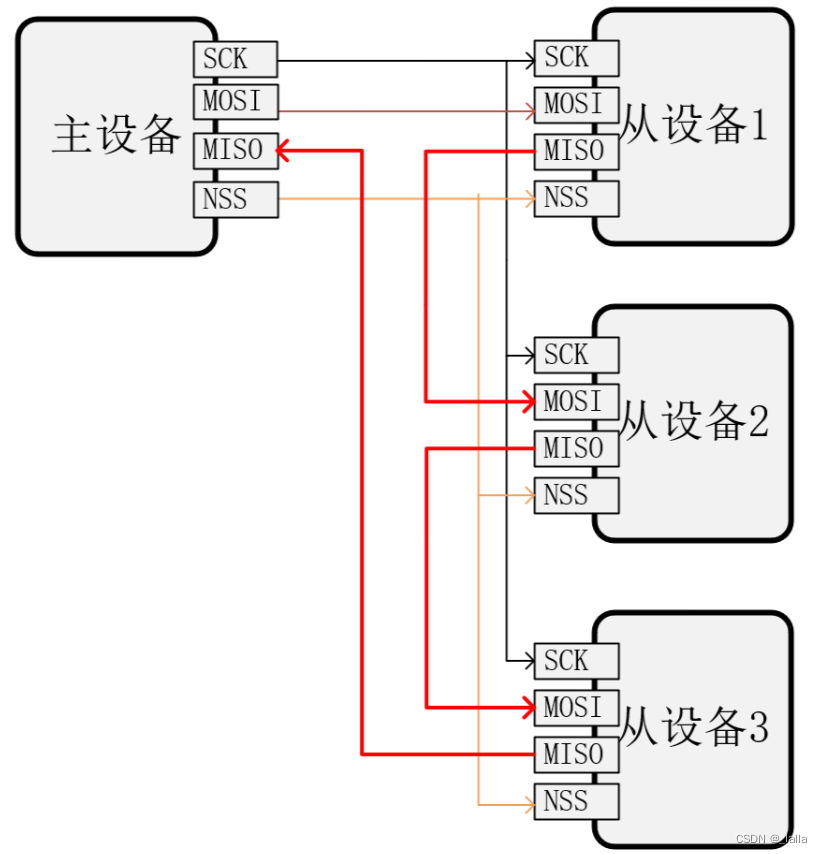

- 2.2 菊花链形式

- 三、SPI配置

- 1、时钟极性CPOL

- 2、时钟相位CPHA

- 3、四种模式

- 4、数据大小

- 5、其他配置参数

- 四、通信过程

前言

2023.4.22 阴

一、简要介绍

SPI:Serial Peripheral interface,串行外围设备接口。全双工通信,高速,可以同时发送、同时接收数据,两条独立的数据通道。

- 单向数据通路只需要一根线

- 指此总线多用来连接如“AD转换、EEPROM、PWM”等外围设备,即对应于AMBA的APB部分

1、优点

- 高速数据传输速率

- 全双工串行通信

- 灵活的数据传输,不限于8位,可以是任意大小的字

- 简单的硬件结构,不需要收发器

2、缺点

- 没有从机应答机制,主机可能在不知情的情况下无处发送

- 通常只支持一个主设备

- 需要更多的引脚

- 没有定义硬件级别的错误检查协议

二、信号线和连接方式

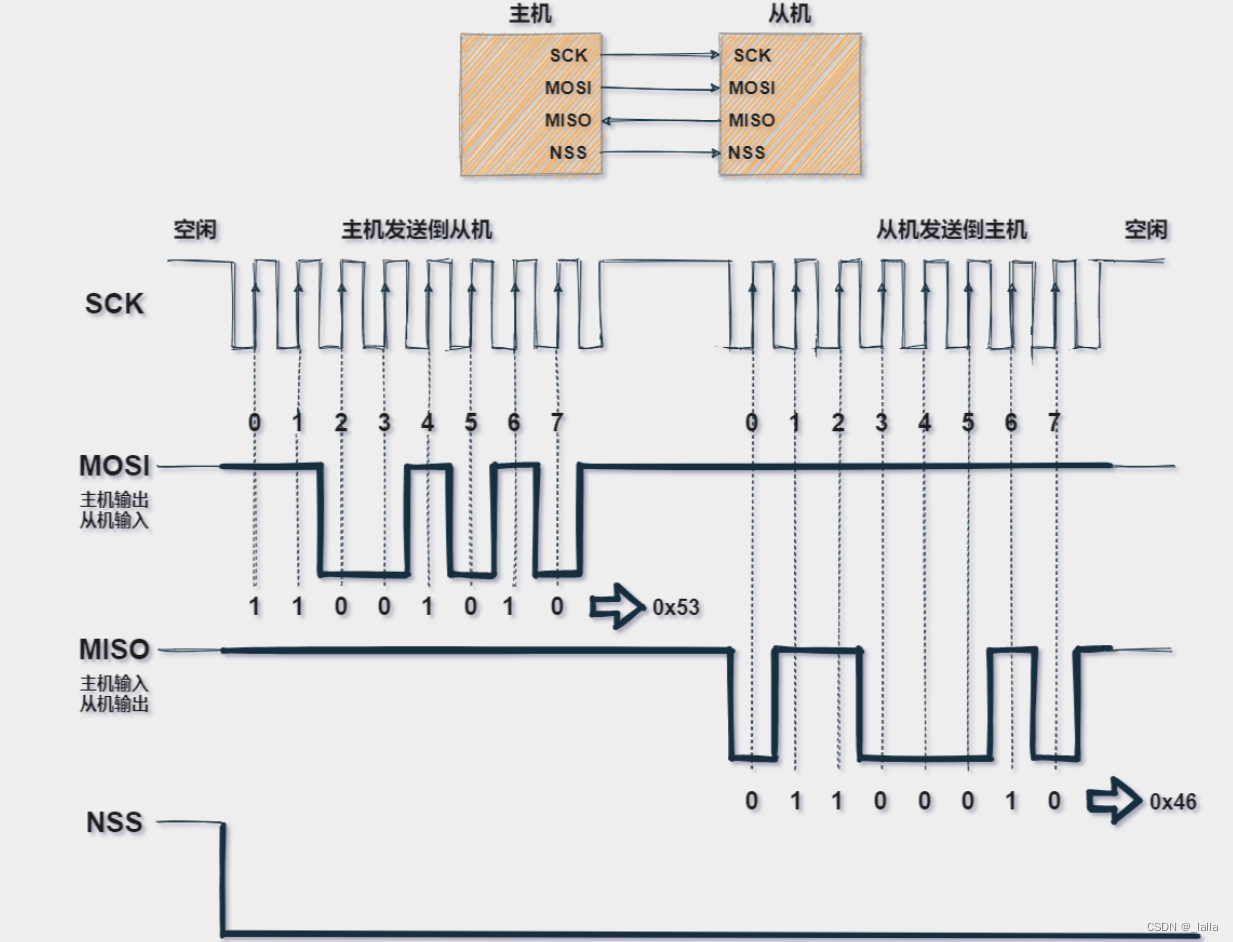

1、四根信号线

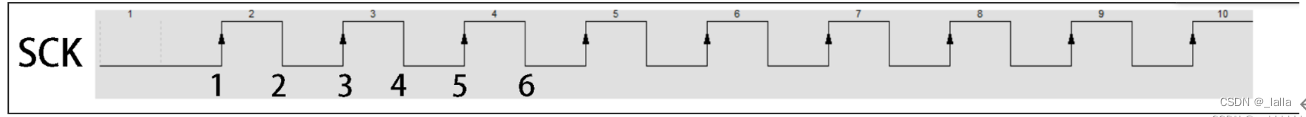

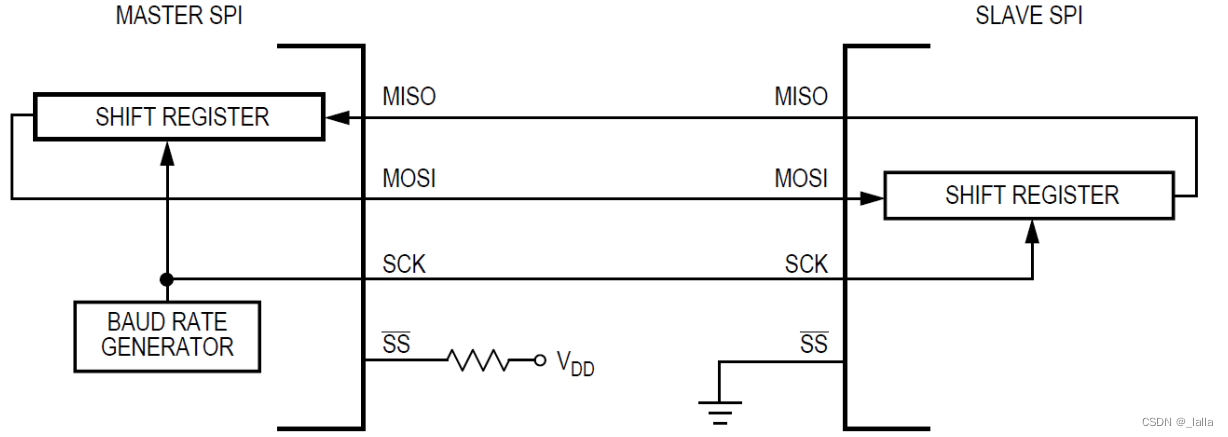

SCK:Serial Clock, 串行时钟信号,在时钟信号的边沿进行数据的传递,由主机产生

MOSI:Master output Slave input,主机发送数据给从机

MISO:Master input Slave output,主机从从机读取数据

NSS: N Slave connect,主机发送,从机接收,片选信号,使能从设备(单主机、多从机),CE,CS或SSEL。

2、连接方式

2.1 多NSS形式

三个从设备之间没有联系,主设备需要操控哪个从设备,就拉低对应NSS上面的信号,使能从设备进行数据转换

2.2 菊花链形式

三个从设备之间存在联系

比如说从设备1是一块EEPROM,从设备2是一个DSP,从设备3是一个比较器,当来自主设备的地址信号到来时,先从EEPROM中读出数据,数据放到DSP中进行处理,处理后的数据,最终在从设备3中进行比较,最后再给主设备

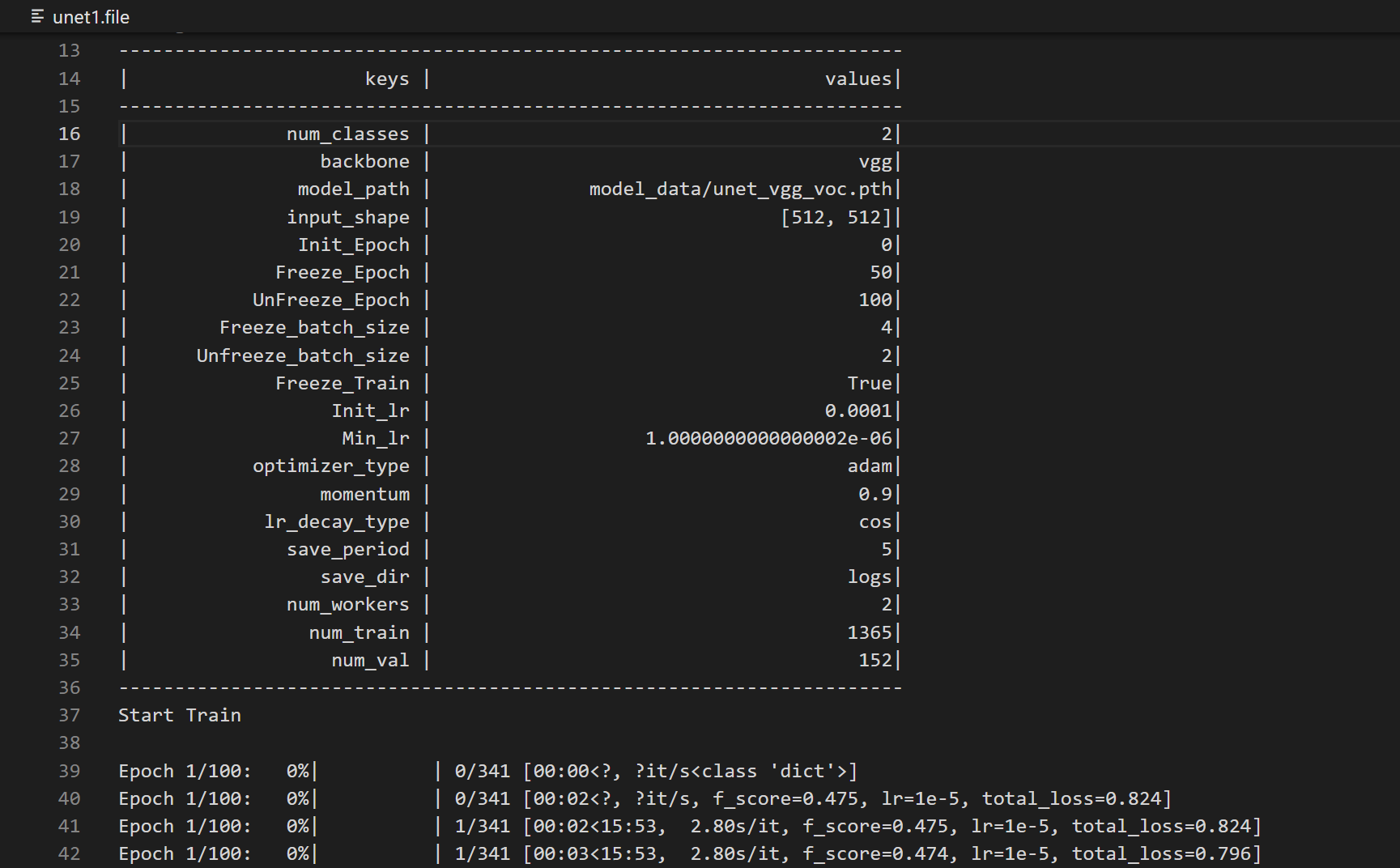

三、SPI配置

1、时钟极性CPOL

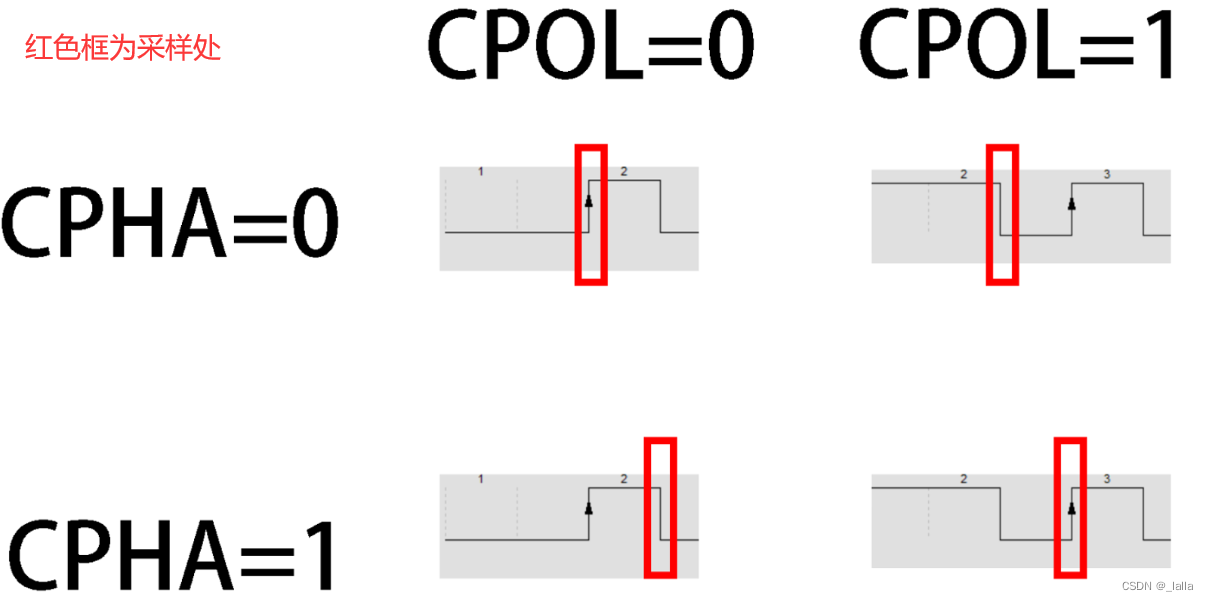

clock polarity:指通讯设备处于空闲状态(SPI开始通讯前、NSS线无效)时,SCK的状态。也就是状态机的IDLE状态是SCK为0或者为1。

- CPOL=0:空闲时SCLK=0

- CPOL=1:空闲时SCLK=1

2、时钟相位CPHA

clock phase:指数据的采样时刻位于SCK的偶数边沿采样还是奇数边沿采样

- CPHA=0:MOSI或MISO数据线上的信号在“奇数边沿”被采样

- CPHA=1:MOSI或MISO数据线上的信号在“偶数边沿”被采样

假如CPOL = 0时,CPHA=0,对应1,3,5处采样,即为上升沿采样,CPHA=1,对应2,4,6处采样,即为下降沿采样。

3、四种模式

| CPOL | CPHA | |

|---|---|---|

| 模式0 | 0 | 0 |

| 模式1 | 0 | 1 |

| 模式2 | 1 | 0 |

| 模式3 | 1 | 1 |

模式0和模式2是上升沿采样,模式1和模式1是下降沿采样

为了保持采样数据的稳定性,不违背建立时间和保持时间。

如果是上升沿采样,则在前一个相差半个时钟周期的下降沿,切换数据。

如果是下降沿采样,则在前一个相差半个时钟周期的上升沿,切换数据。

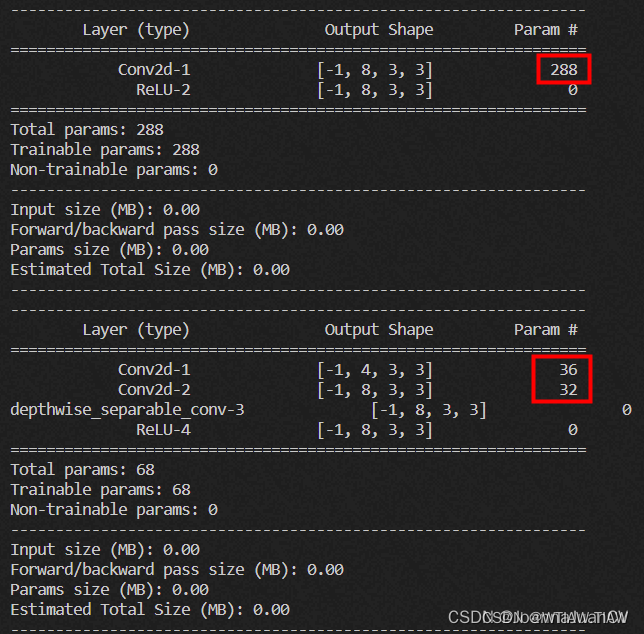

4、数据大小

数据传输的本质是两个寄存器的移位操作

5、其他配置参数

SPI_FirstBit:决定SPI是MSB还是LSB的传输形式

SPI_CRCPolynomial:决定SPI是否采用CRC校验的形式进行数据传输

SPI_Direction:传输方向,两向全双工或单向接收

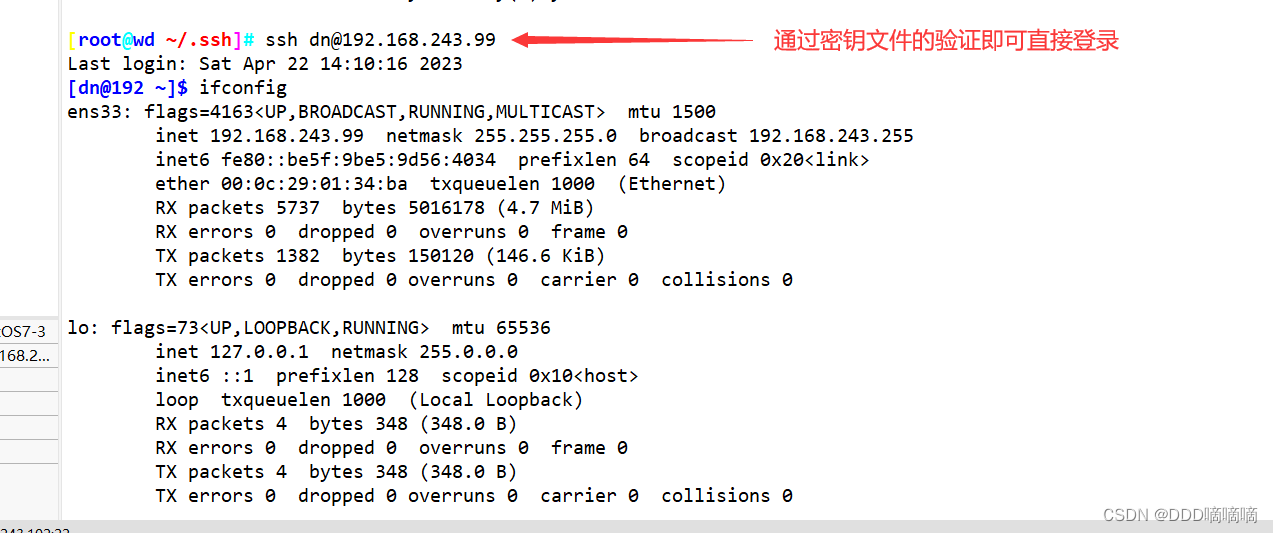

四、通信过程

拉低片选信号,当接收端检测到时钟的边沿信号时,它将立即读取数据线上的信号,这样就得到了一位数据(1bit)