SWD硬件电路设计

- 1 简介

- 2 JTAG和SWD的区别

- 2 设计要点

- 3 电路实战

1 简介

SWD(SERIAL WIRE DEBUG)是一种串行线调试,是ARM设计的协议,主要功能是对微控制器进行编程和调试。

相关引脚说明:

| PIN脚 | 描述 |

|---|---|

| SWDIO | 串行数据线,用于数据的读出和写入。 |

| SWDCLK | 串行时钟线,提供所需要的时钟信号。 |

特别地,JTAG接口和SWD接口时服用,SWD也是用J-LINK工具来实现的。所以在使用的时候需要指定使用的时那种方式,在硬件上时不需要做变更的。

2 JTAG和SWD的区别

- 共享引脚

| 20PIN | 10PIN |

|---|---|

| 20PIN 的(7 脚和 9 脚) | 10PIN 的(2 脚和 4 脚) |

|  |

- 优势不同

- SWD 引脚更少,主要 SWDIO 和 SWCLK 两个引脚;

- SWD 具有特殊功能,例如通过其 I/O 线打印调试信息;

- 与 JTAG 相比,SWD 在速度方面具有更好的整体性能;

- JTAG 协议的优势

JTAG 不仅限于 ARM 芯片,在 ARM 之外的芯片也支持;

JTAG 多种用途,用于编程,调试和生产测试;

JTAG 是一个独立的团体,他们会随着协议的发展而发展。

总结:

| 功能项 | JTAG | SWD |

|---|---|---|

| 引脚数 | 4 | 2 |

| 支持的 CPU 架构 | 支持多种架构,不仅限于 ARM | 仅 ARM |

| 功能 | 编程、调试和边界扫描以进行生产测试 | 仅编程和调试 |

| 拓扑结构 | 菊花链 | 星型 |

| 特殊功能 | 不支持 | 通过调试端口打印调试信息 |

| 硬件设计 | 尺寸和空间大 | 空间节约 |

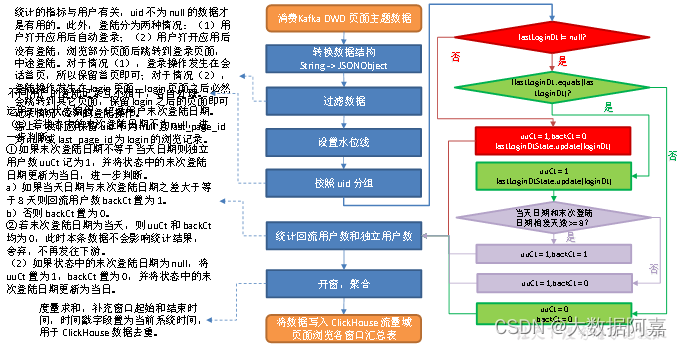

2 设计要点

- 直连即可(没有太多讲究,可以加 ESD 保护)

- PCB 建库的需注意添加标志或者是丝印标志,防止接错。

- 一般建议 SWDIO:串行数据输入输出,作为仿真信号的双向数据信号线,建议上拉 10K 电阻;SWCLK:串行时钟输入,作为仿真信号的时钟信号线,建议下拉 10K 电阻的(原因:jlink 到 SWD 接口的连接线较长导致信号不稳定,或者是Layout 做的太差,引起芯片容易被锁,或者 Debug 调试总是失败报错,建议SWD_DIO 上拉 10k 电阻,SWD_SCK 下拉 10K 电阻保证信号的稳定性。)

- 什么时候选择 SWD 而不是 JTAG:原理图设计足够简单,可以在没有 JTAG功能的情况下进行测试。

- 个人建议:要是可以 JTAG 和 SWD 都做一下。(实测,有时候 SWD 不稳定)—JTAG 的稳定性和速度要快一些。

- SWD 模式比 JTAG 在高速模式下面更加可靠。在大数据量的情况下面 JTAG下载程序会失败, 但是 SWD 发生的几率会小很多。基本使用 JTAG 仿真模式的情况下是可以直接使用 SWD 模式的, 只要你的仿真器支持。

3 电路实战

![[附源码]SSM计算机毕业设计校园兼职招聘系统JAVA](https://img-blog.csdnimg.cn/81aee4284bd4447f93a08acd4db2e58e.png)

![[附源码]Python计算机毕业设计SSM基于java的云顶博客系统(程序+LW)](https://img-blog.csdnimg.cn/e1d7260655a6401391a73ec98e69d673.png)