还君明珠双泪目,恨不相逢未嫁时

文章目录

- 前言

- 7.3.2 中断的作用和原理

- 7.3.3 多重中断

- 7.3.4 程序中断方式

- 7.3.5 DMA 方式

前言

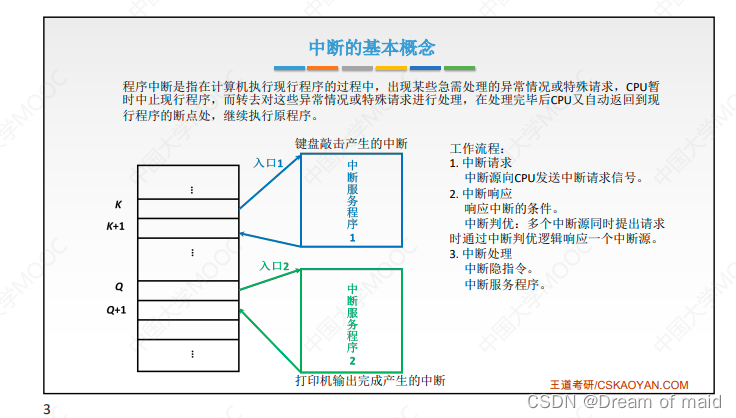

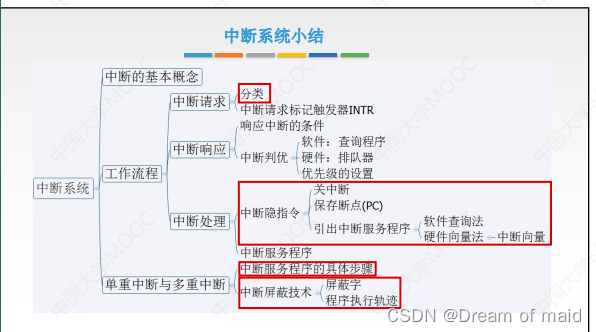

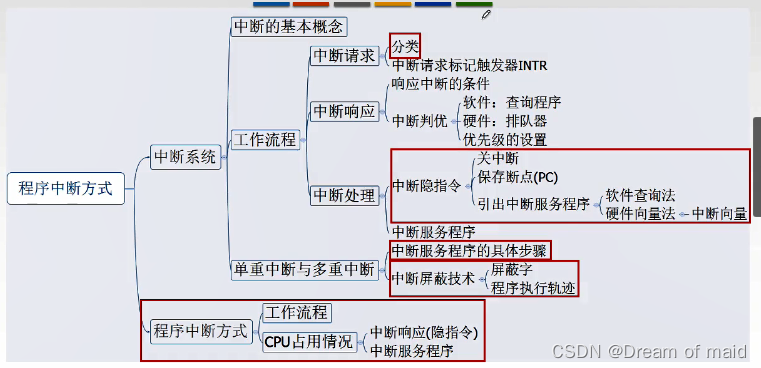

本节除了对时间的计算考察比较多之外,其他的方面也有考察,同时中断的考点在操作系统中也有考察,机组里面更多的关注中断系统工作的硬件原理,首先我们先看一下中断的基本概念,它在系统中有什么作用 ,然后掌握CPU除了中断的这个流程,每一步需要做什么操作,需要用什么硬件,然后我们还要学一下单重中断和多重中断,最后我们来介绍一些程序中断方式

7.3.2 中断的作用和原理

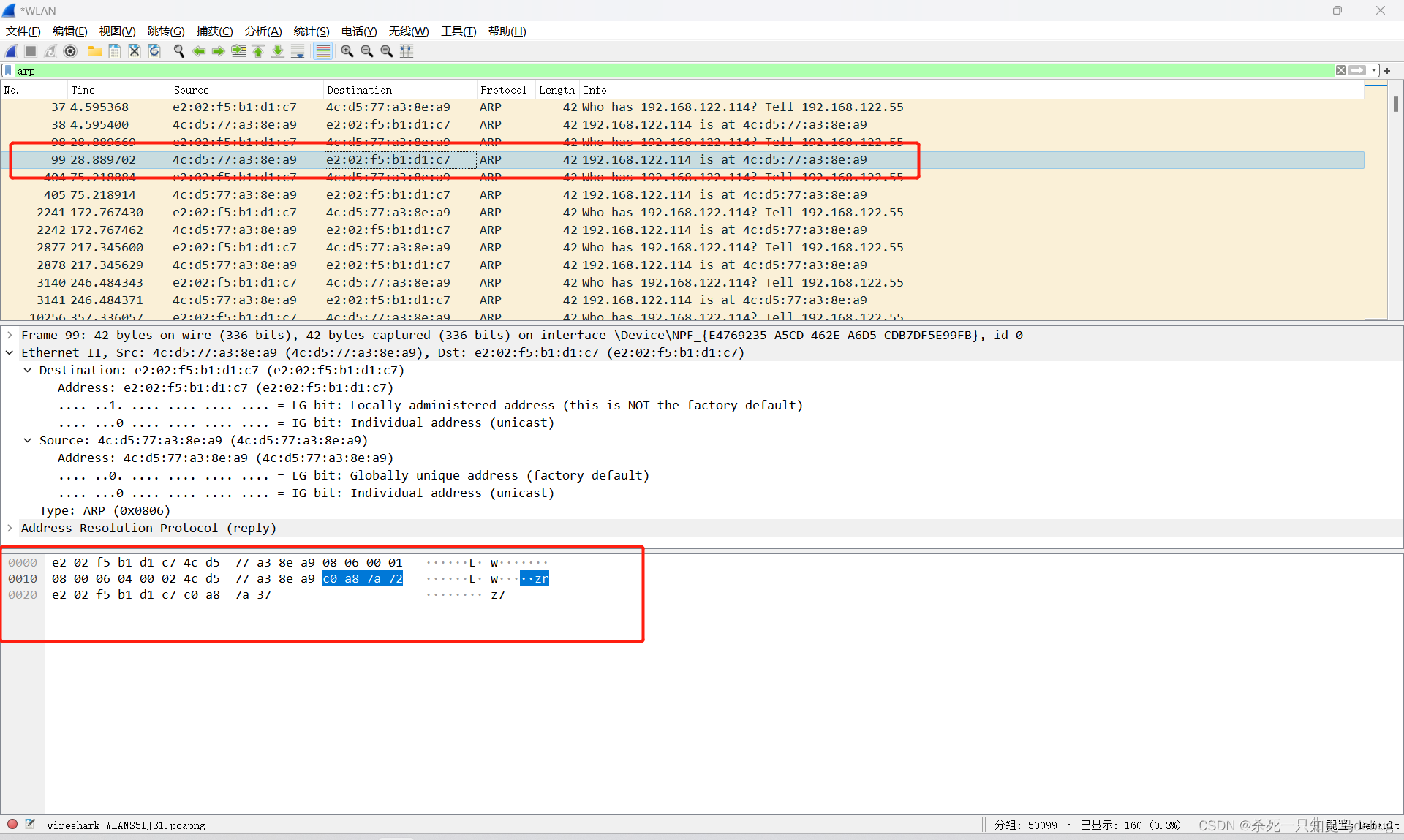

中断的基本概念

程序执行指令就是使用一个PC指向当前要执行的指令的地址,取出这个指令之后要让这个指令加一,指向下一个要执行的指令,因此正常情况下CPU对指令的执行是顺序执行的,除非遇到跳转指令或者函数调用的指令,即便是跳转指令或者函数调用指令,但是依然是属于同一个进程,若这个进程的指令序列开始上CPU运行了,那么也就意味着这个进程会一直霸占着CPU 除非这个进程自主的结束,但是根据我们使用经验来说CPU除了处理当前正在运行的进程 还要处理我们的输入输出设备发来的信号, 这正是因为有中断系统,CPU每执行往一个指令之后,都会在这个指令末尾进行一次检查是否有中断请求信号 ,然后去处理这个中断服务程序,对于不同的中断请求,我们要使用不同的中断程序来处理

关中断:当CPU处于关中断状态时,是不会处理中断程序的(这个关中断状态会被记录于PSW中,执行原子操作(几个语句不可分割)的时候就可以在第一条中加上一个关中断指令,将PSW中的IF变为0,但是也有一些指令在关中断时也需要被响应,比如关机)

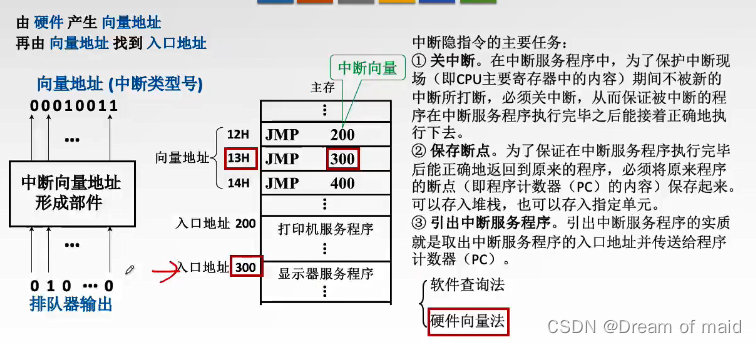

中断隐指令:把CPU的指令执行流转移到正确的一个中断服务程序,本质上就是修改一个PC的值,让PC指向这个中断服务程序的第一个指令

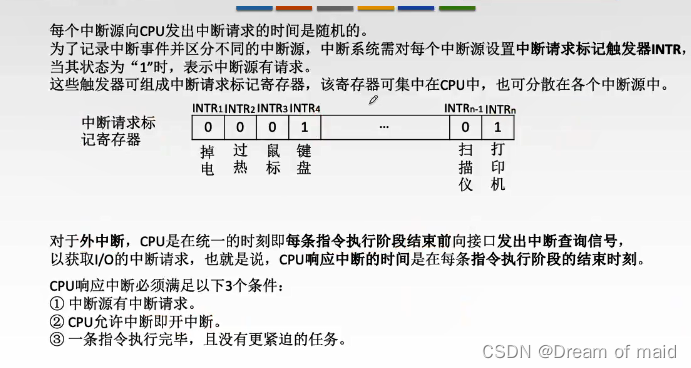

中断请求标记

检测到一个中断请求,应该如何判断是哪一个IO设备发出来的?这里解决方式是设置一个中断请求标记寄存器,这个寄存器是由一个个的触发器组成的,但是有的时候会有多个部件发过来的请求信号,

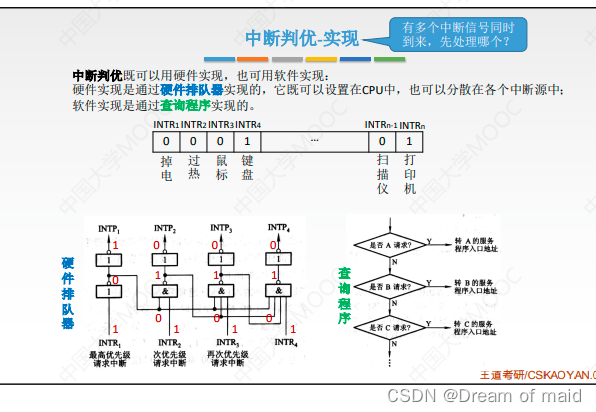

中断判优

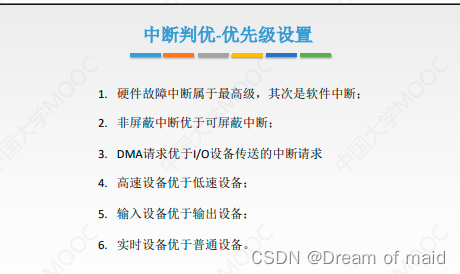

中断判优,优先级设置

第4个:高速设备你响应的越慢,越耽误工作,低速设备的反而没有事情

第5个:键盘输入信息放在缓冲寄存器中,若是不及时取走的话,可能会数据覆盖,

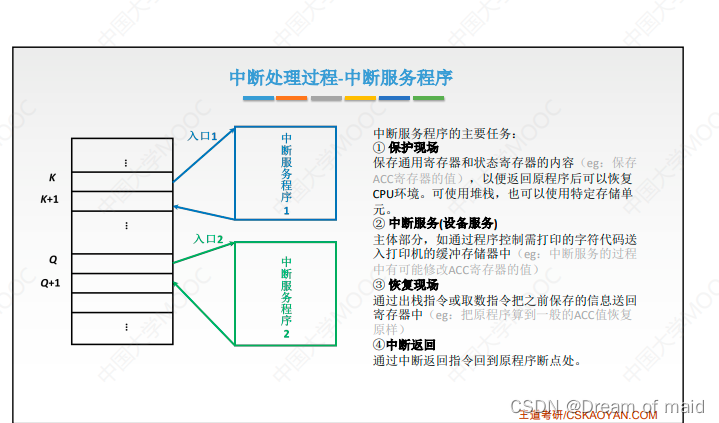

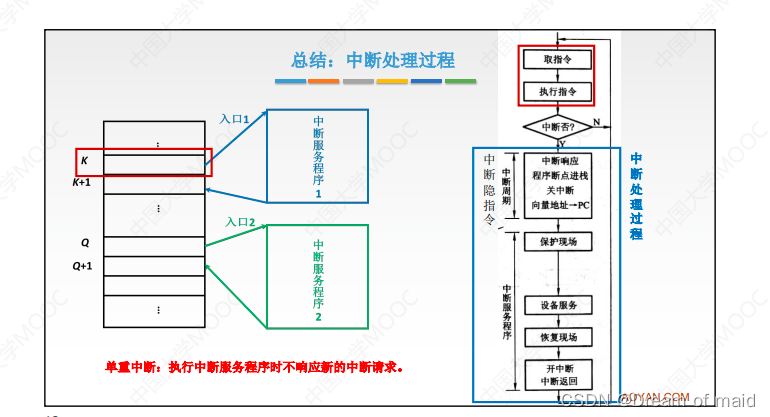

中断处理过程

当程序执行流需要改变的时候,我们需要保留PC的值,这个操作可以交给中断隐指令(是多个指令,不是一个指令),保存原程序的PC值,并让PC执行中断服务程序的第一条指令,这里有两个问题,首先保存的PC值保存在哪里,还要就是是如何找到的中断服务程序的第一条指令(两种方式,软件查询法,硬件向量法)这里我们主要分析硬件向量法,我们可以给每一个中断请求信号进行编号,之前我们说过通过排队器(也就是多个触发器的那个)判断是那个中断源发来的信号,经过中断向量地址形成部件会形成一个向量地址,中断向量指的是函数的指针 如这里的JMP 后面的200 对应入口地址200,向量地址可以理解为指针的指针,你可能回想为何向量地址不直接与入口地址对应,若是直接与入口地址对应,那么中断服务程序的长度也就不能变化了,若是使用二级指针,我们的中断类型是一定的,并且一一对应的关系好确定,我们也只需要修改JMP 后面的便可

本节回顾

这里中断服务程序中也是有一个关中断,一个开中断,这也就保证了中断服务程序是一气呵成的,这也就是单重中断

7.3.3 多重中断

也就是在执行某个中断程序的时候,依然允许执行其他的中断服务程序

如果我们把开中断安排在保护现场的前面,也就有可能主程序的现场我们只保存了一半,又被新的中断程序中断了,导致主程序的以前的运行现场丢失

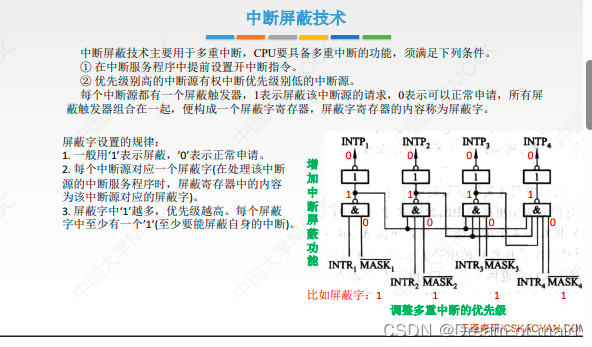

屏蔽字:用来屏蔽某些中断的,本质上也是来出来优先级的问题

中断屏蔽字

例题

本节回顾

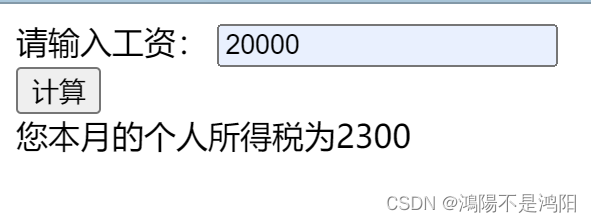

7.3.4 程序中断方式

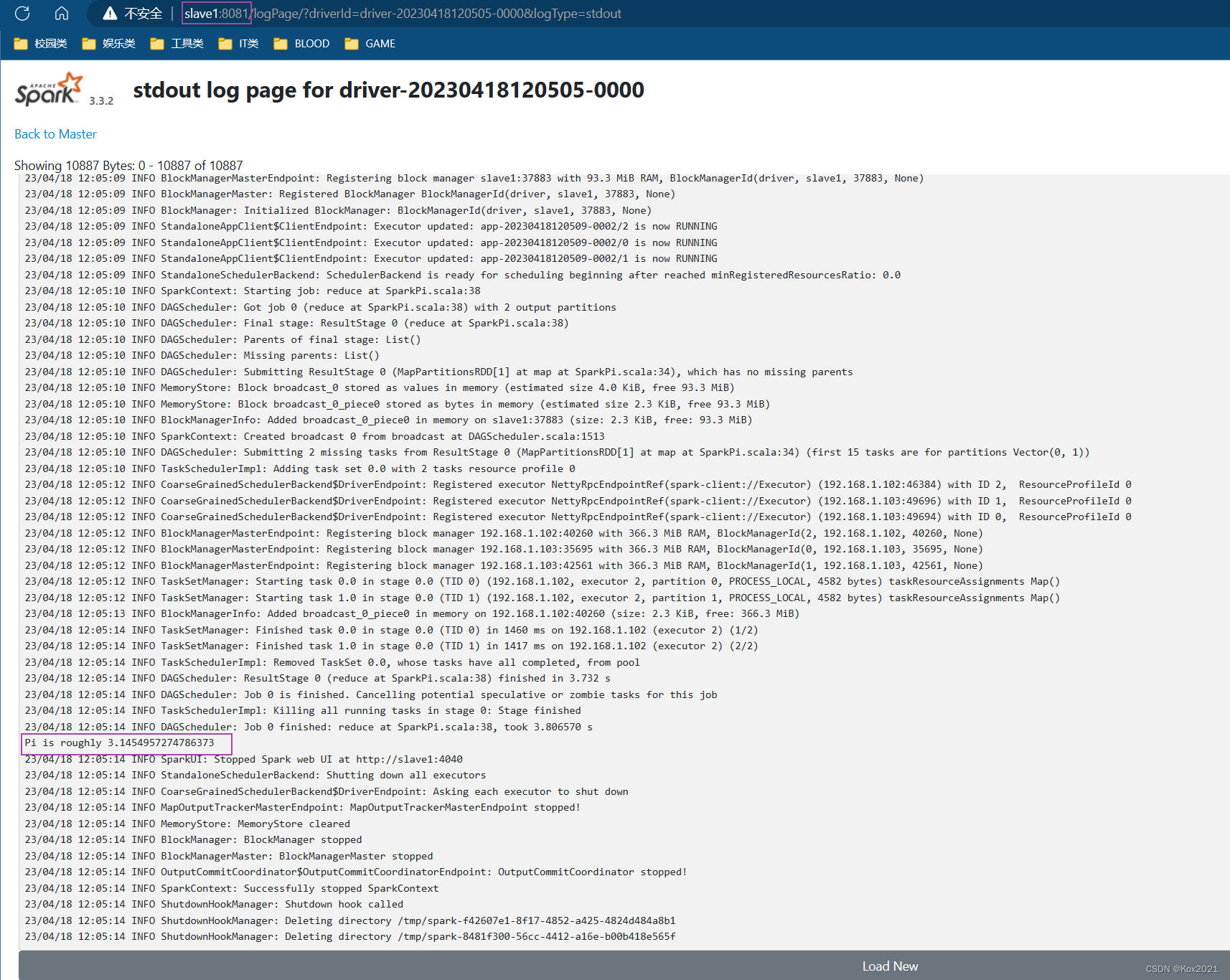

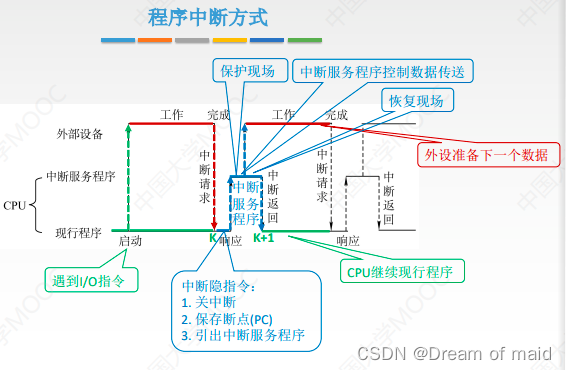

引入中断系统之后,如何控制IO 设备的读写工作,假设CPU正在运行一个外部设备,而这个设备正在等待输入,CPU需要通过IO指令发出启动输入的命令,外部设备就去准备CPU所需要的信息,若是对于程序查询方式,CPU需要不断轮询IO设备是否需要已经输入工作

而引入了中断系统之后,CPU会继续干以前的事情,当IO设备完成工作之后,IO设备会给CPU发送一个中断请求信号,假设之前CPU运行的那条指令的地址是K ,在K这个指令的末尾 检测到了中断请求信号,此时就要对中断请求信号进行处理,当CPU处理完这个中断之后,就会到K+1这个地址,其中的中断处理的过程,需要一个中断隐指令完成一系列的操作

在中断服务程序中,首先需要保存以前的现场(各种寄存器的值,还有屏蔽字),然后正式的对中断服务进行处理,在这时间,CPU已经取走了第一个数据,然后继续给IO设备发送输入指令,引入了中断服务程序之后,CPU与外部设备就可以并行

本节回顾

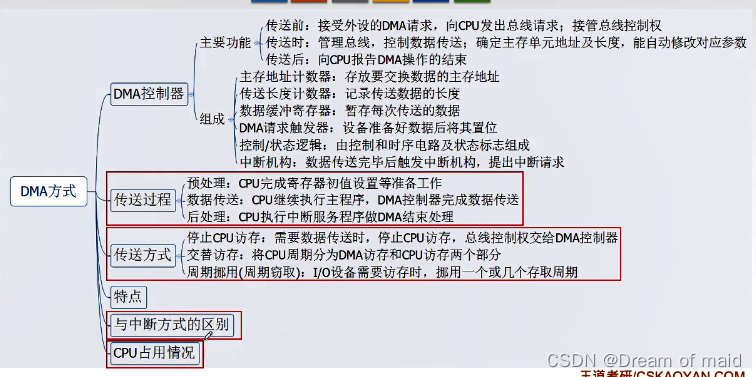

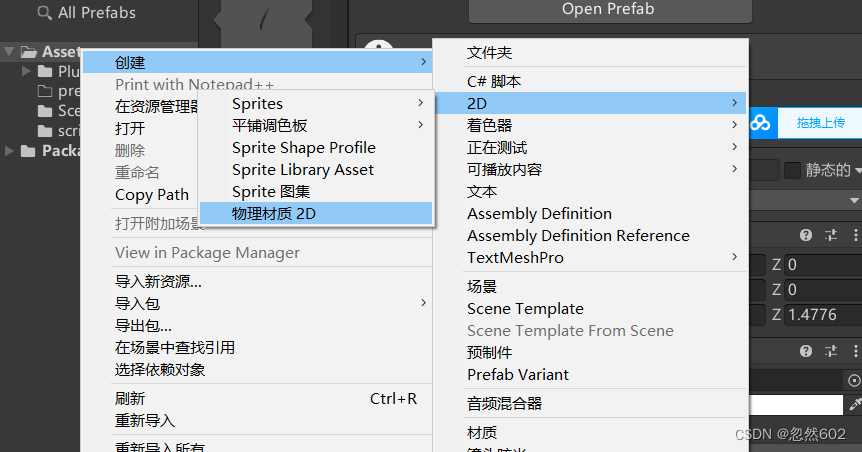

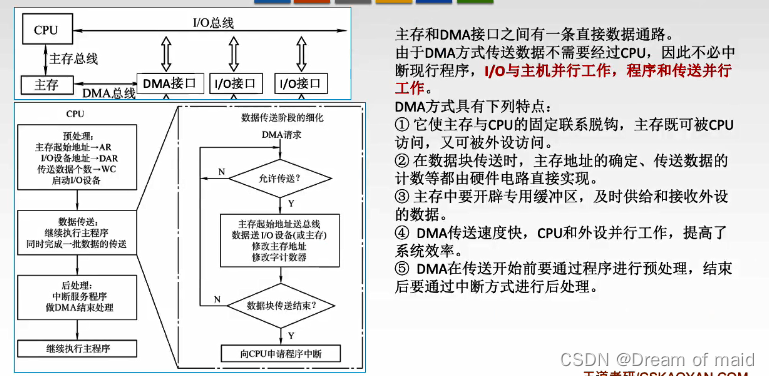

7.3.5 DMA 方式

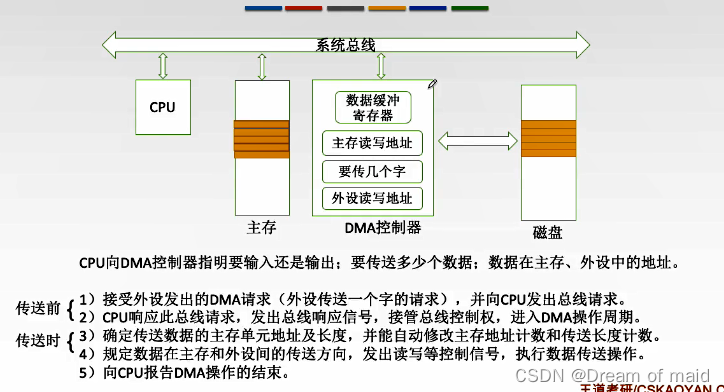

使用这种程序中断方式,每一次IO设备准备好一个字,CPU 就需要执行一次这个中断服务程序把这个字转存到主存中,CPU执行这个中断服务程序所需要的时间开销就非常大,DMA控制器通常用来控制快速设备的,以块为单位进行读写的设备,如磁盘,也就是一次读入许多字

下图单总线结构 DMA是否能访问主存是由CPU说了算的

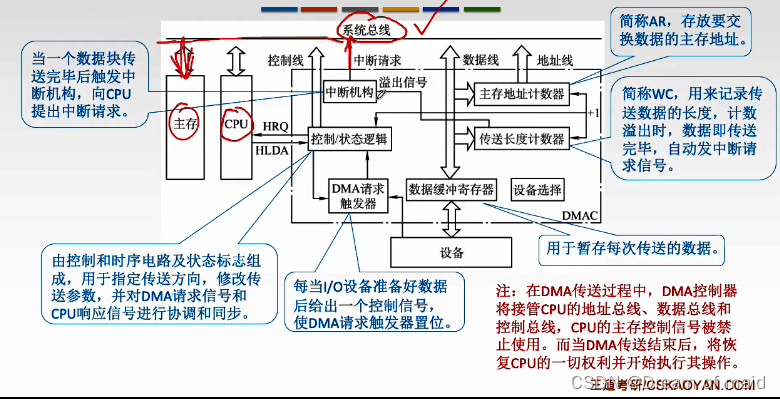

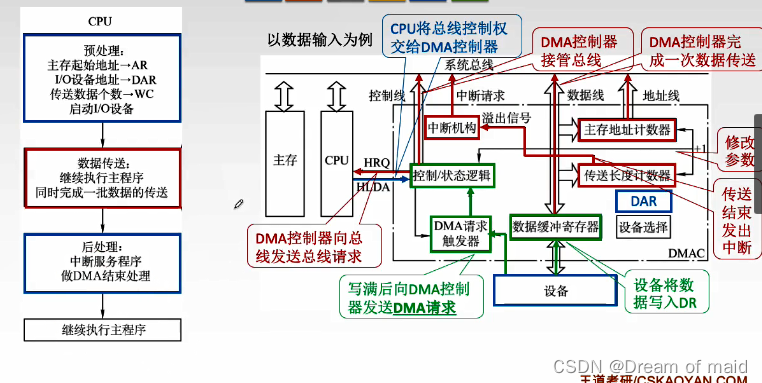

DMA内部结构细化

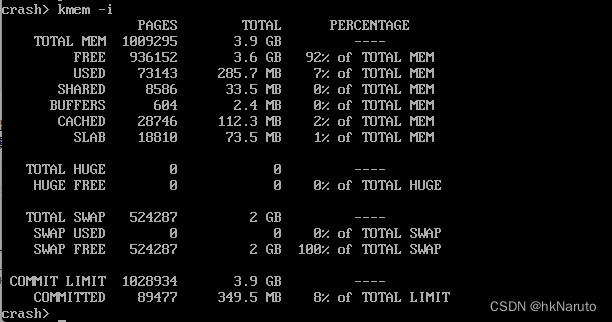

每传送完一个字,主存地址计数器以及传送长度计数器都会自动加一,中断机构与传送长度计数器之间是有一个溢出信号,意思是传送长度计数器所能表示的范围是有限的,当溢出的时候就会发出一个溢出信号,然后就会有中断请求

DMA 传送过程

预处理阶段DMA控制器指明接下来要读或者要写的内容应该存放在主存的什么位置,主存的读写寄存器(AR),还有一个用于指明设备的地址英文名叫做DAR,此外还需要指明多少个数据WC,接下来就有DMA控制器控制着数据传送的过程,对于CPU 它可以继续执行之前执行 的程序,如果此时我们要输入一个数据,设备首先要将数据写入DR这个寄存器中,同时向DMA触发器发出一个高电平型号让其变成1,当控制逻辑检测到DMA 请求,他就会向CPU申请总线的控制权(HRQ),如果系统总线可以让给DMA控制器使用的话,会给一个反馈信号(HLDA)DAM获得总线的控制器就可以通过数据线 地址线,控制线向主存发出读或者写的命令,同时把数据缓冲器DR中的数据打到数据线总线上,把主存的地址信息打到地址总线上,这样就完成了一个字的传输,然后让主存地址与传送长度计数器自动加一,传输多个字之后就会发生长度溢出,中断机构检测到之后就会发送一个中断请求,DMA在对中断型号进行处理,DMA请求与中断请求是不一样的,DMA请求表示要传送一个字 中断请求则表示一整块的数据传送已经完成了,

DMA方式的特点

三总线结构才会出现DMA 与cpu 同时访存的情况

DMA与CPU 都可以与主存进行数据的交互,但是应该是先满足主存还是先满足CPU,也就提出了用下列三种方式解决冲突

访存冲突

第三种若是CPU与DMA同时访存的时候,IO 设备优先,因为输入可能会覆盖

DMA方式与中断方式

本节回顾