板级电源分配网络的分析与仿真

在硬件电路设计中,电源系统的设计是关键步骤之一,良好的电源系统为电路板

上各种信号的传输提供了保障。本章将研究电源完整性的相关问题,并提出一系列改

进电源质量的措施。

3.1

电源完整性

电源完整性(

Power Integrity

)简称为

PI

,是指电源分配网络(

Power Distribution

Network

,

PDN

)能够满足负载芯片对电源的需求。其设计目标主要有两个:一是为

负载提供干净的供电电压,二是为信号提供低噪声的参考路径

[21]

。

随着芯片开关速度和晶体管数量的不断提高,芯片的功耗不断增加,开关在切换

时所需的瞬态电流需求越来越大,这些变化给电源分配网络的设计提出了巨大的挑战。

电源分配网络主要由如下几部分组成:电源芯片、安装在

PCB

板上的电容以及芯片

内部的电容和电源网络。本文主要针对安装在

PCB

板上的电容、电源和地平面进行

分析。

3.1.1

电源噪声的来源

电源噪声的来源主要包括三个方面:

(

1

)电源芯片输出存在纹波。这部分噪声由芯片的制作工艺以及工作原理等决

定,当选择好电源芯片时,相应的输出噪声就会存在。常用的电源芯片有开关电源和

线性电源两种。开关电源的优点是发热少,转换效率高,一般可以达到

85%

,输出电

流大,缺点是输出的波动较大,且可能会有尖峰脉冲,需要在输出端添加磁珠来改善。

而线性电源的发热较为明显,转换效率较低,但是线性电源的输出稳定,纹波较小。

要根据供电要求灵活选用。

(2)稳压电源无法及时响应快速变化的负载电流需求。随着芯片工作频率的不

断提高,芯片需要的电流变化的频率也越来越高,当该频率超过稳压电源的调整频

率时,稳压电源就无法及时为负载提供足够的电流,进而导致输出电压下降,产生

电源噪声。

(3)电源路径和地路径上存在压降

[22]

。由于电源路径和地路径存在阻抗,当电

流流过这些路径时,就会产生压降,因此负载电压就会随着电流的变化而产生波动。

同时过孔、封装引脚和芯片内部的电源网络也存在阻抗,都会产生压降。

3.1.2

建立仿真模型

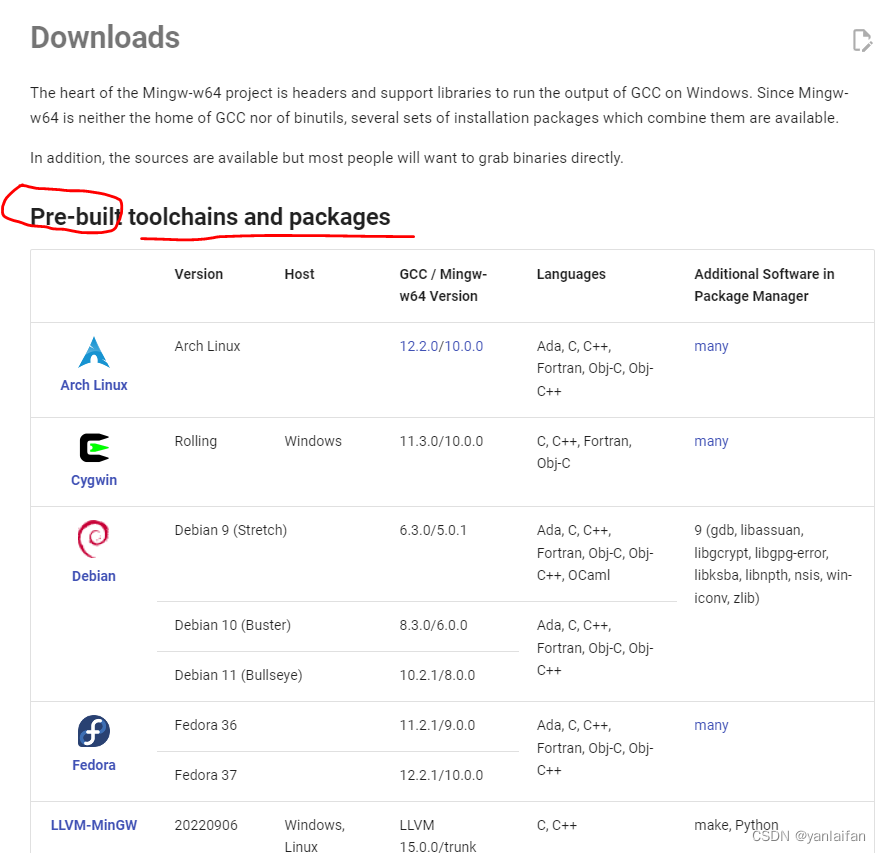

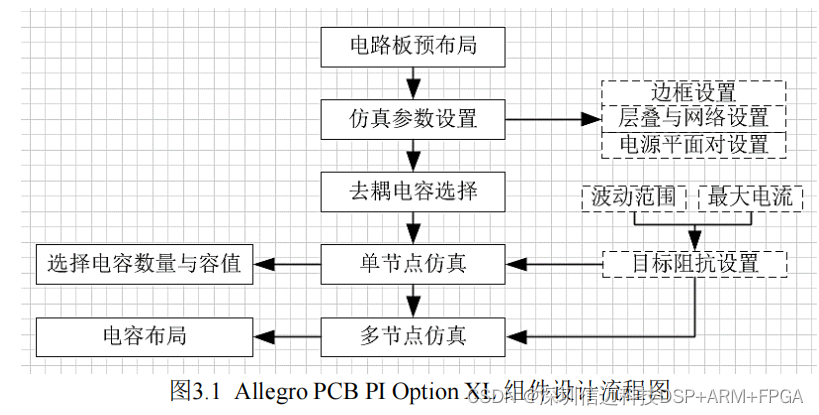

仿真软件选择

Cadence

公司的

Allegro PCB PI Option XL

组件,该组件可进行电

源噪声分析和高速

PCB

电源分配系统的设计,其仿真功能主要分为单节点仿真和多

节点仿真两种

[23]

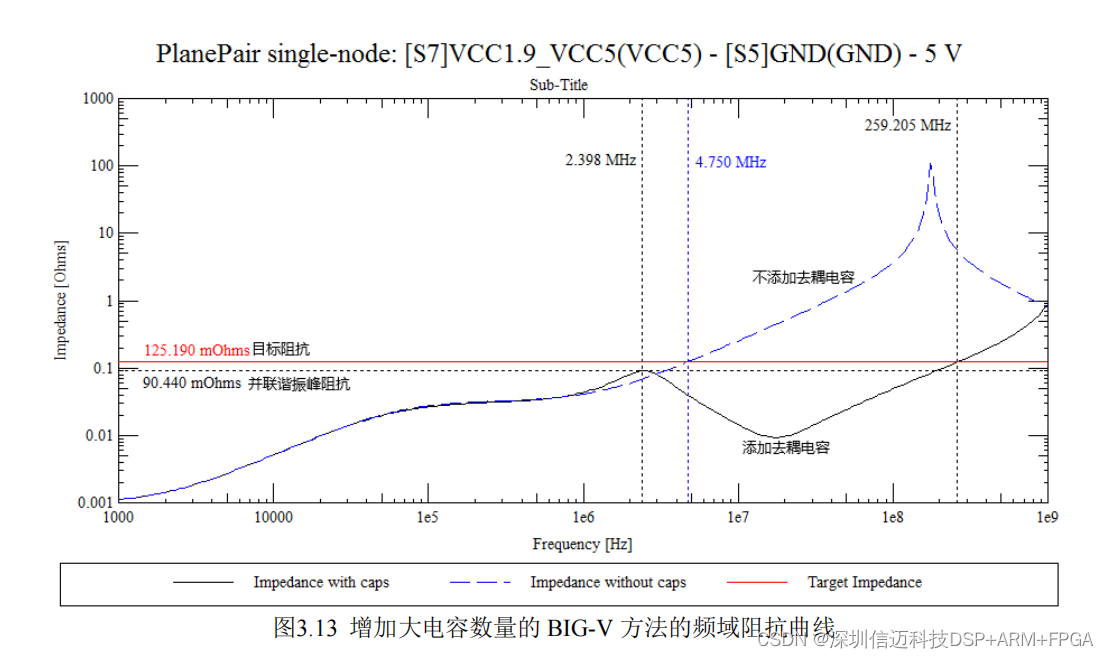

。单节点仿真仅考虑电容的去耦能力和目标阻抗之间的关系,通过该

仿真可以对比不同去耦电容网络的去耦能力的差别,方便用户选择合适的去耦电容网

络。多节点仿真则会考虑噪声源信号、电容的滤波半径和电容的布局等参数,该仿真

结果更接近真实的情况,通过多节点仿真可以完成去耦电容的布局工作。仿真软件的

基本使用流程如图

3.1

所示。

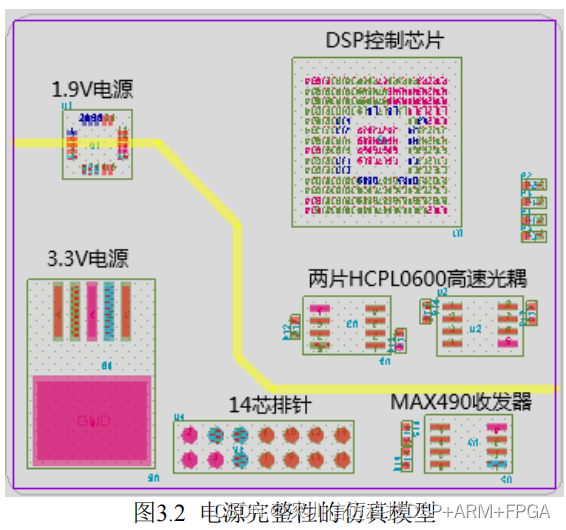

由于本章的主要内容在于电源完整性相关问题的分析与仿真,故电路模型的设计

重点放在电源分配网络的建立上,不考虑其余的外围电路。按照上述设计流程建立如

图

3.2

所示的预布局仿真模型。

如图

3.2

所示,该仿真模型的尺寸为

55*47.5mm

,具体电路包括:

DSP

控制芯片

TMS320F28335

、

1.9V

电源芯片

TPS74401

、

3.3V

电源芯片

TPS75633

以及由收发器

MAX490

和光电隔离芯片

HCPL0600

构成的上位通信接口电路;

14

芯排针则作为接

插件,引入该模型所需要的

5V

电源。电路的工作频率取

DSP

的工作频率

150MHz

。

需要说明的是,在进行电源完整性仿真时,

DSP

芯片和上位通信接口电路仅起噪声源

的作用,不考虑其实际的电路功能。

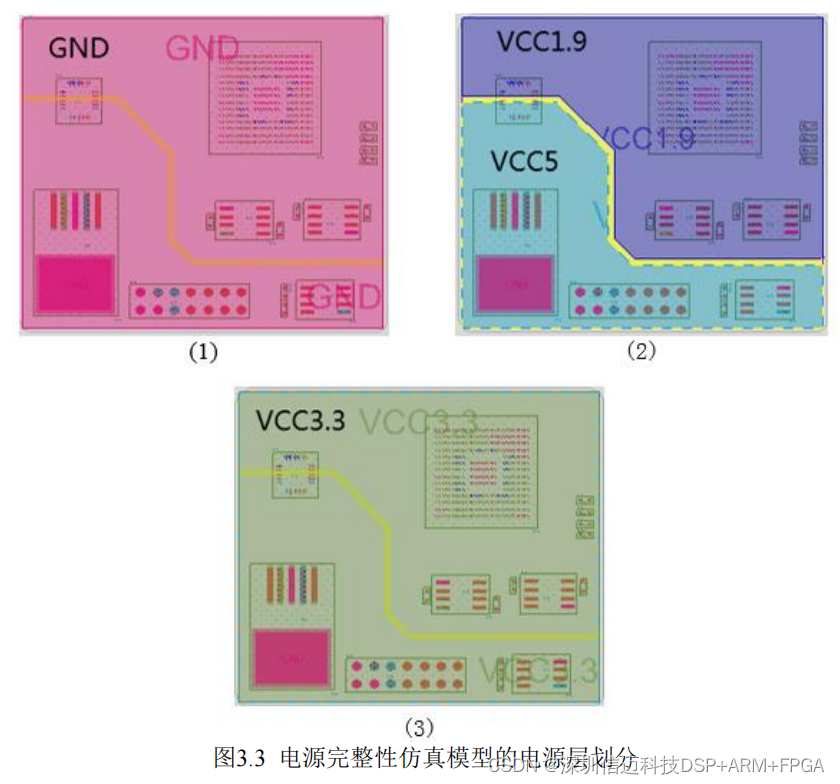

在完成预布局的基础上对仿真模型进行电源层划分,该模型所用到的电源有:

1.9V

、

3.3V

、

5V

和

GND

。划分好的电源平面如图

3.3

所示。

如图

3.3

所示,该模型的电源层一共划分为

3

层:第(

1

)层为完整的地平面;

第 (2)层则进行分割,划分为 1.9V

电源平面和

5V

电源平面;

第(3)层为完整的

3.3V

电源平面。各个电源层之间的间距设置为

8mil

。

3.2

去耦电容

为了使电源芯片的输出能够快速响应负载芯片的需求,主要采用的方法是在电源

芯片的输入输出引脚和负载芯片的供电引脚周围放置去耦电容

[24]。本节将重点分析

电容的去耦原理和频域阻抗特性,并通过仿真提出改善电容去耦能力的措施。

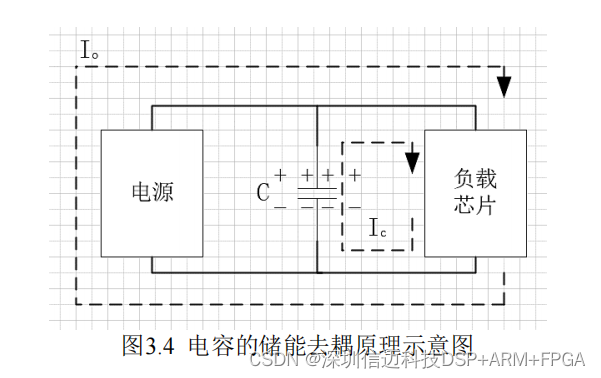

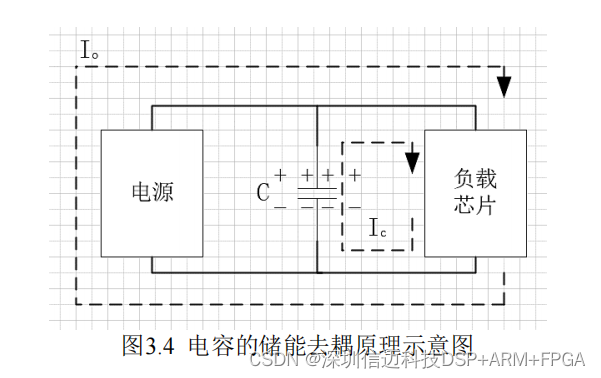

3.2.1

电容去耦原理

电容去耦的原理可以从储能和阻抗两个角度进行理解。

(

1

)储能去耦原理

图

3.4

给出了电容的储能去耦原理,

C

为电源芯片外放置的去耦电容组合。当负

载电流保持不变时,电源电压和电容两端的电压也不变,且与负载芯片两端的电压一

致,此时流过电容的电流为零,负载所需的电流由电源提供。当负载芯片的电流快速

变化时,需要电源能够立即提供给负载芯片所需的电流,但是电源往往不能及时响应

负载电流的变化,这就会导致负载芯片的电压产生变化。此时电容两端的电压也会随

着负载电压的变化而变化,电容就会进行充放电并产生电流

为负载芯片提供电流,

从而保证负载芯片的电压不会产生明显的变化

[25]

。

从储能的角度来理解去耦电容的作用比较直观,但是对于电路设计却没有多大的

帮助,因此需要从阻抗的角度理解电容的去耦原理。

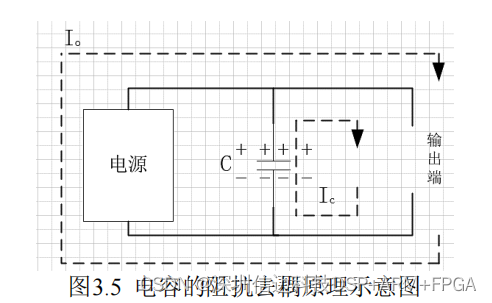

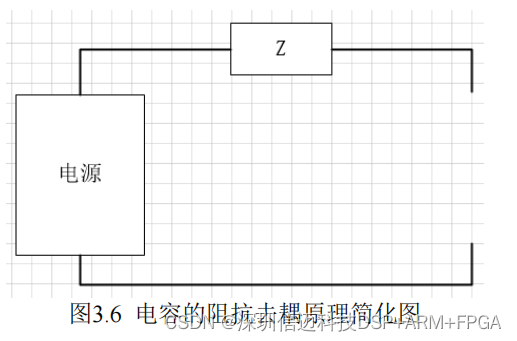

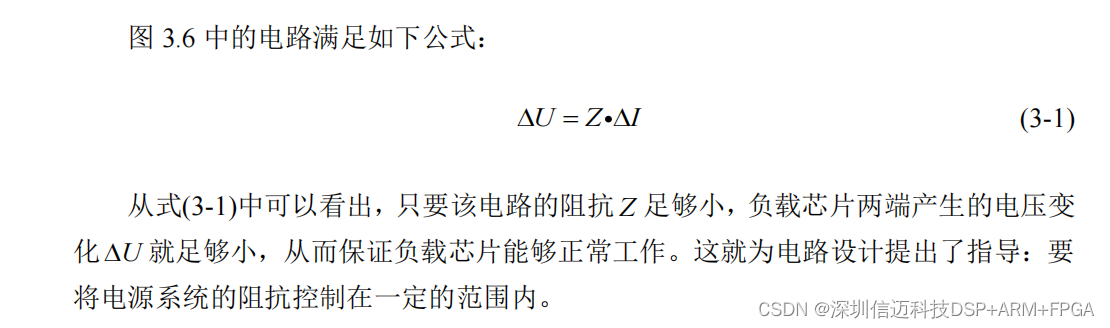

(2)阻抗去耦原理

将图

3.4

中的负载芯片去掉,可以得到如图

3.5

所示的模型。从该模型的输出端

看进去,将电源与电容组合

C

当做一个整体的电源系统,即可以简化为图

3.6

所示的

电路。

然后在仿真模型内添加电压调节模块(

VRM

)和噪声源,由于

1.9V

电源仅为

DSP

的内核电源引脚供电,因此在

DSP

的位置添加噪声源,并设置噪声电流的最大幅度

为

0.5A

。为了对比不同布局情况下的去耦效果,将分两种方式对去耦电容进行布局。

首先采用第一种方式进行布局,即将小电容均匀放置在最靠近

DSP

芯片的位置,

而大电容则适当远离

DSP

芯片放置,这种电容布局方式如图

3.17

所示。同时可以看

到,组件会自动在模型中设置多个仿真节点,这里选择位于

DSP

下方的四个仿真节

点进行仿真。多节点仿真结果如图

3.18

所示。

3.3

提升电源质量的措施

通过分析电容的实际特性、并联特性和安装后的特性,对比不同的电容网络选择

方法的去耦效果,可以得出一系列能够改善电源分配网络去耦效果的方法。在电路板

的设计过程中,具体可以采取以下方法来改善电路的电源完整性:

(

1

)要合理选择电源芯片,兼顾转换效率与输出纹波。同时针对不同的场景灵

活选用线性电源和开关电源,比如给对电源比较敏感的模拟电路供电时,可以选择输

出噪声低的线性电源。

(2)去耦电容网络的选择尽量采用

Multi-Pole

(

MP

)方法,选择多种电容值的

电容搭配使用,避免使用容值差较大的去耦电容网络,为了兼顾成本与去耦效果,可

以使用

One per decade

方法来选择去耦电容。

(3)摆放电容时要考虑其去耦半径的大小,小电容要靠近芯片,而大电容可以

摆放的远一些。同时去耦电容要均布在芯片四周,不同电压的去耦电容要交替摆放。

(4)安装电容时,减小电容走线的长度,同时要加宽走线的宽度。这样可以保

证其电流回路面积较小,减少了安装电感对电容去耦效果的影响。

(5)电源平面和地平面的层叠设置要合理,尽量使电源平面与其对应的地平面

相邻。分割电源平面时尽量保证形状规则,使平面的阻抗均匀。

信迈提供高速信号仿真方案。