计组:2.4

- 算术逻辑单元

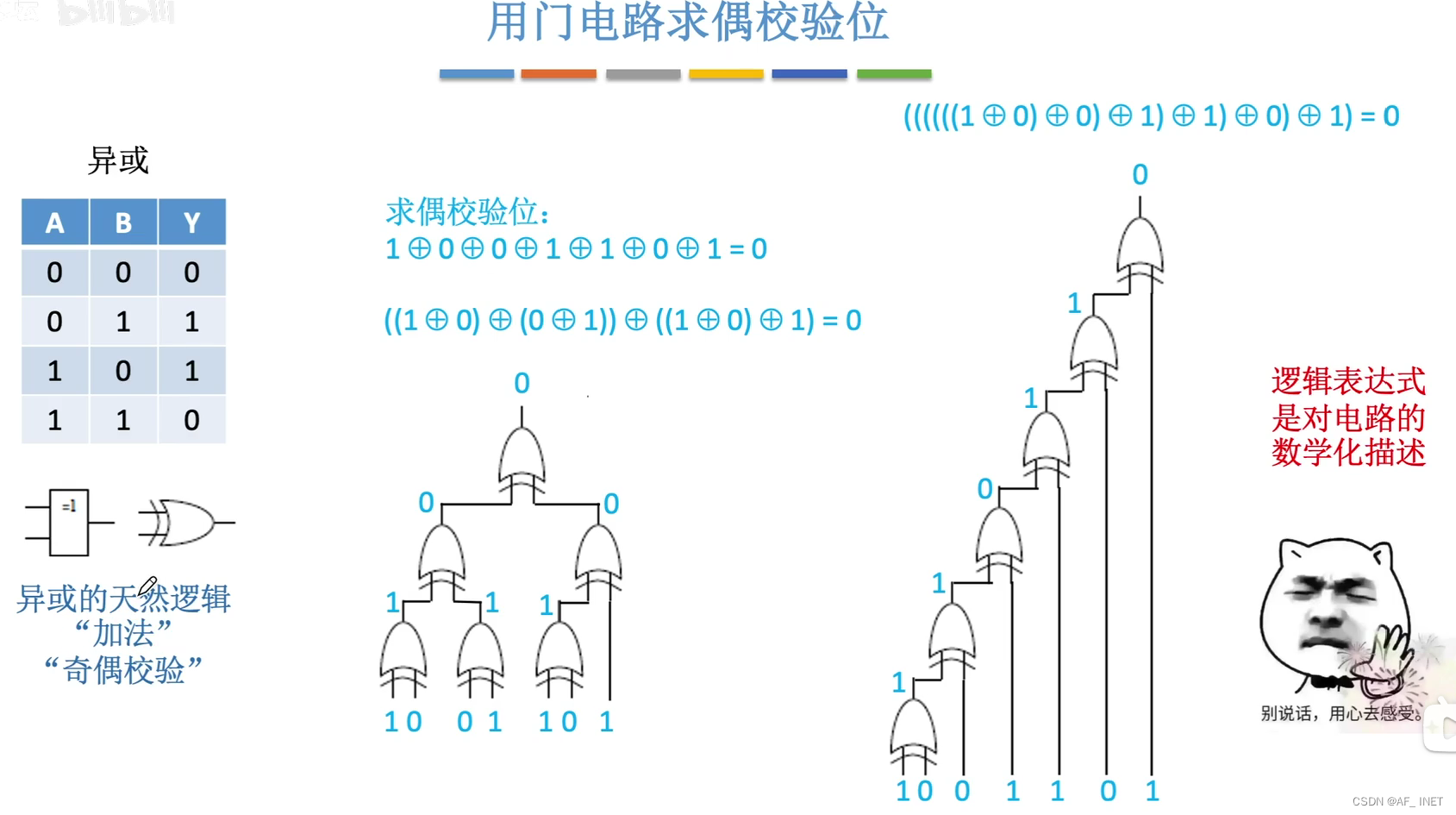

- 异或门实现奇偶校验的原理

- 串行加法器&&并行加法器

- 并行加法器的优化

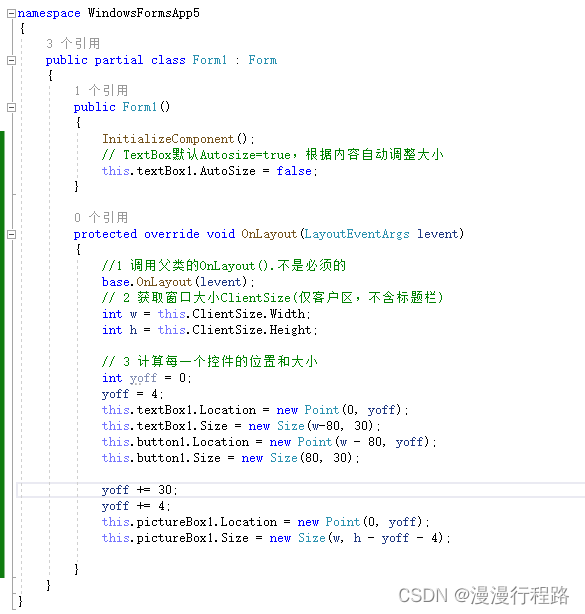

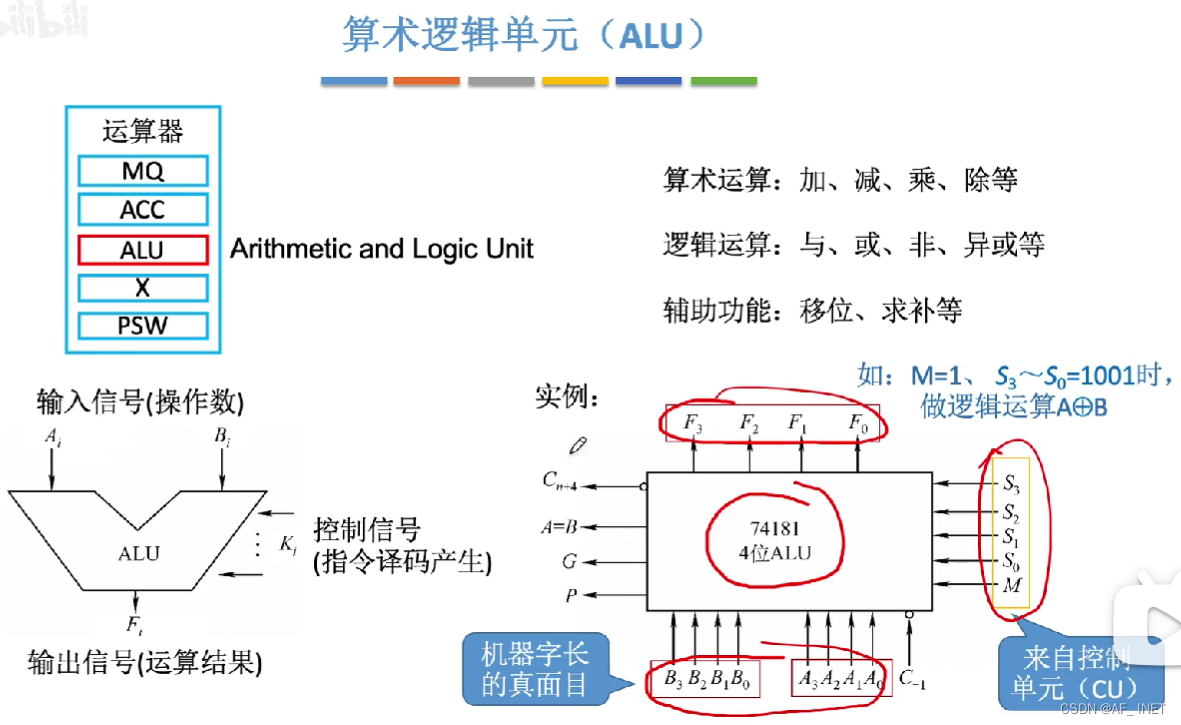

算术逻辑单元

控制信号:

当M=0时表示算术运算

当M=1时表示逻辑运算

S0~ S3表示做什么运算,因此ALU可以表示16种算数运算和16种逻辑运算

Ai,Bi代表输入两个4bit的数据,得到4bit的输出,机器字长代表计算机可以同时处理多少字长的bit运算,机器字长代表算术逻辑单元可以同时输入多少bit的信息,基本上寄存器的位数和ALU保持一致,也就是机器字长

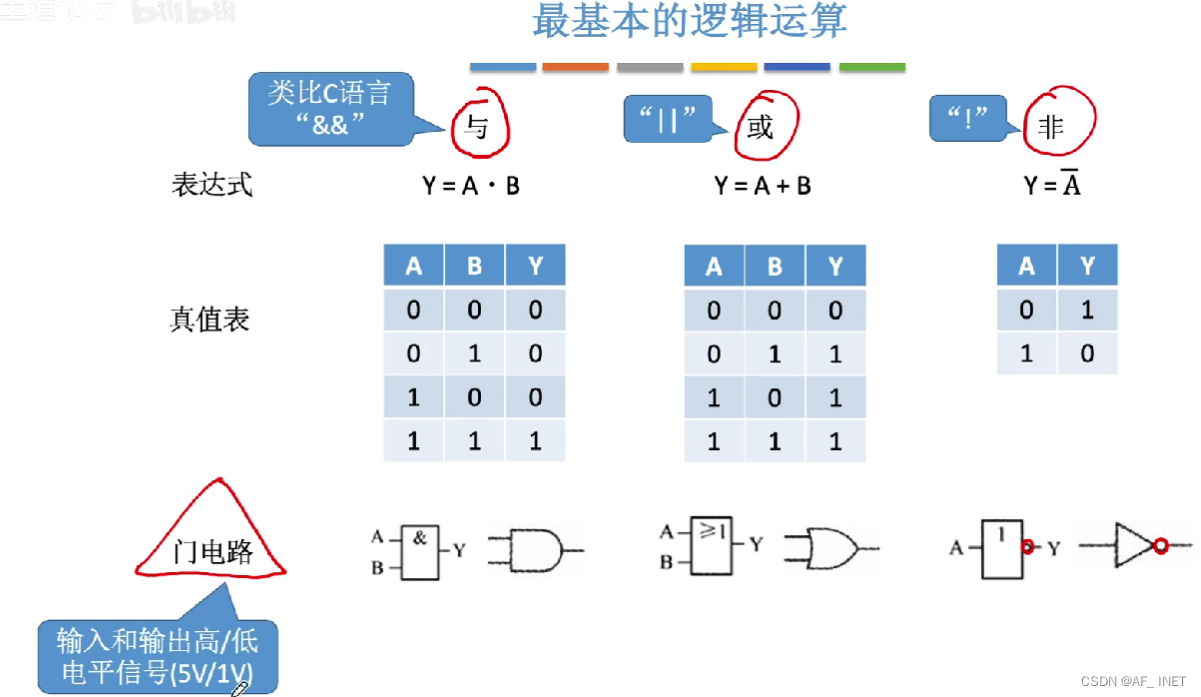

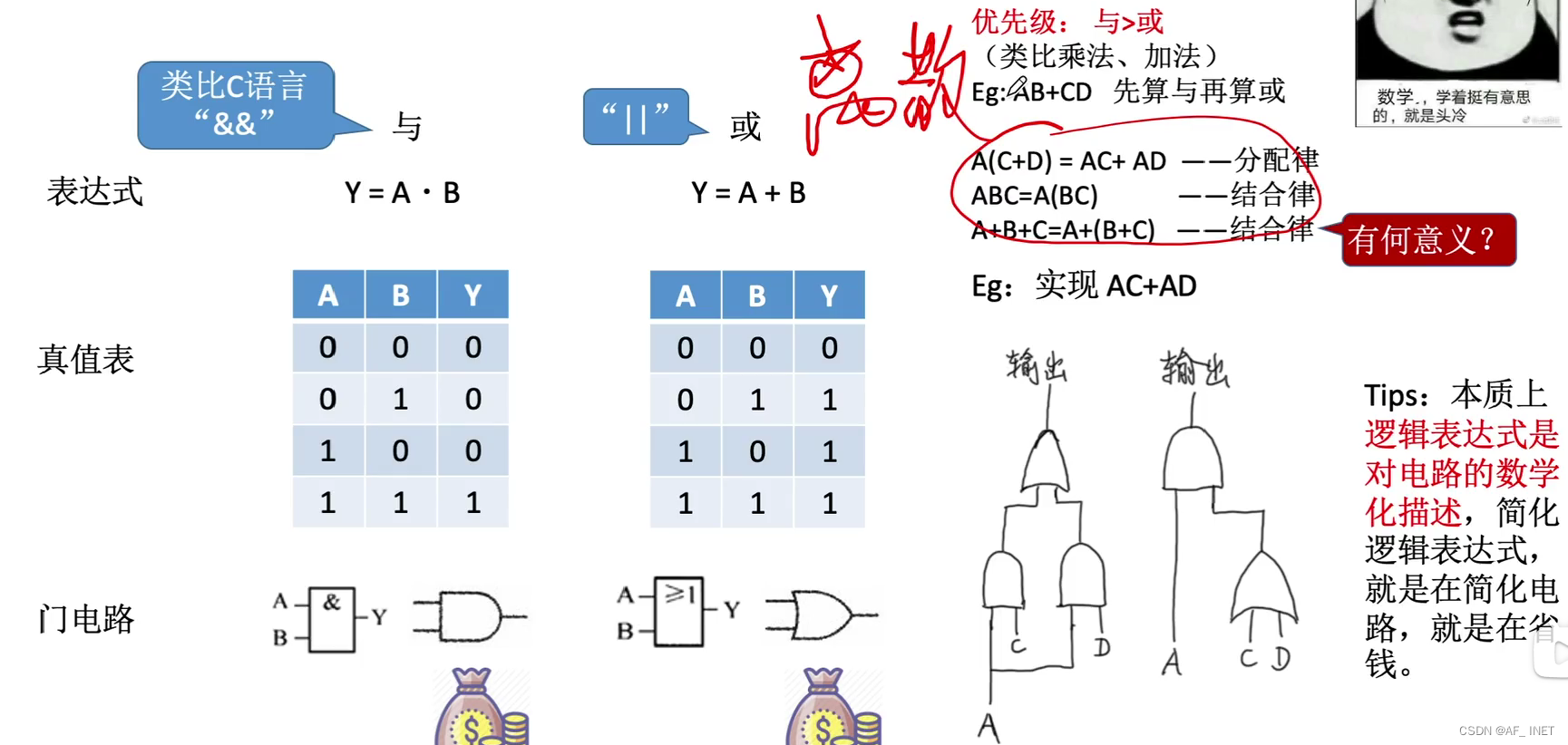

异或门实现奇偶校验的原理

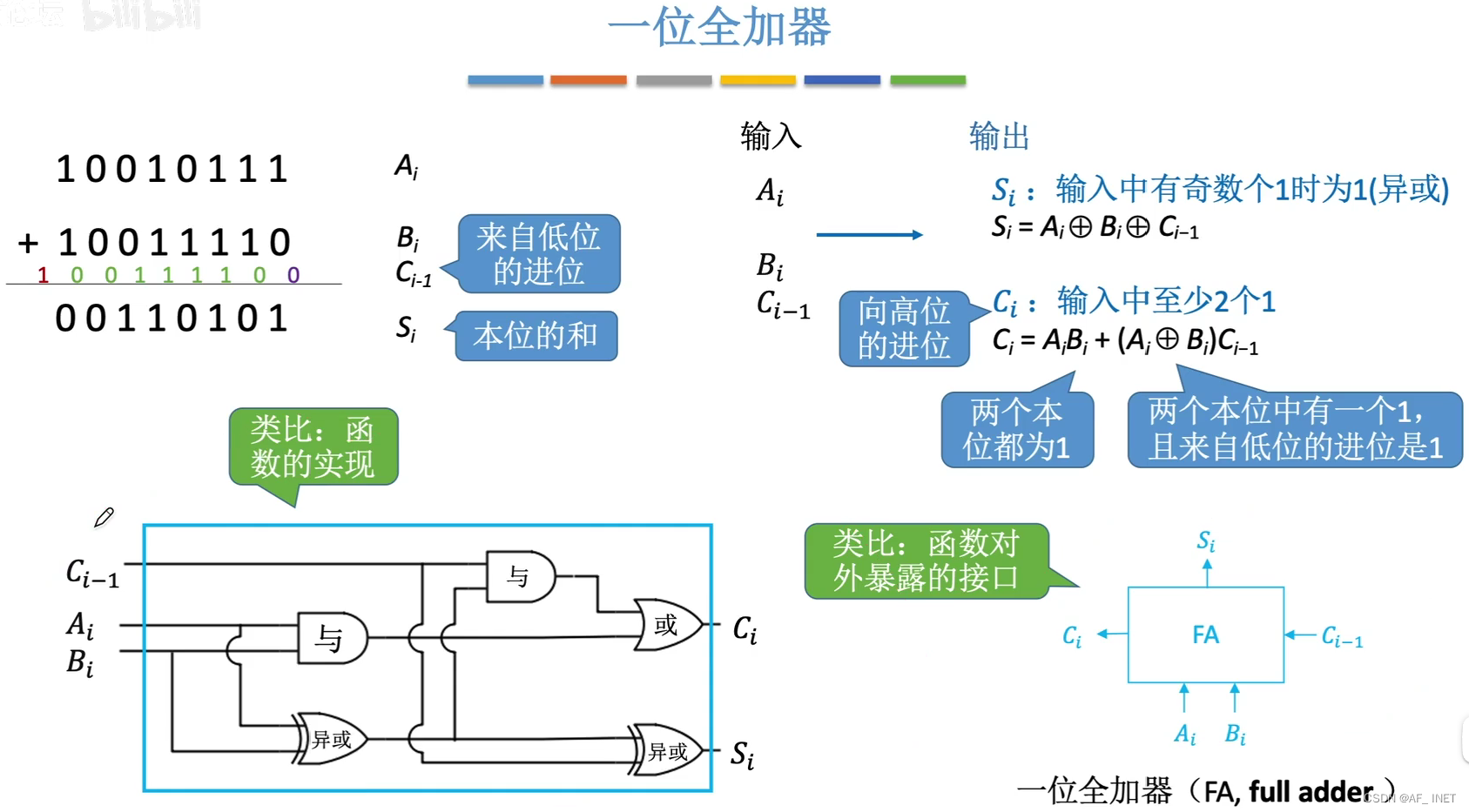

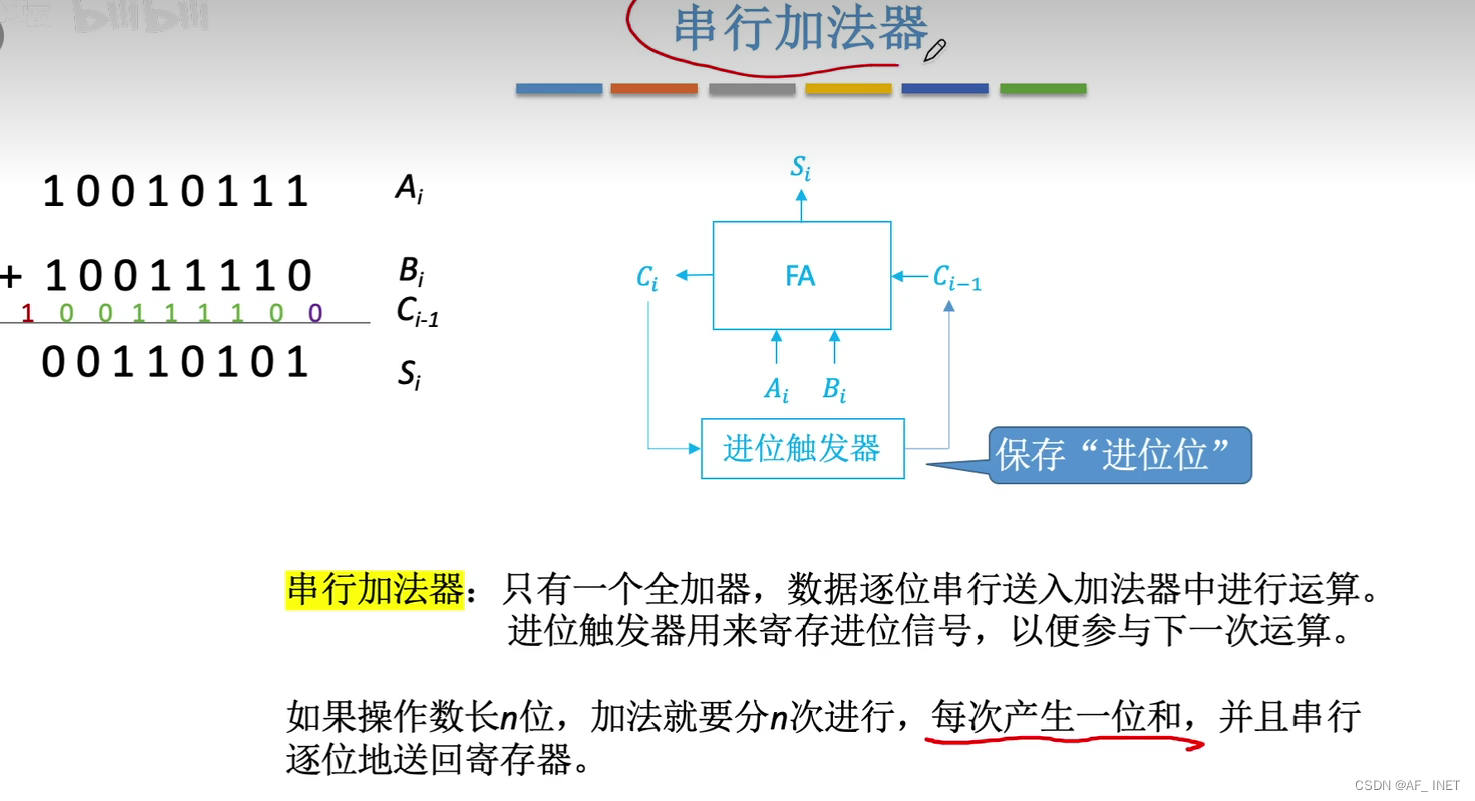

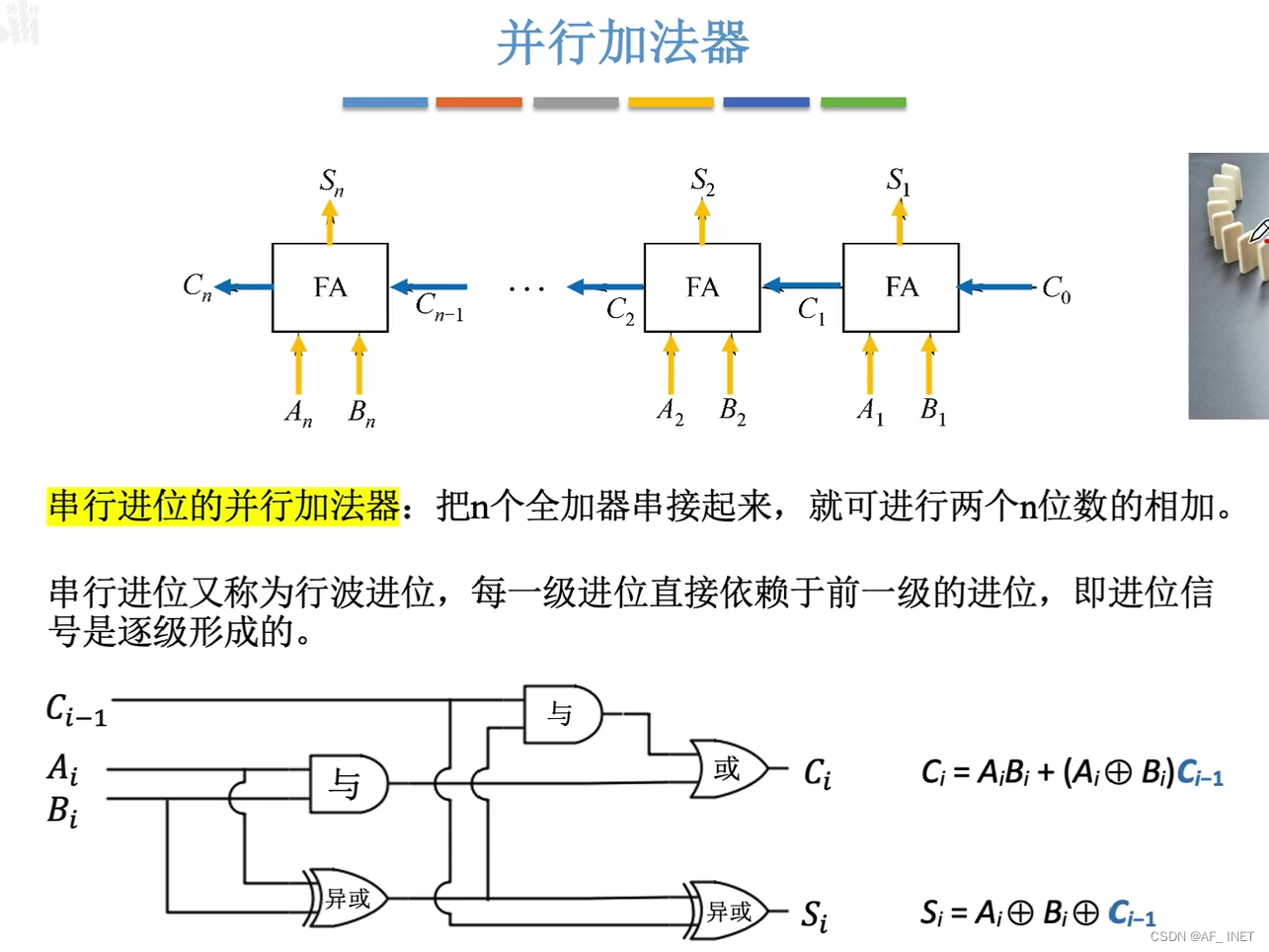

串行加法器&&并行加法器

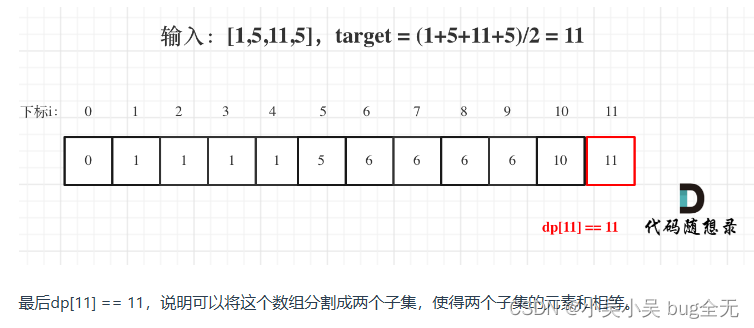

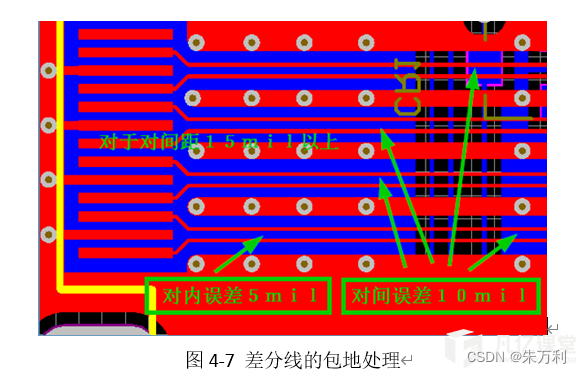

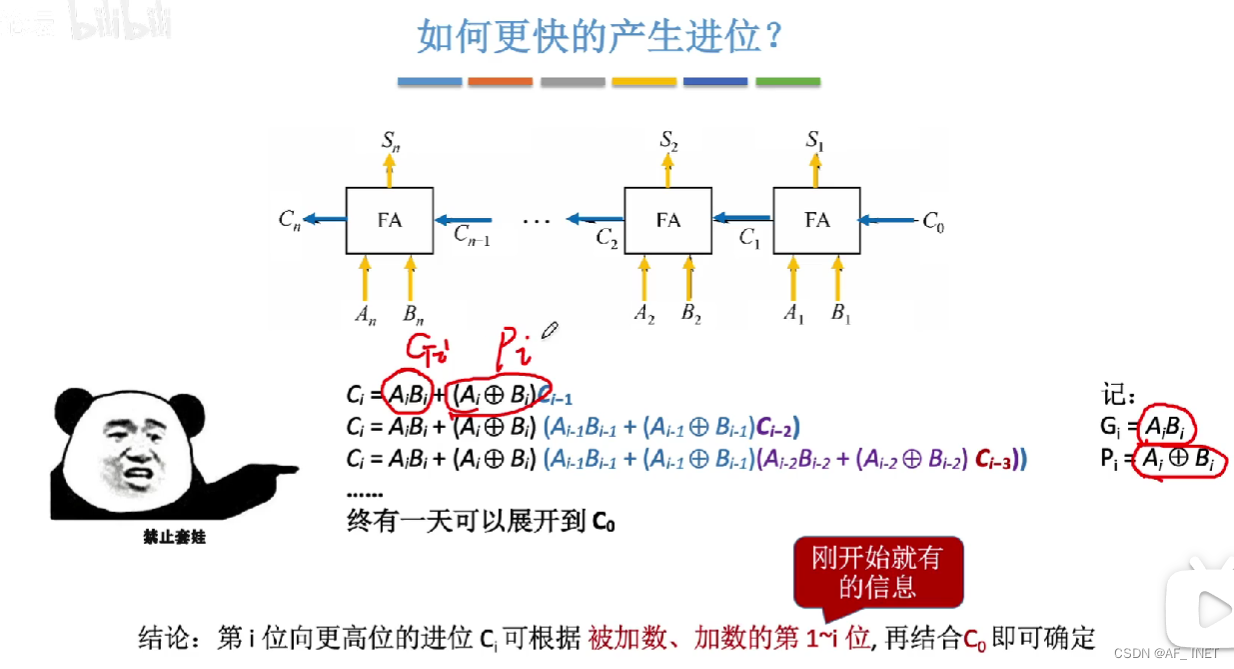

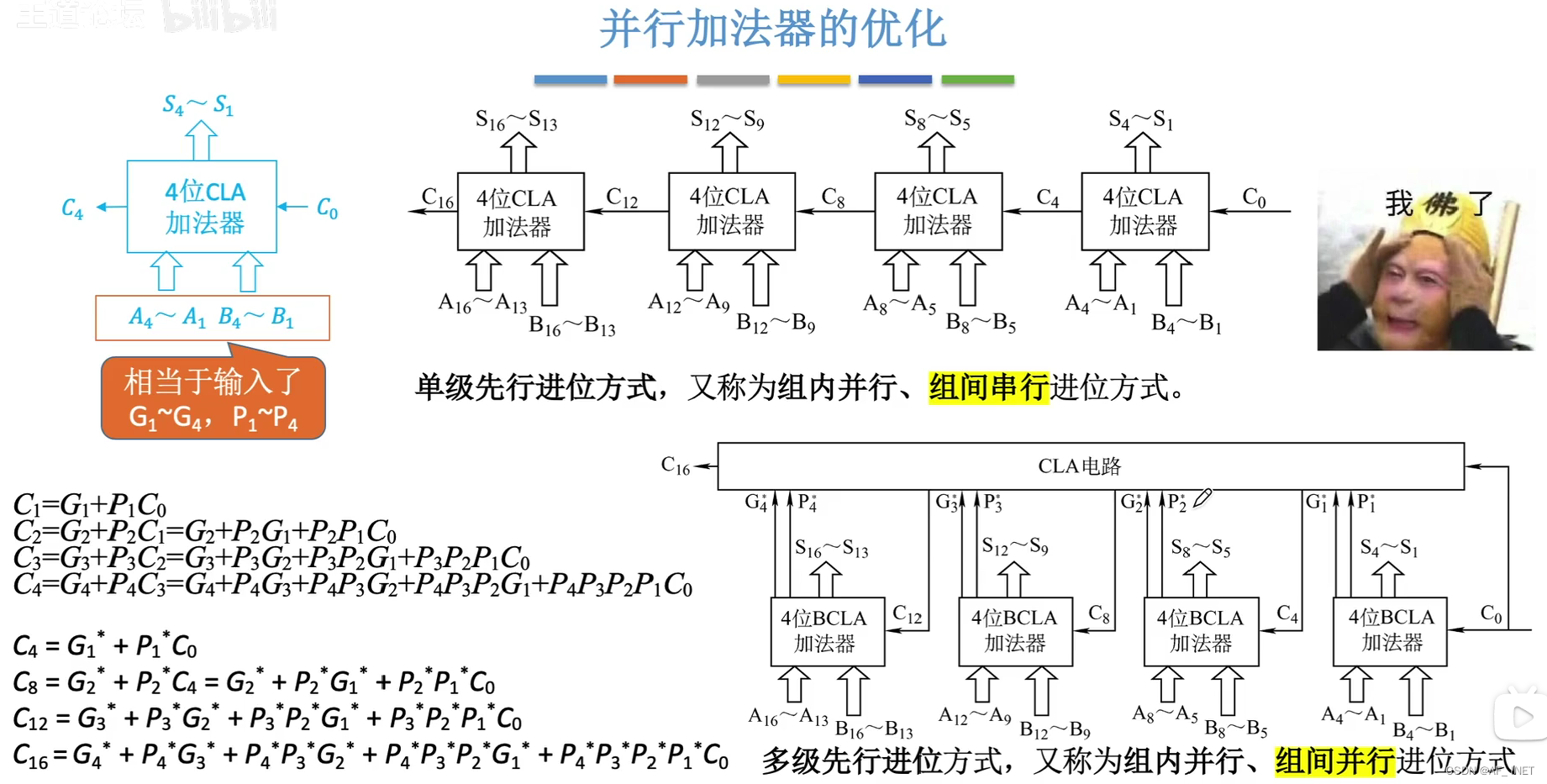

并行加法器的优化

- 设计电路使每一位的进位几乎同时产生

- Gi为进位产生函数,如果Ai和Bi都是1,则会产生进位

- Pi的值影响到来自低位的值是否会往上传递

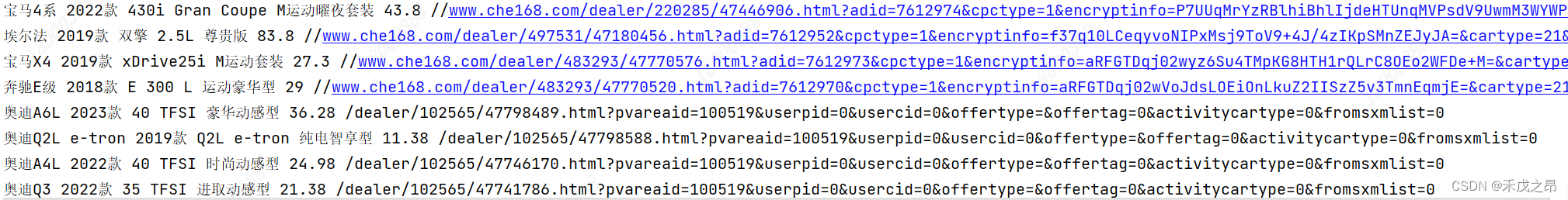

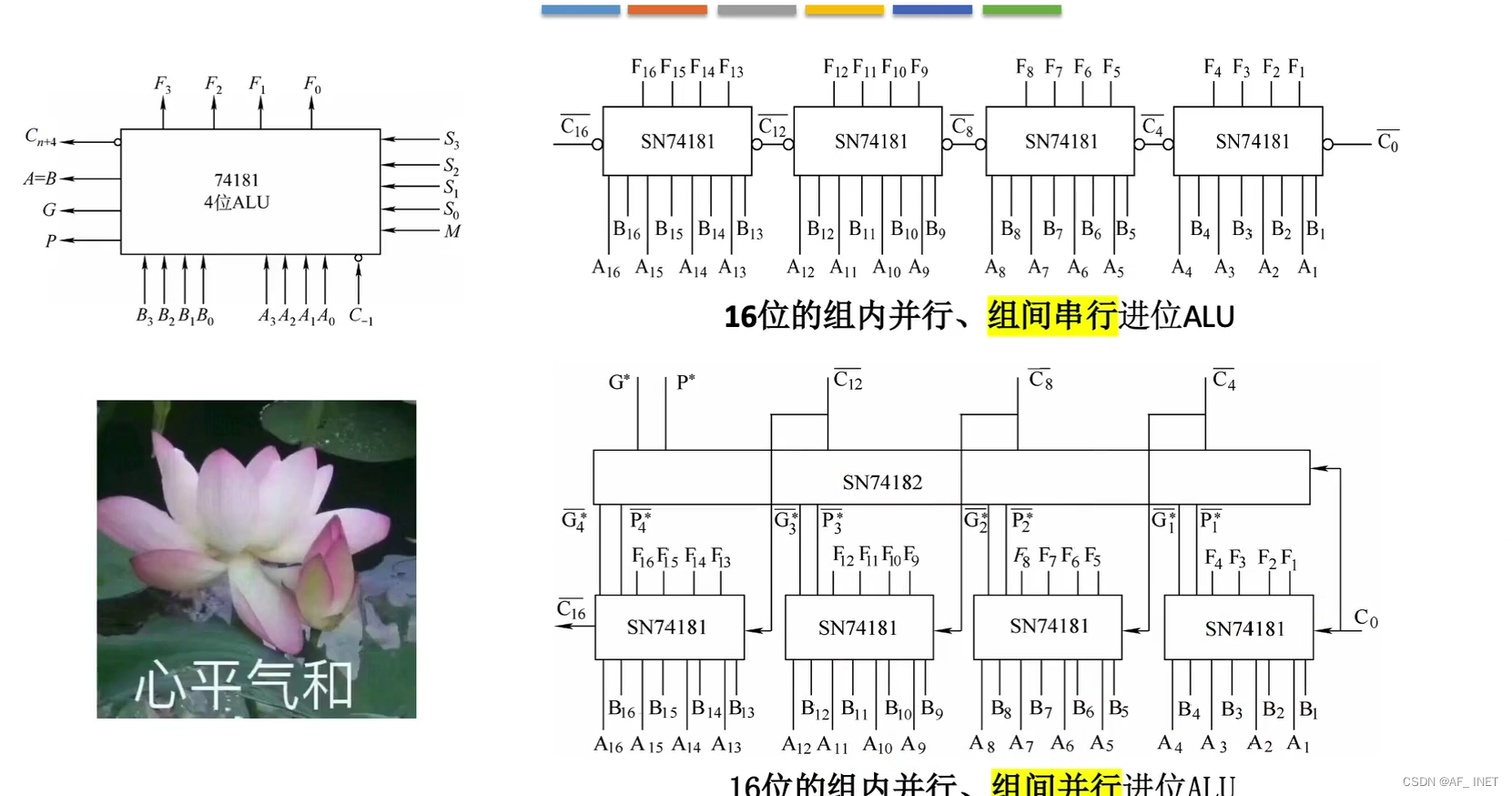

如果只用一个74L181芯片,那么此时机器字长只有四位,只能同时进行4位整数运算,把多个74181串联,得到机器字长为16位的ALU

串行加法器——>串行进位的并行加法器——>

组内并行、组间串行进位的加法器——>组内并行、组间并行进位的加法器