逻辑代数L是一个封闭的代数系统,由一个逻辑变量集K,常量0和1,以及与或非三种基本运算构成。

参与逻辑运算的变量叫逻辑变量,用字母A,B……表示。每个变量的取值非0 即1。 0、1不表示数的大小,而是代表两种不同的逻辑状态。

正、负逻辑规定:

- 正逻辑体制规定:高电平为逻辑1,低电平为逻辑0。

- 负逻辑体制规定:低电平为逻辑1,高电平为逻辑0。

真值表是把逻辑变量的所有取值及其对应的结果构成的一个二维表格。

与、或、非

逻辑符号表:https://zh.wikipedia.org/zh/%E9%80%BB%E8%BE%91%E7%AC%A6%E5%8F%B7%E8%A1%A8

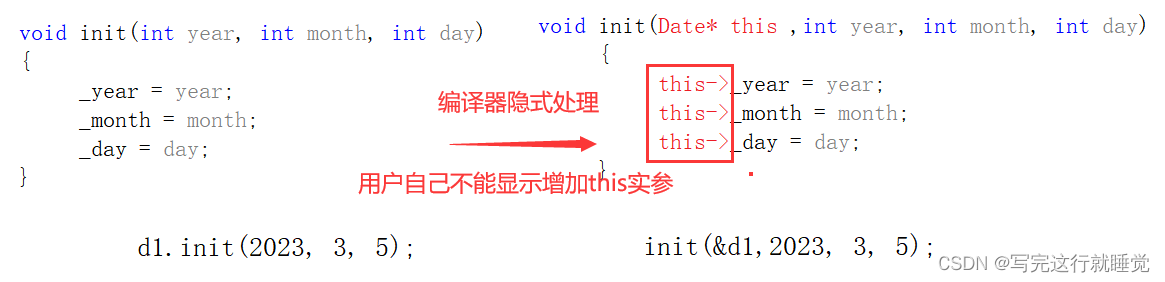

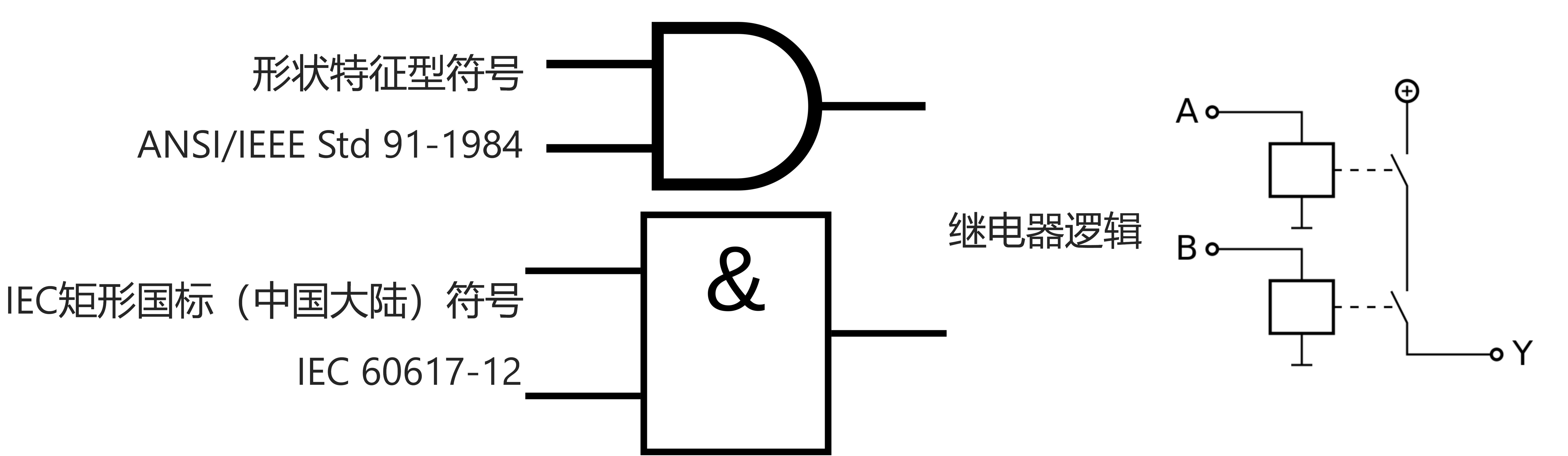

与:逻辑合取

如果A与B二者都为真,则陈述A∧B为真;否则为假。

符号:∧、•、&

维基百科:https://zh.wikipedia.org/wiki/%E4%B8%8E%E9%97%A8

或:逻辑析取

如果A或B之一为真陈述或AB两者都为真陈述,则A∨B为真;如果二者都为假,则陈述为假。

符号:∨、+、ǀ

维基百科:https://zh.wikipedia.org/wiki/%E6%88%96%E9%97%A8

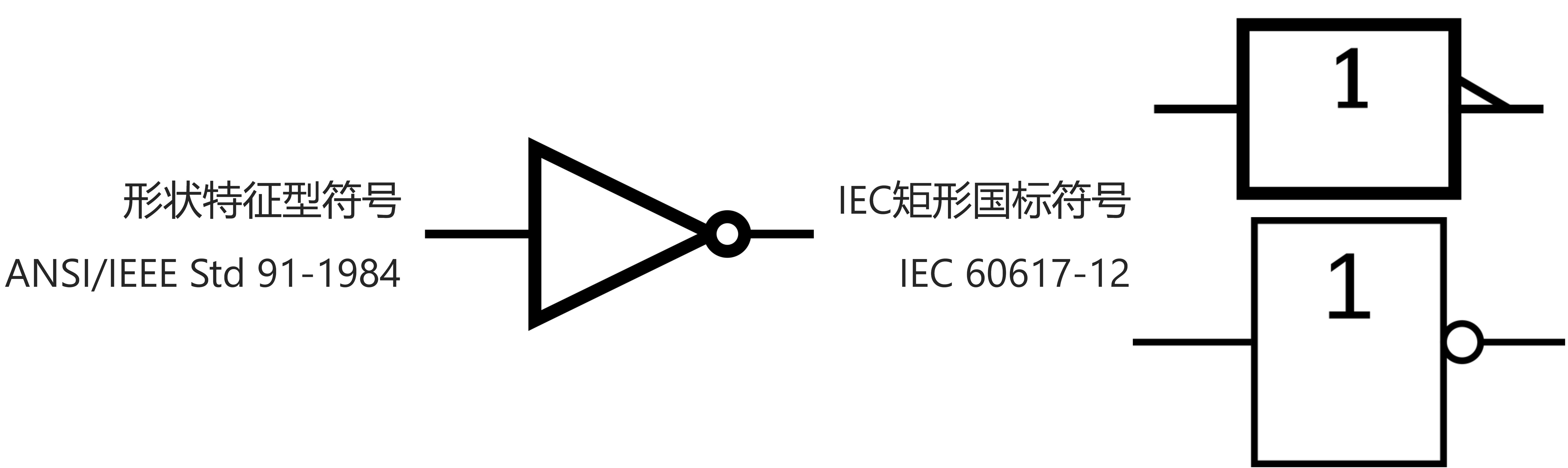

非:逻辑否定

又名:反相器

陈述¬A为真,当且仅当A为假。穿过其他算符的斜线同于在它前面放置的 “¬”。

符号:¬、˜

维基百科:https://zh.wikipedia.org/wiki/%E5%8F%8D%E7%9B%B8%E5%99%A8

与非、或非、异或、同或

与非:输入都为1时,输出为0

或非:输入都为0时,输出为1

异或:输入不相同时,输出为1

同或:输入相同时,输出为1

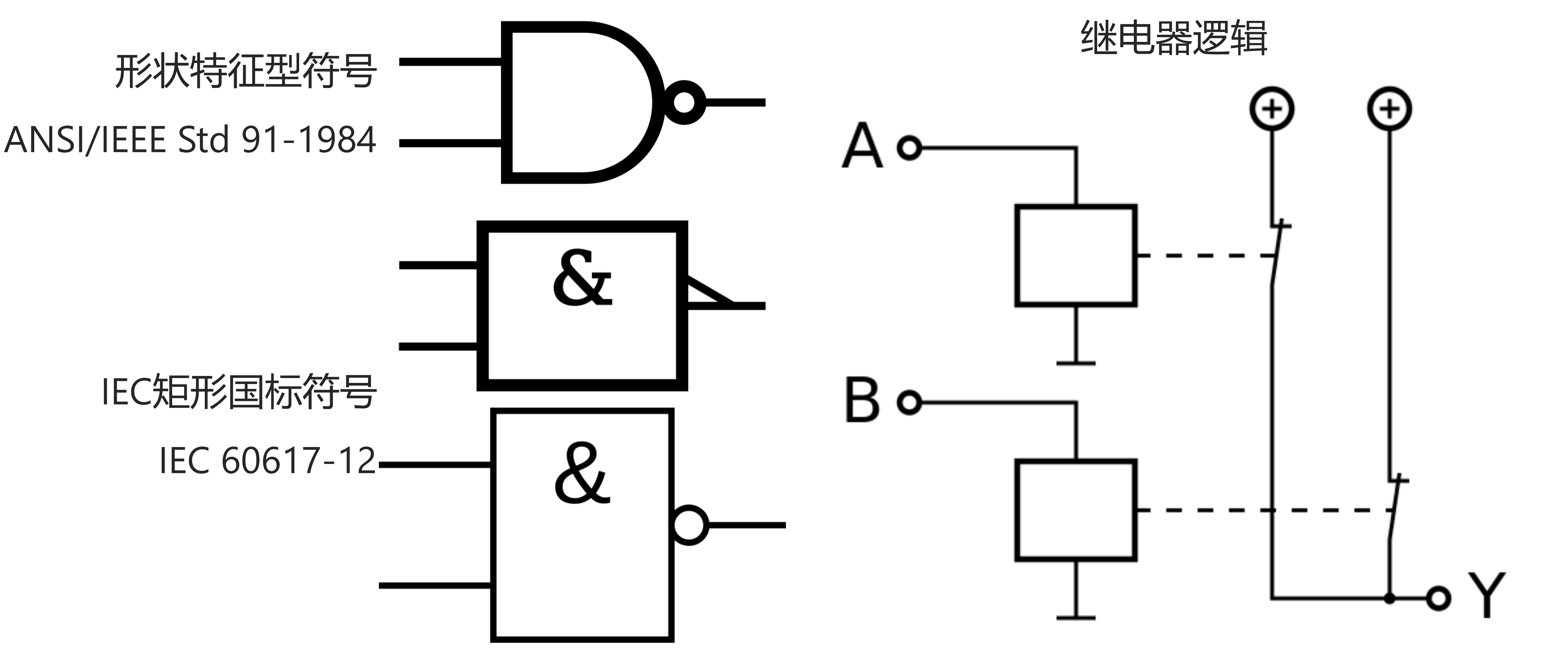

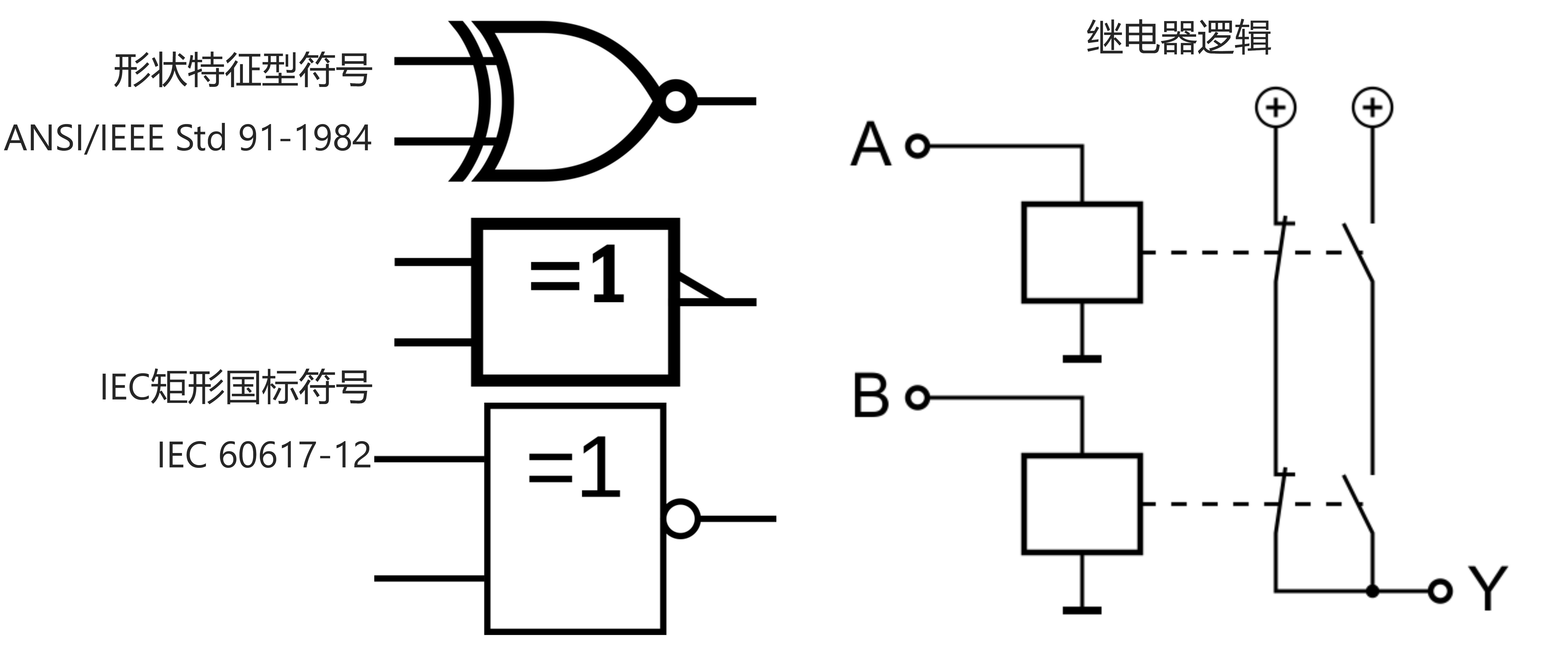

与非NAND

与非门(英语:NAND gate)是数字逻辑中实现逻辑与非的逻辑门。若输入均为高电平(1),则输出为低电平(0);若输入中至少有一个为低电平(0),则输出为高电平(1)。与非门是一种通用的逻辑门,因为任何布尔函数都能用与非门实现。

真值表:

只有在A和B都为1时,结果才为1。

| 输入A | 输入B | 输出A NAND B |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

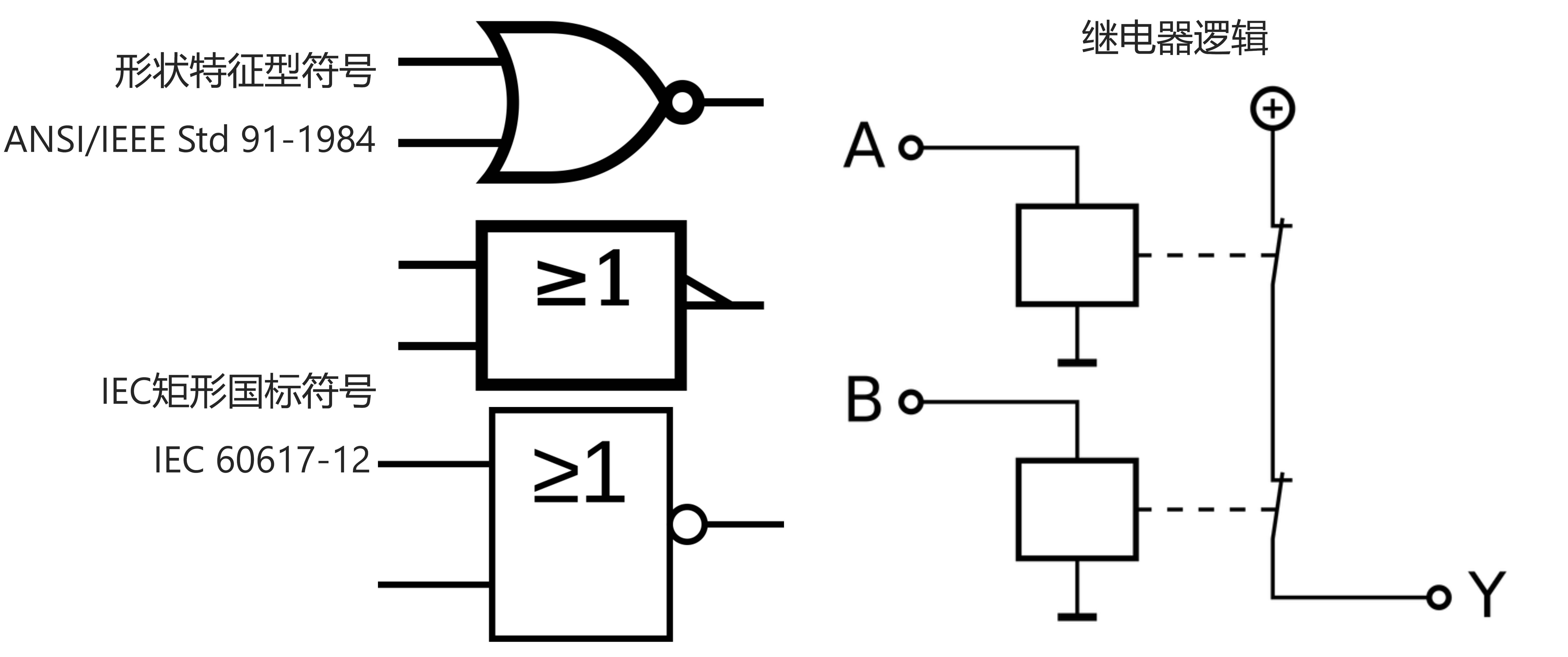

或非NOR

或非门(英语:NOR gate)是数字逻辑中实现逻辑或非的逻辑门,功能见右侧真值表。若输入均为低电平(0),则输出为高电平(1);若输入中至少有一个为高电平(1),则输出为低电平(0)。或非是逻辑或加逻辑非得到的结果。或非是一种具有函数完备性的运算,因此其他任何逻辑函数都能用或非门实现。相比之下,逻辑或运算器是一种单调的运算器,其只能将低电平变为高电平,但不能将高电平变为低电平。

真值表:

| A | B | Y=A+B | Y=A NOR B |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 |

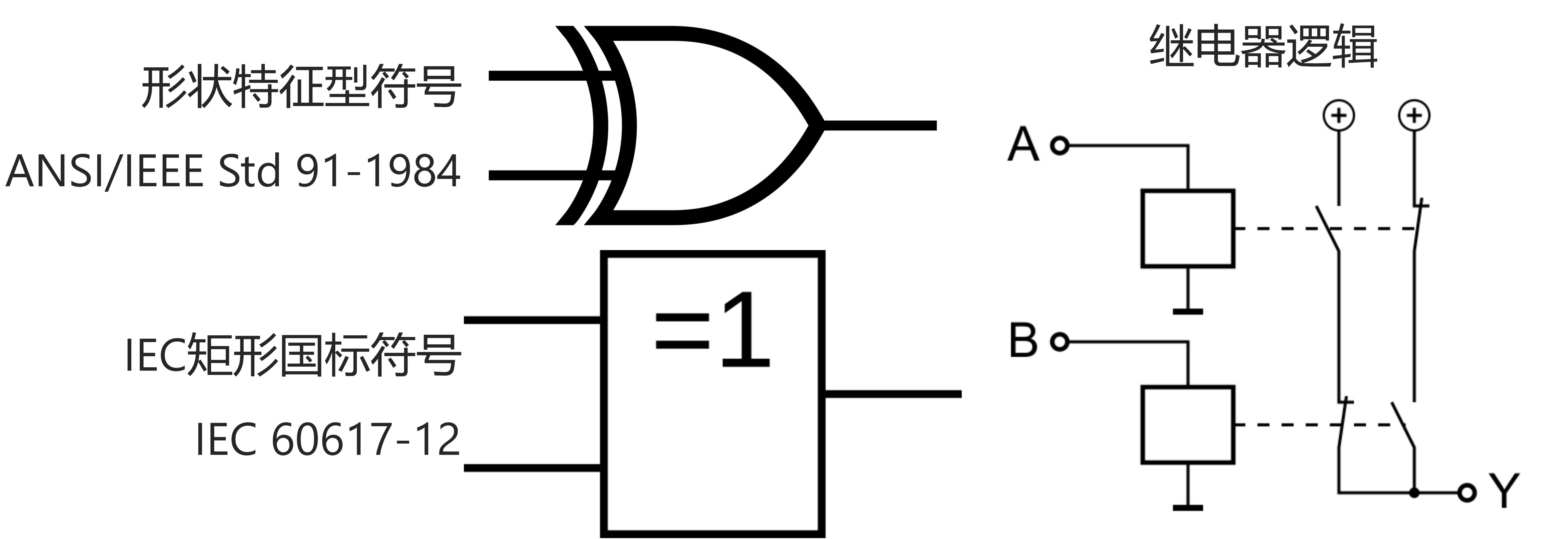

异或XOR

异或门(英语:Exclusive-OR gate,简称XOR gate,又称EOR gate、ExOR gate)是数字逻辑中实现逻辑异或的逻辑门,功能见右侧真值表。若两个输入的电平相异,则输出为高电平(1);若两个输入的电平相同,则输出为低电平(0)。

这一函数能实现模为2的加法,因此,异或门可以实现计算机中的二进制加法。半加器是由异或门和与门组成的。

真值表:

| A | B | A⊕B |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

同或XNOR

同或门(英语:XNOR gate,偶尔写作ENOR gate、ExNOR gate,在Intel处理器中,此项功能被命名为"test"),又称异或非门,是数字逻辑中实现逻辑双条件的逻辑门,功能见右侧真值表。若两个输入的电平相同,则输出为高电平(1);若两个输入的电平相异,则输出为低电平(0)。

真值表:

| A | B | A⊕B | A⊙B |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

逻辑代数运算规则

与乘除法类似,满足交换律、结合律、分配律,不再赘述。

特别注意分配律的变式:A+BC=(A+B)(A+C)

由于逻辑变量的值只有0和1,还满足0-1律和互补率。

0-1律

A+0=A//0为断路,并联之后,结果是否导通取决于A,结果为AA·0=0//0为断路,与A串联,无论A为多少,一定不导通,结果为0A+1=1//1为通络,与A并联后,无论A为多少,一定导通,结果为1A·1=A//1为通络,与A串联后,结果是否导通取决于A,结果为A

互补律

A+A'=1//由于A与A’互反,并联之后,一定有一条分路导通,结果为1AA'=1//由于A与A’互反,串联之后,一定有一部分断开,一定不导通,结果为0

重叠律

A+A=A,AA=A

//A与A并联或串联,结果是否导通,取决于A

该定律说明一个变量多次自与、自或的结果仍为自身,即逻辑代数中不存在倍率和方幂运算。

吸收律

A+AB=A,A(A+B)=A

//很明显,电路是否导通,取决于A

该定律说明表达式中A项包含了式中另一项,则该项可以去掉。

消去律(消因子公式)

A+A'B=A+B,A(A'+B)=AB

//A和B只要有一个为1,结果为1

并项律

AB+AB'=A,(A+B)(A+B')=A

//B的值不影响最终结果

复原律(还原律)

A’'=A

冗余律(消项公式)

AB+A'C+BC=AB+AC

(A+B)(A'+C)(B+C)=(A+B)(A'+C)

该定律说明当表达式中某个变量以原变量和反变量的形式出现在两项中时,该两项的其他变量组成的第三项是多余的,可以去掉。

德·摩根定律

(A+B)'=A'B',(AB)'=A'+B'

并集的补集是补集的交集,交集的补集是补集的并集

逻辑函数基础

基本规则

代入规则

任何一个含有变量 X 的等式,如果将所有出现 X 的位置,都代之以一个逻辑函数 F,此等式仍然成立。

对偶规则

设 F 是一个逻辑函数式,如果将 F 中的所有的 * 变成 +,+ 变成 *,0 变成 1,1 变成 0,而变量保持不变。那么就的得到了一个逻辑函数式 F’,这个 F’ 就称为 F 的对偶式。如果两个逻辑函数 F 和 G 相等,则它们各自的对偶式 F’ 和 G’ 也相等。

反演规则

当已知一个逻辑函数 F,要求 ¬F 时,只要把 F 中的所有 * 变成 +,+ 变成 *,0 变成 1,1 变成 0,原变量变成反变量,反变量变成原变量,即得 ¬F。 使用反演规则时要注意保持原函数中逻辑运算的优先顺序。

最小项&最大项

当用"与或"或者"或与"式表示一个逻辑函数时,有两种表达式特别重要。

一种是用"最小项"构成的"与或"式;

另一种是用"最大项"构成的"或与"式。

为了学习这两种重要的逻辑表达式,我们首先要掌握最小项和最大项的概念。

最小项

对于 n 个变量的逻辑函数而言,它的与项如果包含全部 n 个变量,即每个变量以原变量或反变量的形式出现一次且只出现一次,那么这个与项就称为该逻辑函数的最小项。

两个最小项如仅有一个变量因子不同,其他变量均相同,则称这两个最小项相邻。

最小项编号

任何一个最小项用 Mi表示,M表示最小项,下标i为使该最小项为1的变量取值所对应的等效十进制数。

如A'BC,取值011时为1,因此这一项的编号为3。

一个最小项,只要把原变量当成1,反变量当成0,便可直接得到它的编号。

最小项性质:

- 对于任意一个最小项,只有一组变量的取值才能使其值为1

- 任意两个不同的最小项之积为0

- n个变量的全部最小项之和为1

- 相邻最小项相或,可以合并成一项,并可以消去一个变量因子(没用)

最大项:与最小项相反

对于 n 个变量的逻辑函数而言,它的或项如果包含 全部n 个变量,即每个变量以原变量或反变量的形式出现一次且只出现一次,那么这个或项就称为该逻辑函数的最大项。

两个最大项如仅有一个变量因子不同,其它变量均相同,则称这两个最大项相邻。这与最小项相邻的规律相同。

最大项编号

任何一个最小项用 Mi表示,M表示最大项,下标i为使该最小项为0的变量取值所对应的等效十进制数。

如A'+B+C,取值100时为0,因此这一项的编号为4

最大项性质:

- 每一个最大项都只有一组变量的取值才能使其值为0

- 不同的最大项相或,结果为1

- n个变量的全部最大项之积为0

- 相邻最大项相与,可以合并成一项,并可以消去一个变量因子(没用)

- n个变量的任何一个最大项有n个相邻最大项(没用)

最小项和最大项的关系

编号相同的最小项和最大项互为反函数。

标准形式

逻辑变量的逻辑与运算叫做与项,与项的逻辑或运算构成了逻辑函数的与或式,也叫做积之和式(SP form)。

逻辑变量的逻辑或运算叫做或项,或项的逻辑与运算构成了逻辑函数的或与式,也叫做和之积式(PS form)。

标准与或

如果一个逻辑表达式为与或式,而且其中每个与项都是最小项,则称该逻辑表达式为标准与或式(或者标准积之和式,或者最小项之和形式)。

任一逻辑函数表达式都可以表示为标准与或式,而且是唯一的。

标准或与

如果一个逻辑表达式为或与式,而且其中每个或项都是最大项,则称该逻辑表达式为标准或与式(或者标准和之积式,或者最大项之积形式)。

任一逻辑函数表达式都可以表示为标准或与式,而且是唯一的。

![[1.3.2]计算机系统概述——中断和异常](https://img-blog.csdnimg.cn/d13cbc2731014ff4acd0a40eb10e5841.png)