本篇博客是考研期间学习王道课程 传送门 的笔记,以及一整年里对

计算机组成知识点的理解的总结。希望对新一届的计算机考研人提供帮助!!!

关于对 “总线” 章节知识点总结的十分全面,涵括了《计算机组成原理》课程里的全部要点(本人来来回回过了三遍视频),其中还陆陆续续补充了许多内容,所以读者可以相信本篇博客对于考研计算机组成原理 “总线” 章节知识点的正确性与全面性;但如果还有自主命题的学校,还需额外读者自行再观看对应学校的自主命题材料。

食用说明书:

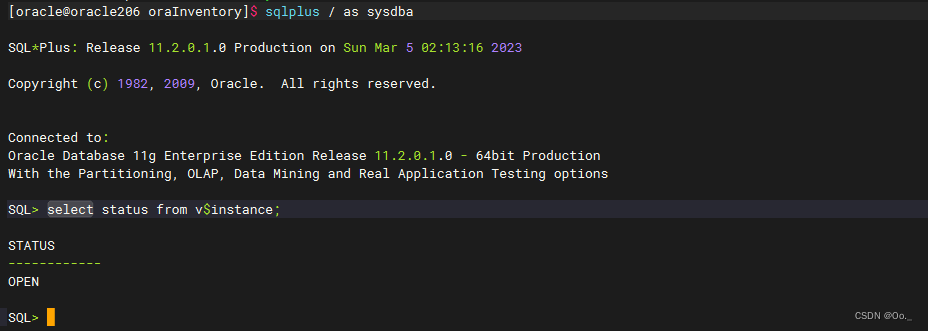

第一遍学习王道课程时,我的笔记只有标题和截图,后来复习发现看只看图片,并不能很快的了解截图中要重点表达的知识点。

在第二遍复习中,我给每一张截图中 标记了重点,以及 每张图片上方总结了该图片 对应的知识点 以及自己的 思考 。

最后第三遍,查漏补缺。

所以 ,我把目录放在博客的前面,就是希望读者可以结合目录结构去更好的学习知识点,之后冲刺复习阶段脑海里可以浮现出该知识结构,做到对每一个知识点熟稔于心!

请读者放心!目录展示的知识点结构是十分合理的,可以放心使用该结构去记忆学习!

注意(⊙o⊙)!,每张图片上面的文字,都是该图对应的知识点总结,方便读者更快理解图片内容。

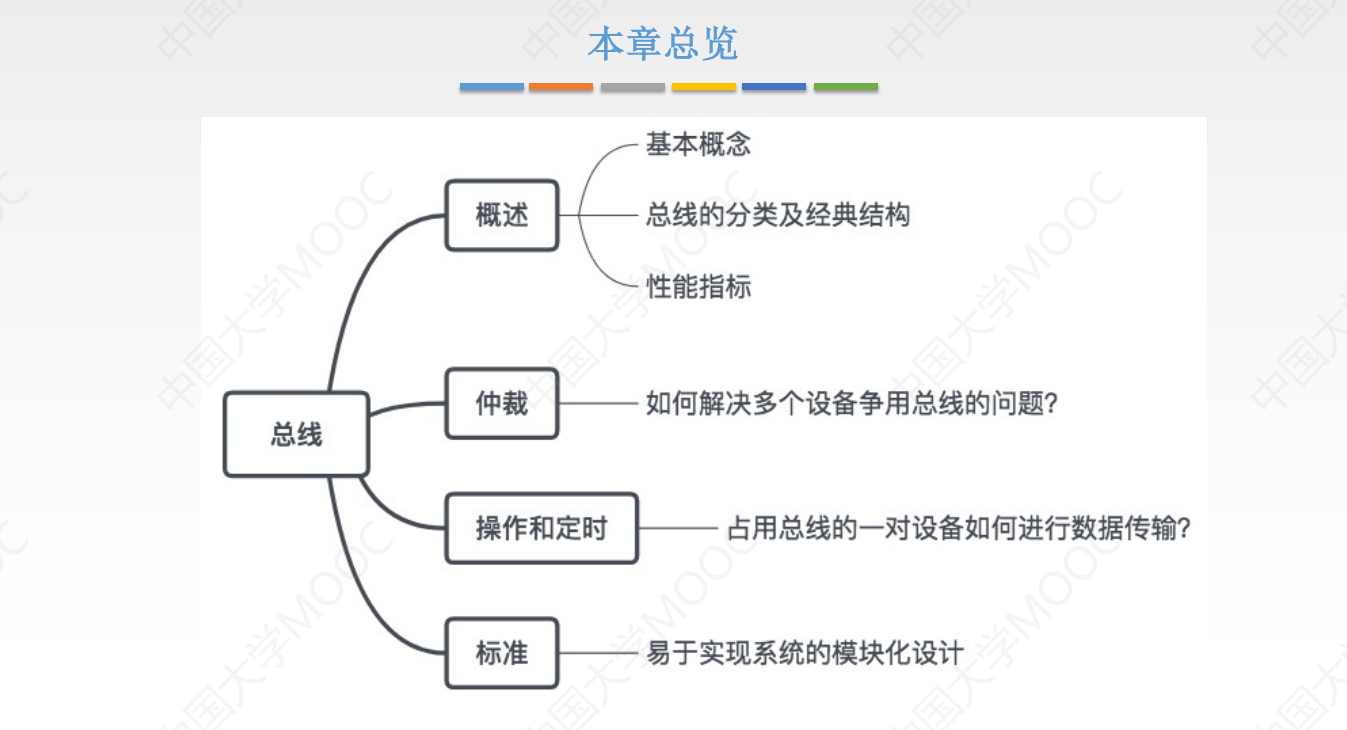

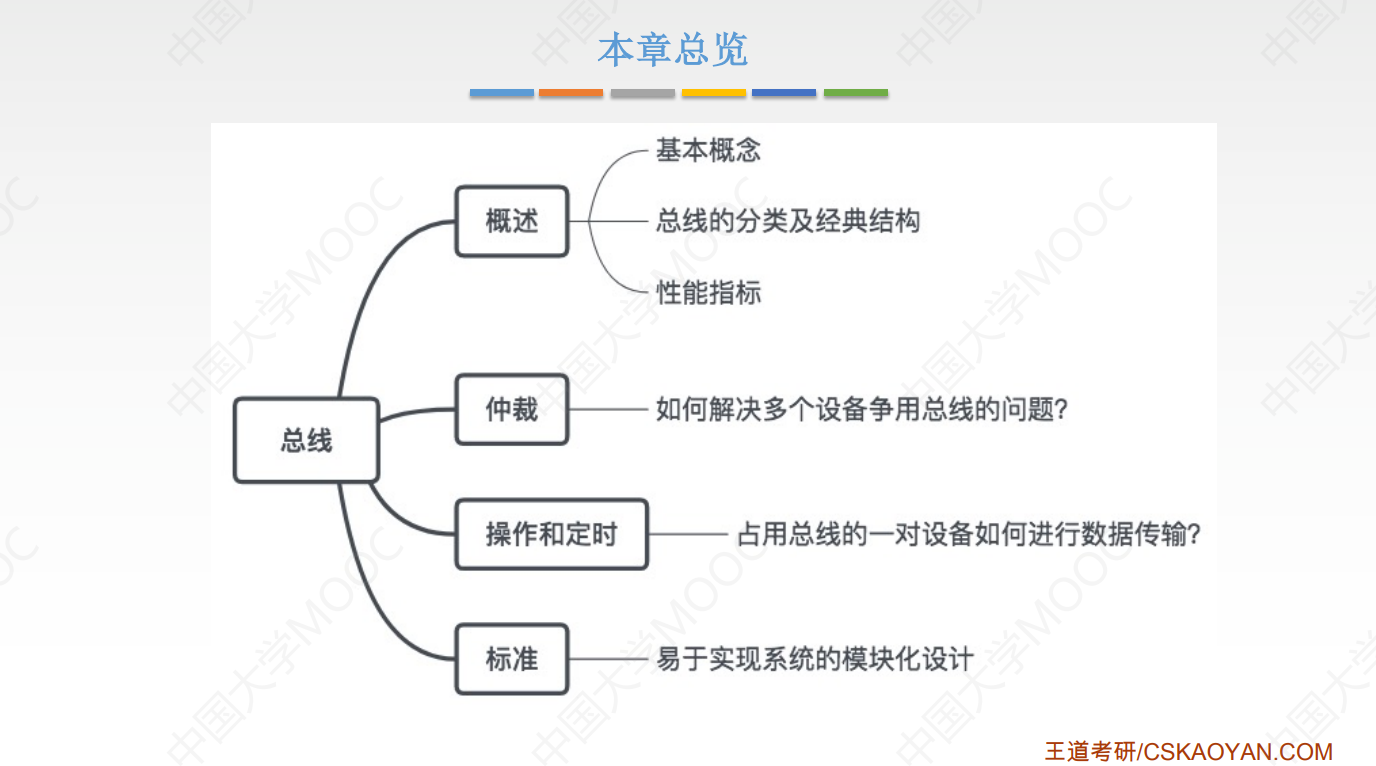

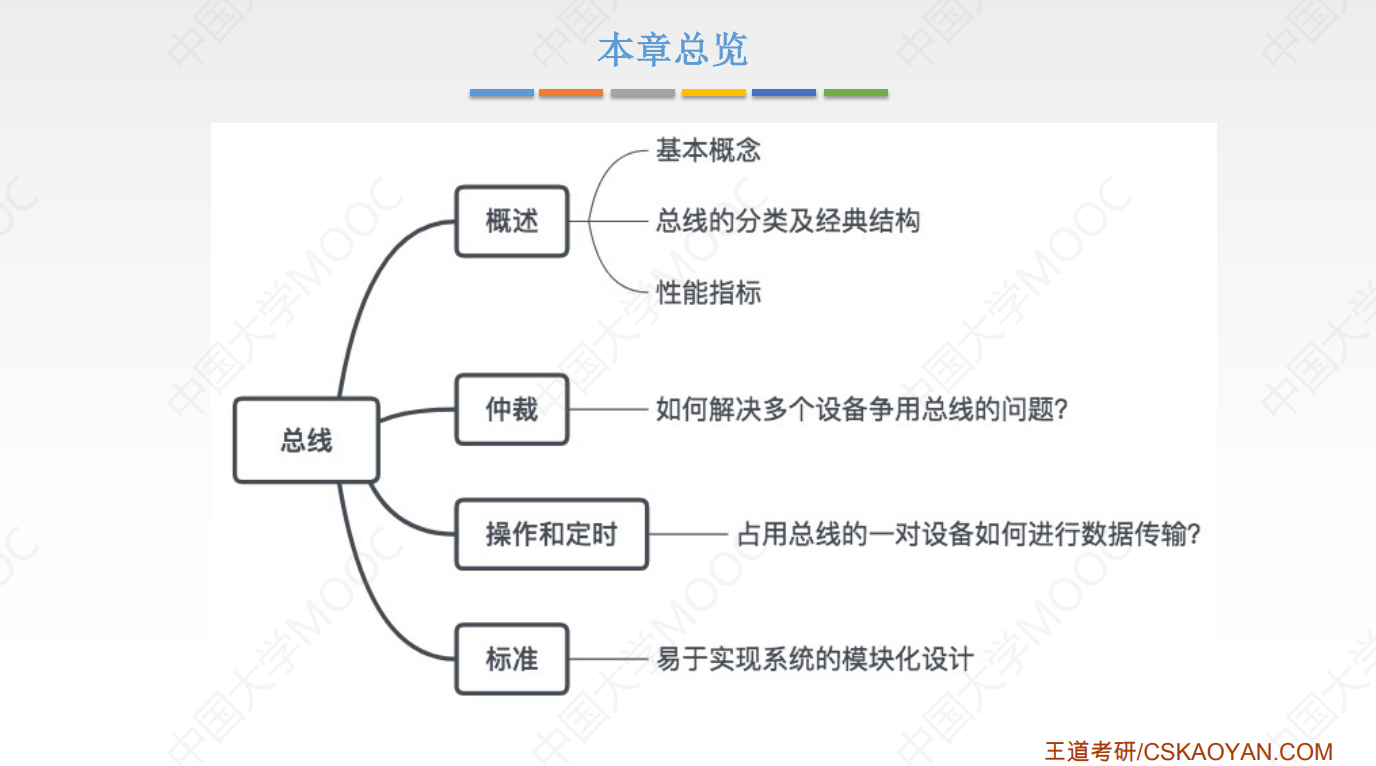

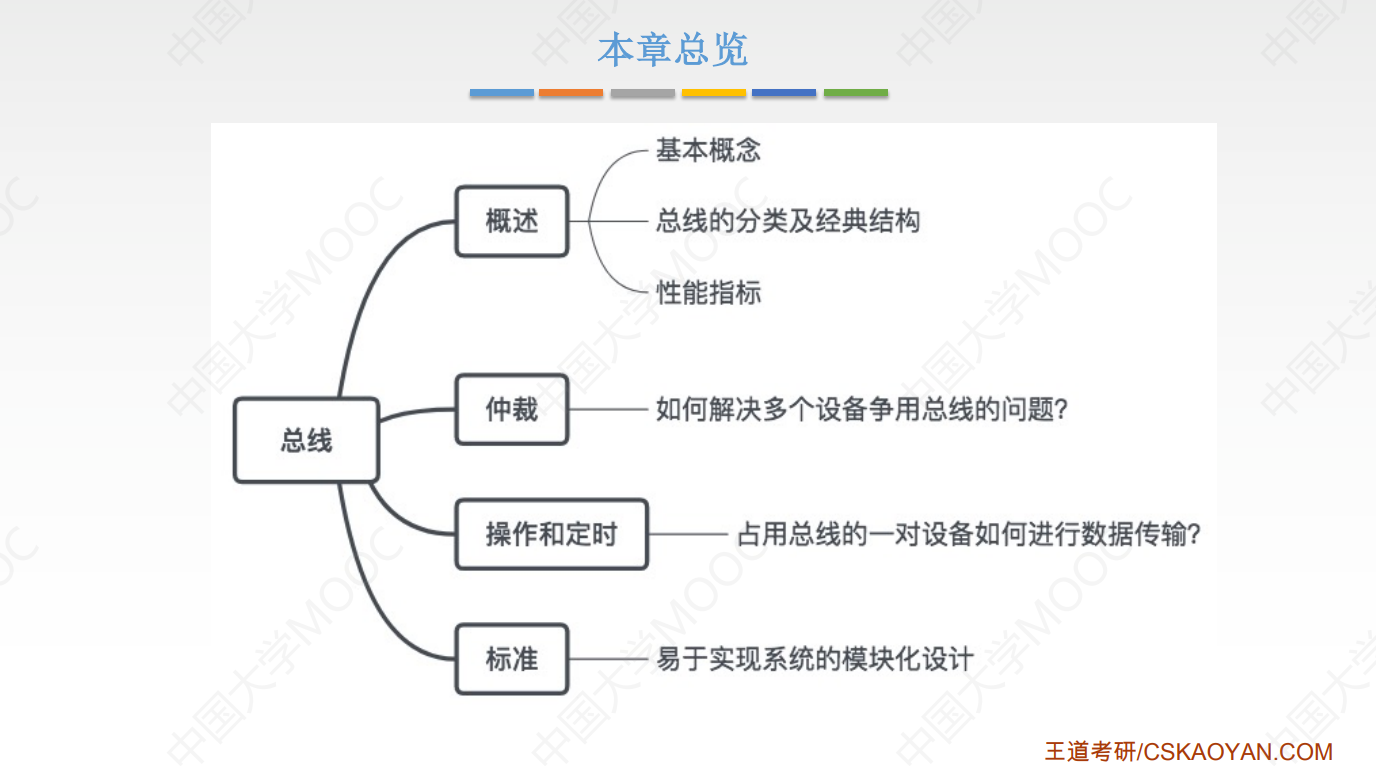

《计算机组成原理》第6章 总线

【考纲内容】

王道 P286 ~ 301 网课耗时:

0.5 h + 0.5 h + 0.5 h

- 总线的基本概念;

- 总线的组成及性能指标;

- 总线事务和定时;

【复习提示】

总线章节一般考察 ==选择题,==特别是 总线的特点、猝发传输方式、性能指标、定时方式 及 常见的总线标准;

总线带宽的计算 也可能结合其他章节出综合题;

除课后习题外,王道课本内容笔记里都包含 ;

6.1 总线概述

6.1.1 总线的基本概念

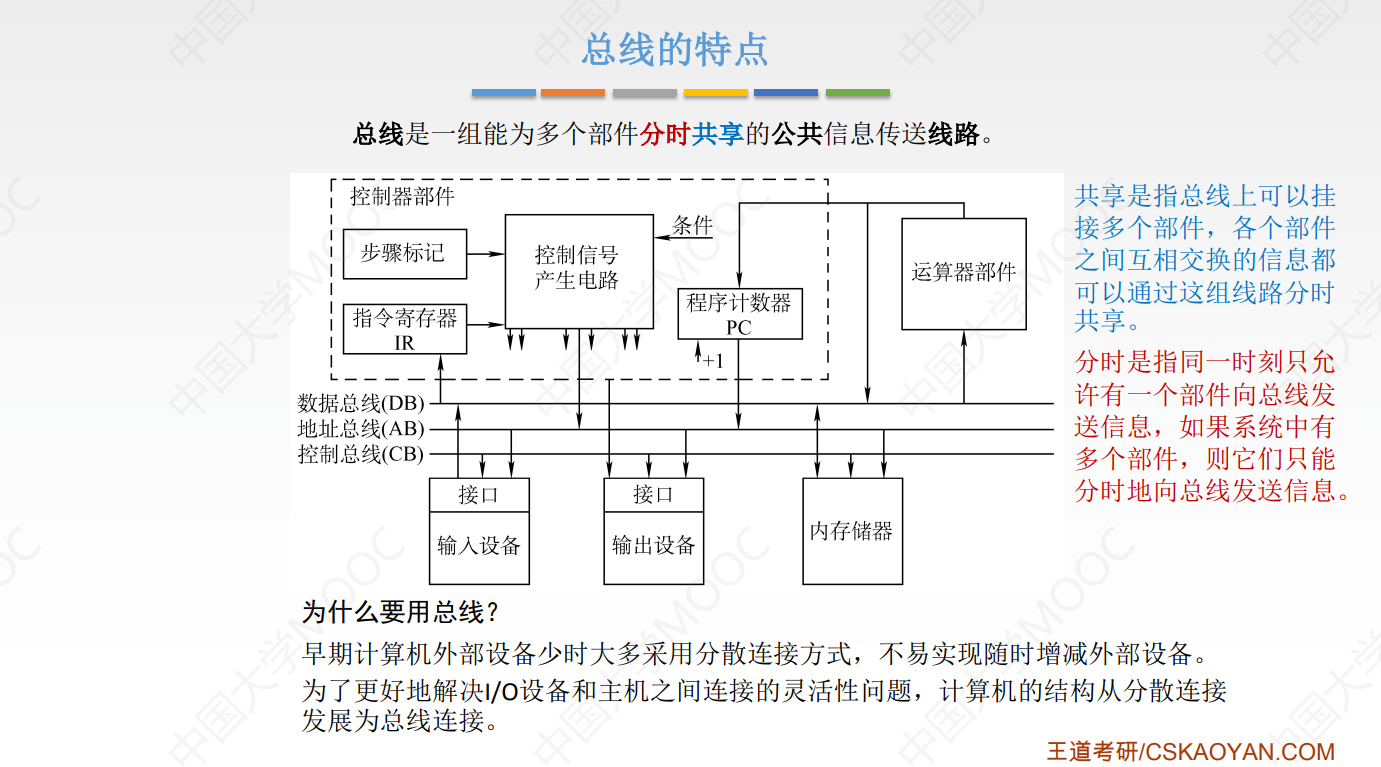

1. 总线的基本概念

① 计算机系统五大部件的互连方式

随着技术发展,计算机结构从 分散连接 发展为 总线连接 :

分散连接:各部件之间使用单独的连线;

总线连接:各部件连到一组公共信息传输线上;

② 为什么要使用 总线连接方式 ?

分散连接是 两两相连 ,需要通信的两个部件,使用线路连接起来;

但是如果两两连接的数量太多时,不仅成本高,而且连接太麻烦了!

并且两两进行连接,就要求有对应的接口,但不可能有那么多接口,即占用空间,而且后续还难扩展!

所以逐渐使用 总线连接 的方式进行部件之间的连接;

③ 总线上的信息传输

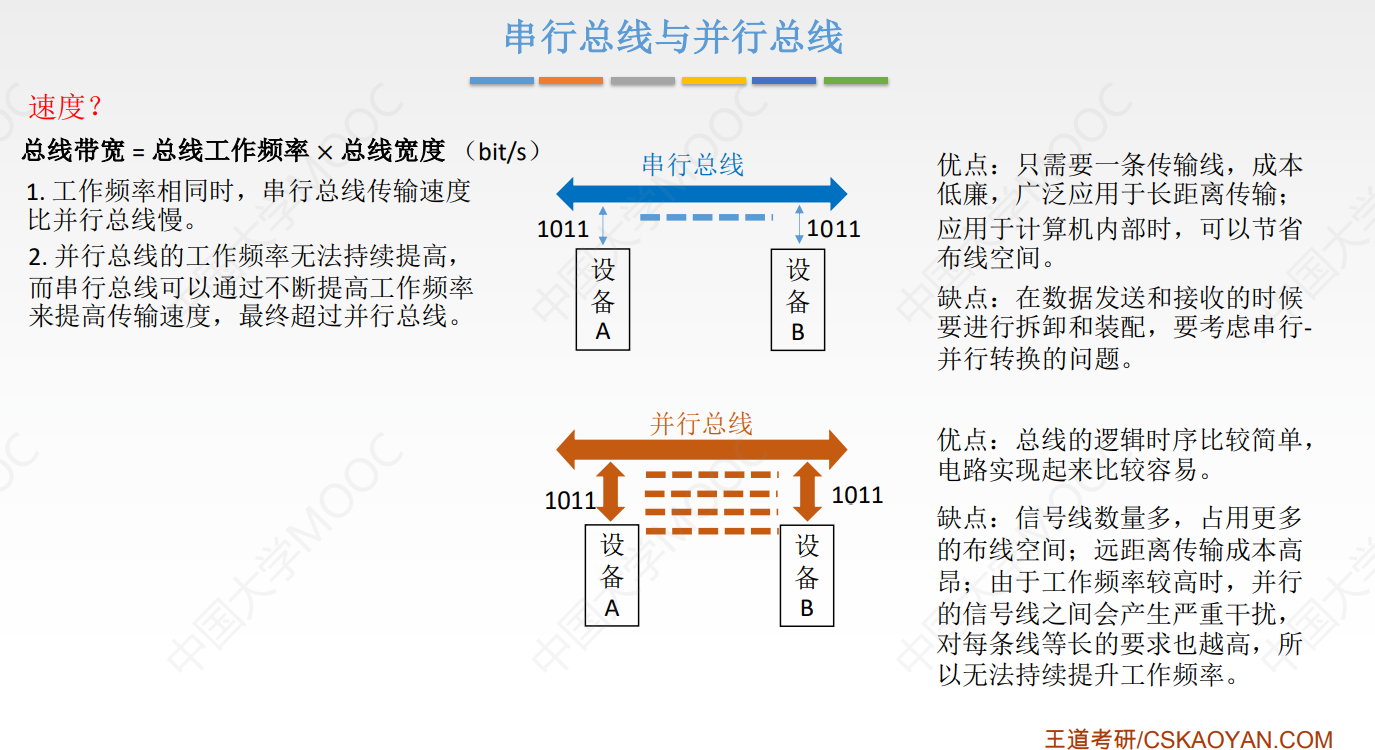

串行传输:一位一位地传输,一位一位地接收。(适合长距离传输)

并行传输:多位同时传输,多位同时接收。需要多条线,传输距离变长时,线与线之间会产生干扰,信号可能会发送变形。

(适合短距离传输)

2. 总线的定义和特性

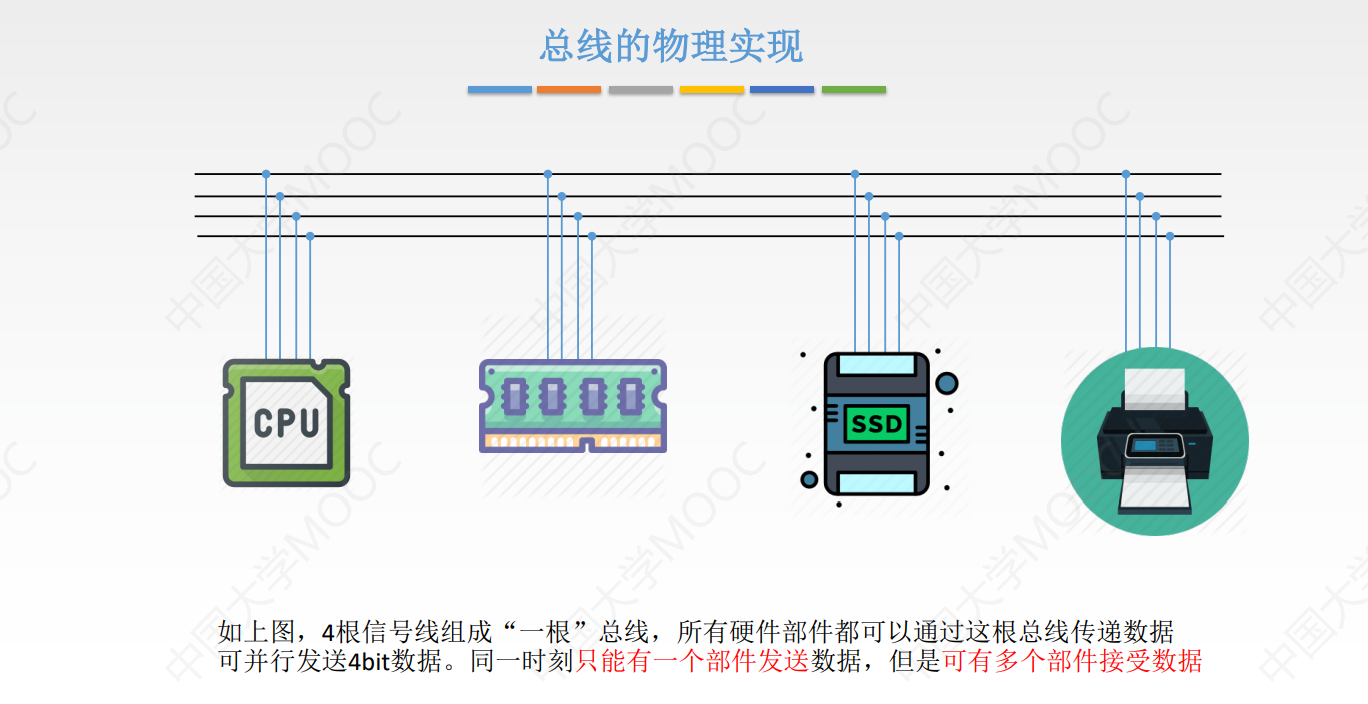

总线(Bus)是连接各个部件的信息传输线,是各个部件共享的传输介质;(唐朔飞版本定义) 总线是一组能为多个部件 分时共享 的公共信息传输线路;(王道版本)

- 分时:同一时刻只能有一个部件占用总线,避免多个部件向总线发送信息时,出现 信号冲突 问题(分时发送、同时接收);

- 共享:每个部件交换的信息可通过这组线路分时共享,接收相同信息;

从物理角度来看,总线由许多导线直接印刷在电路板上,延伸到各个部件(CPU、主存、I/O),这就要求其满足一些相应的物

理特性:

1. 机器特性:尺寸、形状、管脚数 及 排列顺序;

2. 电气特性:传输方向 和有效的 电平 范围;

3. 功能特性:每根传输线的功能(地址、数据、控制);

4. 时间特性:信号之间的时序关系;

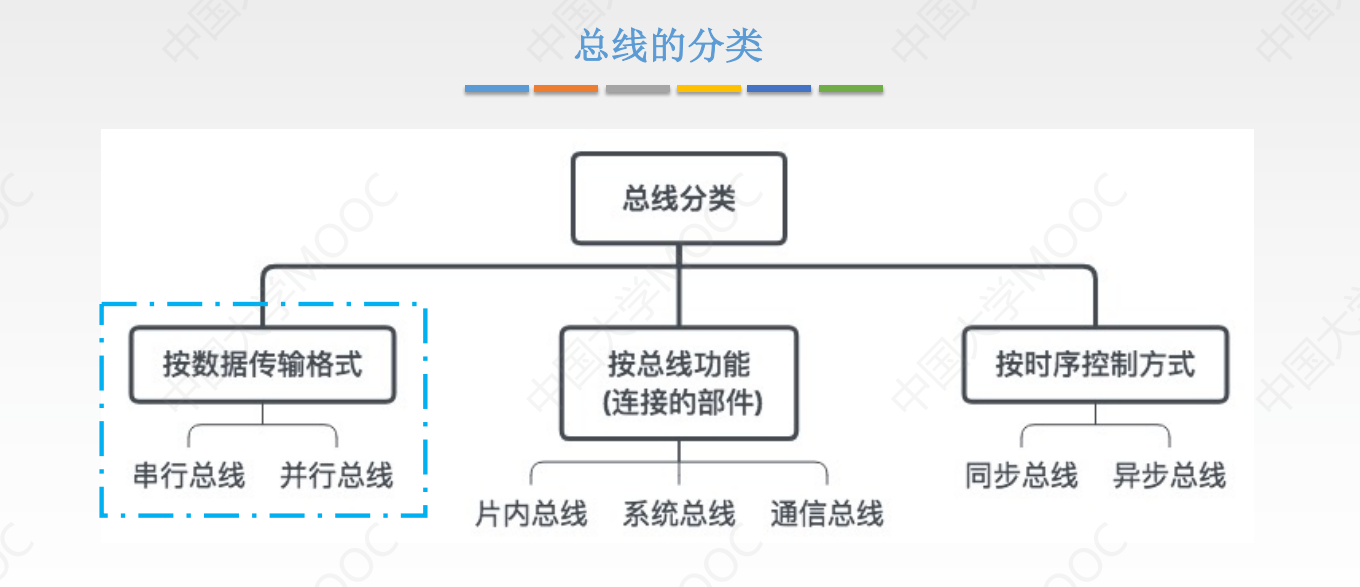

6.1.2 总线的分类

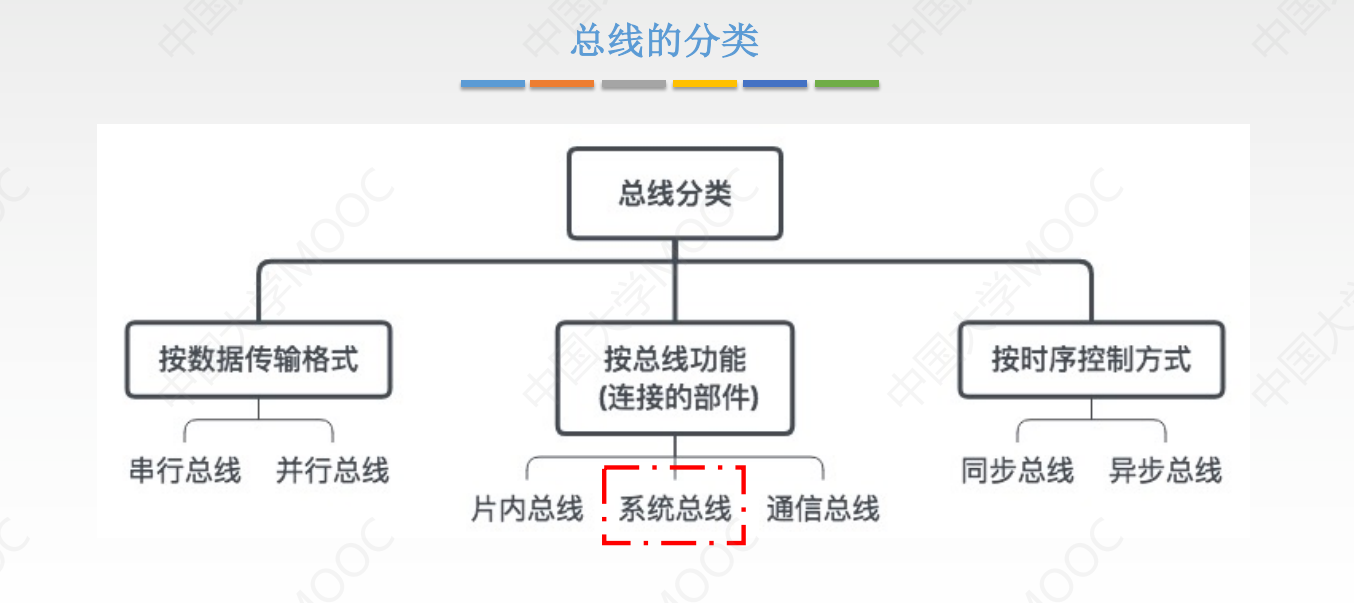

1. 按数据传输格式分类

串行总线:每次传输一位数据;

并行总线:每次传输多位数据;

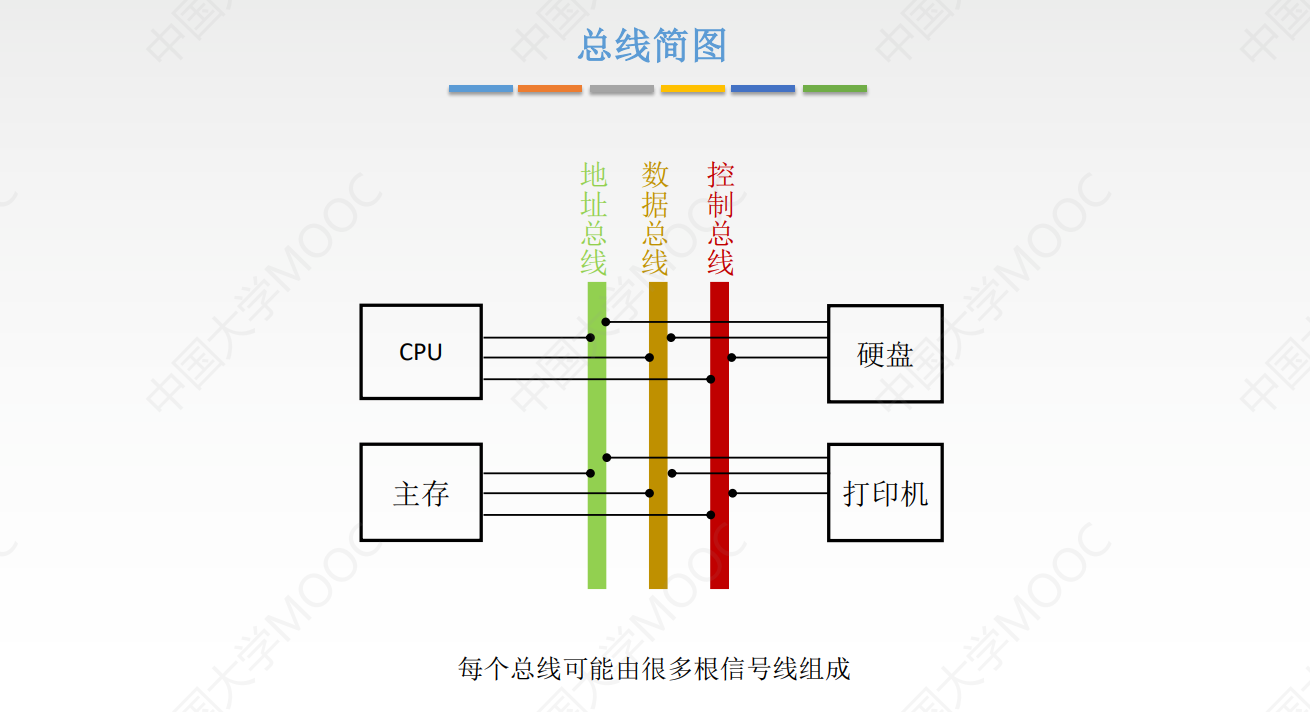

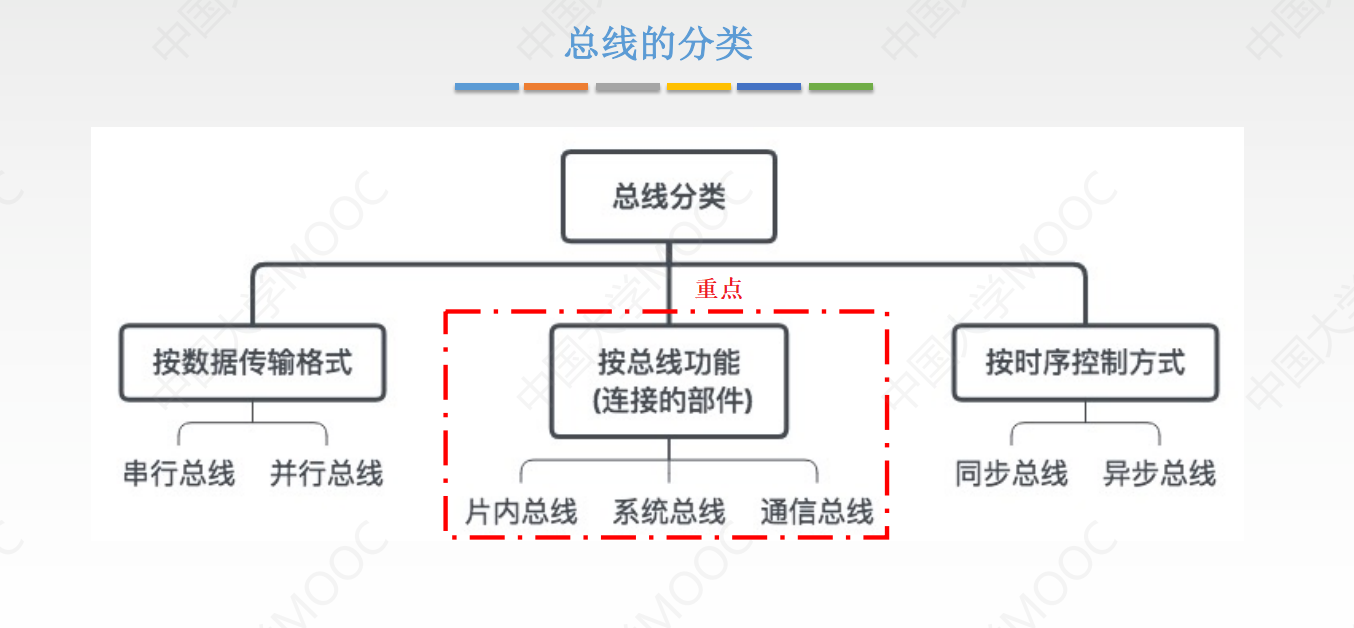

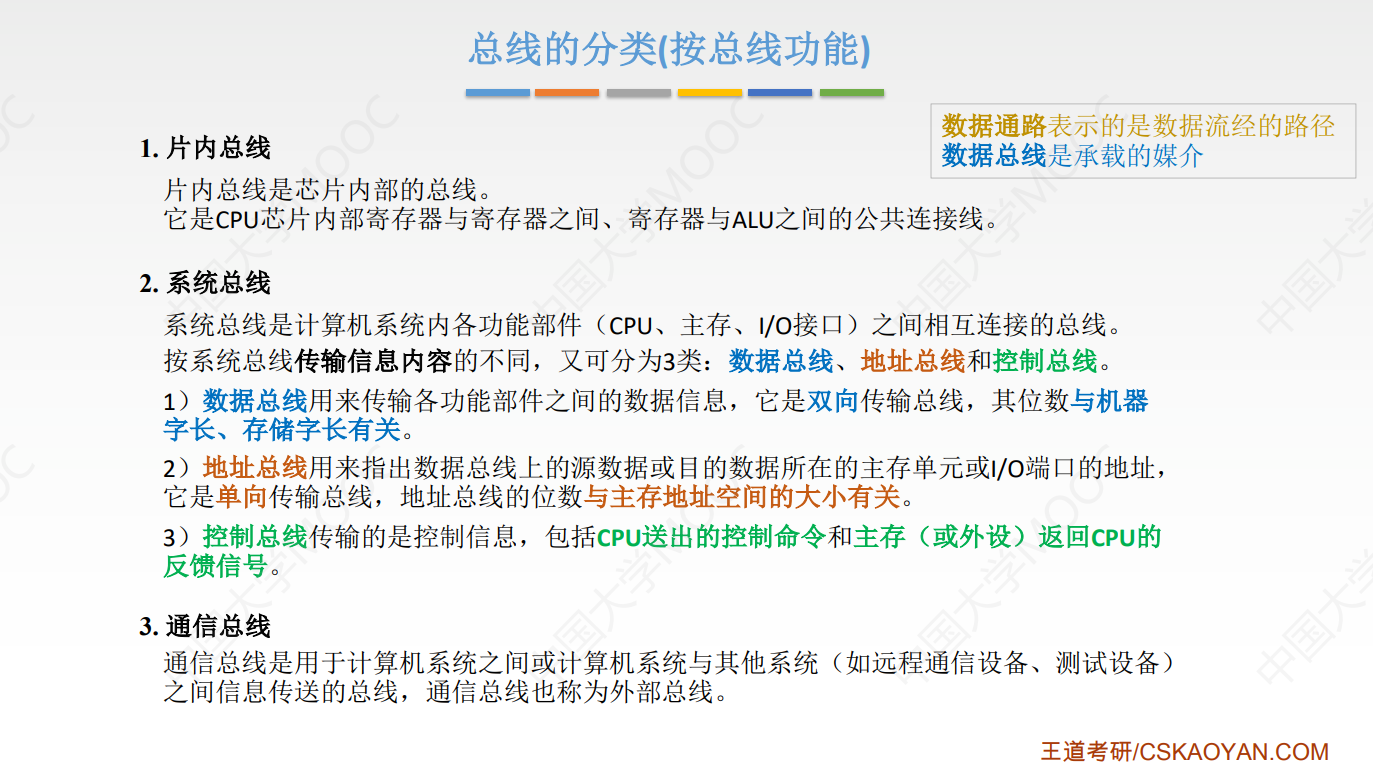

2. 按总线功能分类 ⭐

① 片内总线

芯片内部 的总线

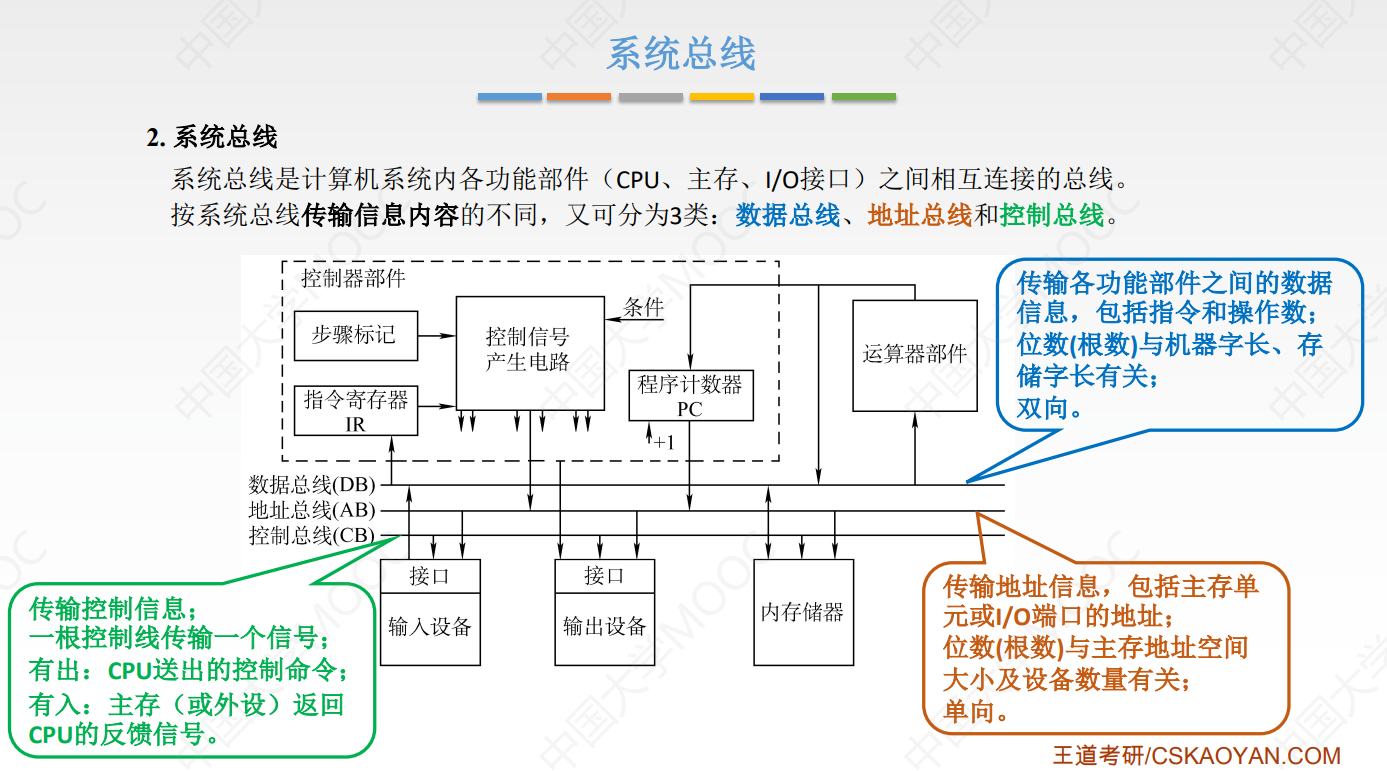

(CPU内部级别);② 系统总线 ⭐

计算机各部件之间 的信息传输线

(计算机内部级别) 按系统总线传输信息进一步划分:

- ==数据总线:==传输各功能部件之间的数据信息。是 双向 的,其位数与机器字长、存储字长相关;

- ==地址总线:==指出 数据总线上源数据或目的数据 在 主存或I/O设备上的地址。是 单向 的,其位数与存储单元个数(存储地址、I/O设备)相关;

- ==控制总线:==用来发出各种控制信号的传输线,有出、有入。

例如:中断请求、总线请求、存储器读、存储器写、总线允许、中断确认等;

③ 通信总线

用于 计算机系统之间 或 计算机系统与其他系统(如控制仪表、移动通信等)之间的通信

(计算机级别) 传输方式:串行通信总线、并行通信总线;

IO总线主要用于连接中低速的IO设备,通过IO接口与系统总线相连接,目的是将低速设备与高速总线分离,以提升总线的系统性能,常见的有USB、PCI总线。

3. 按时序控制方式

略,非重点

6.1.3 总线的连接方式

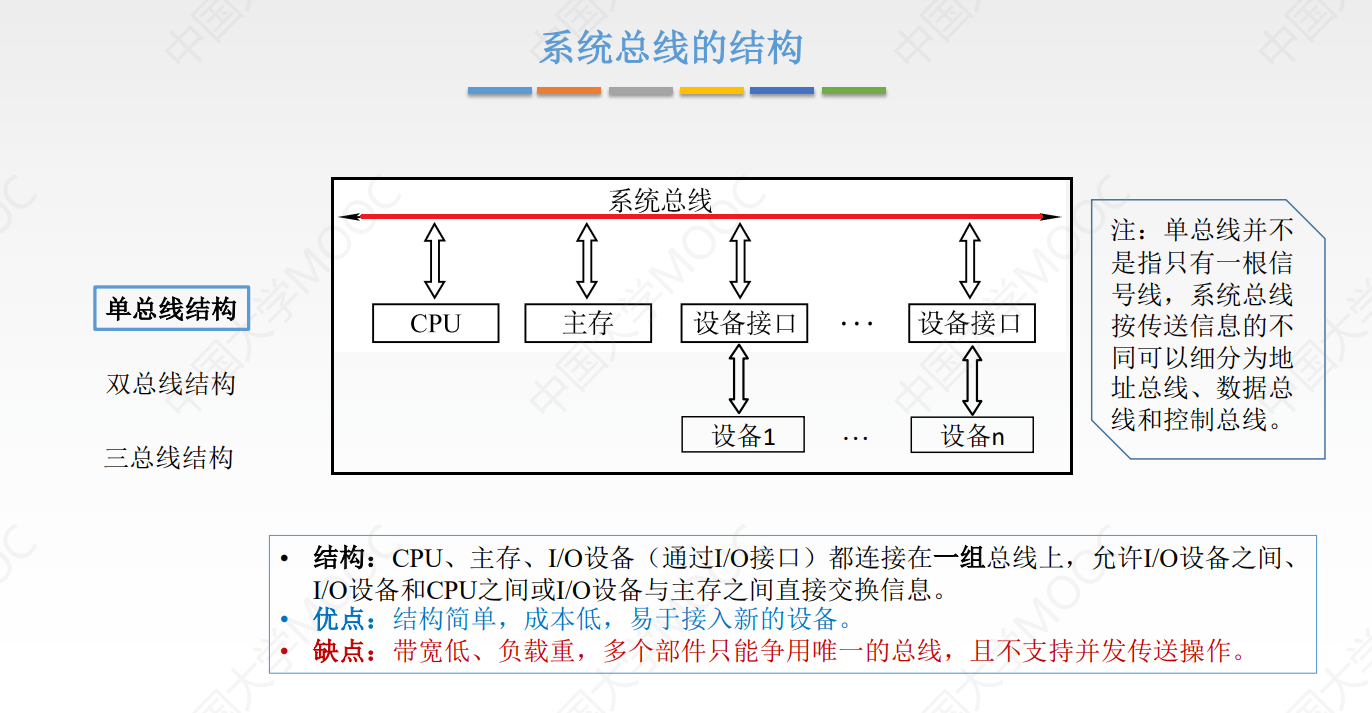

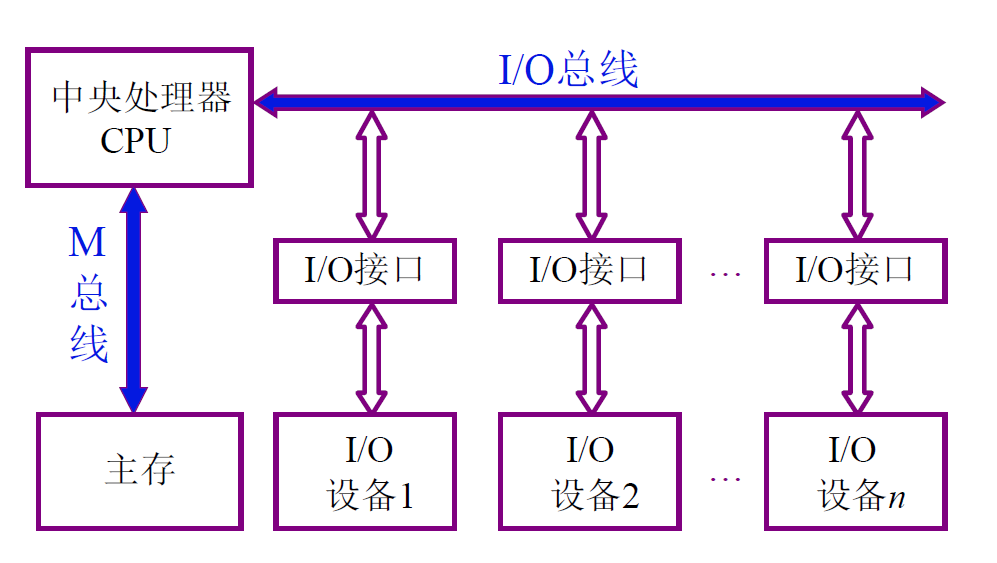

① 单总线结构

特点:一组总线、容易冲突 ;

针对总线冲突问题,可以设置 总线判优 逻辑,各部件按优先级来占用总线,但会影响整机的效率;

② 双总线结构

面向 CPU 的双总线结构,如下图所示(了解即可);

缺点:I/O设备与主存交换信息时仍然要占用CPU,所以会 影响CPU效率 ;

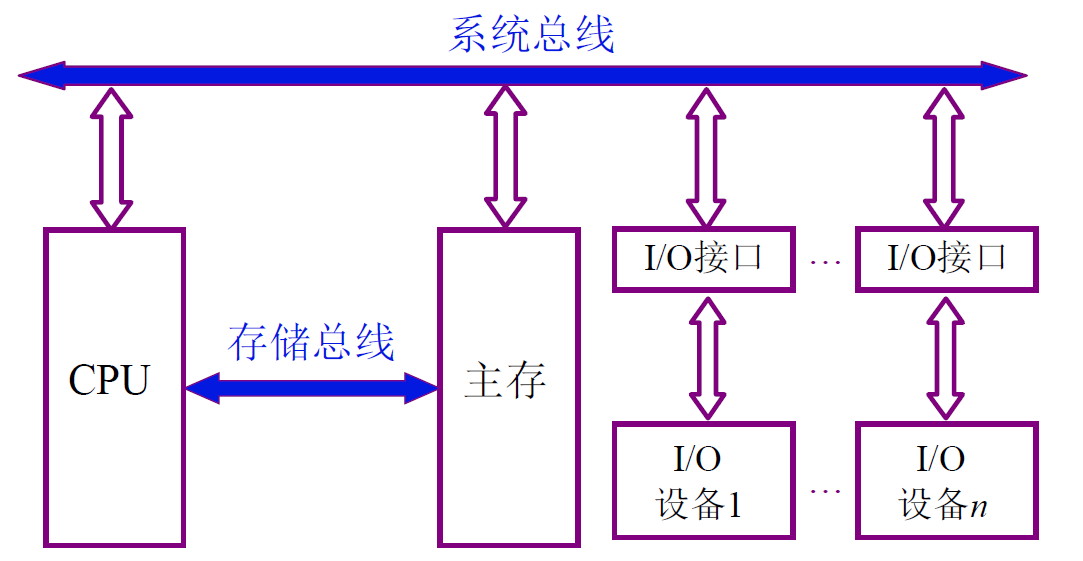

以 存储器 为中心的双总线结构,如下图所示(了解即可);

增加了 存储总线 ,即减轻了 单总线结构 中的 总线负担 问题,又不会出现 面向CPU的双总线结构 中影响CPU效率的情况;

不过现阶段,主存还是无法同时使用系统总线和存储总线。

加入 通道 的双总线结构,如下图所示;

单总线已经无法解决CPU、主存和I/O设备之间的传输速率不匹配问题,所以改进采用 多总线结构 ;

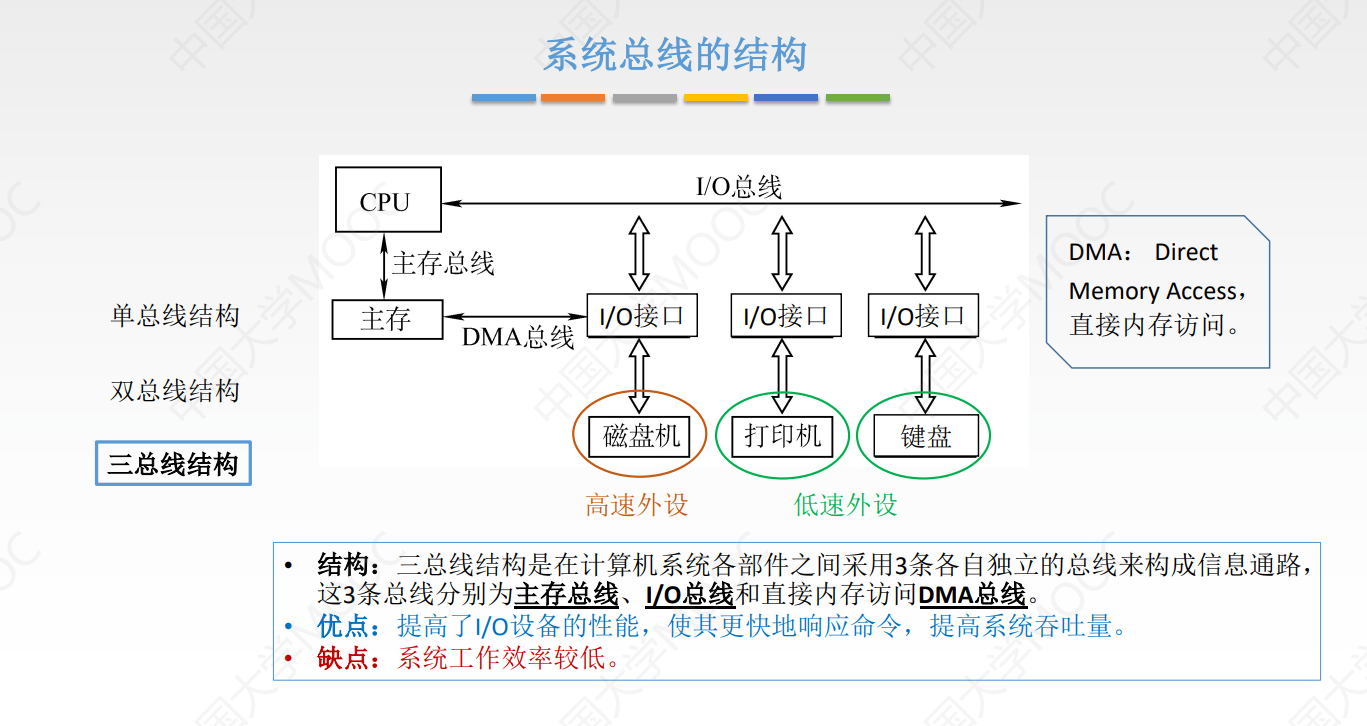

③ 三总线结构

将速率不同的I/O设备进行分类,然后将它们连接在不同的总线上,进一步提高计算机效率;

主存总线:CPU与主存之间的传输;

I/O总线:CPU与各类I/O设备之间传递信息;

DMA总线:高速I/O设备与主存之间直接交换信息;

任一时刻里,三总线只能使用一种总线;

主存总线与DMA总线不能同时对主存进行存取,I/O总线只能在CPU执行I/O指令时才能使用;

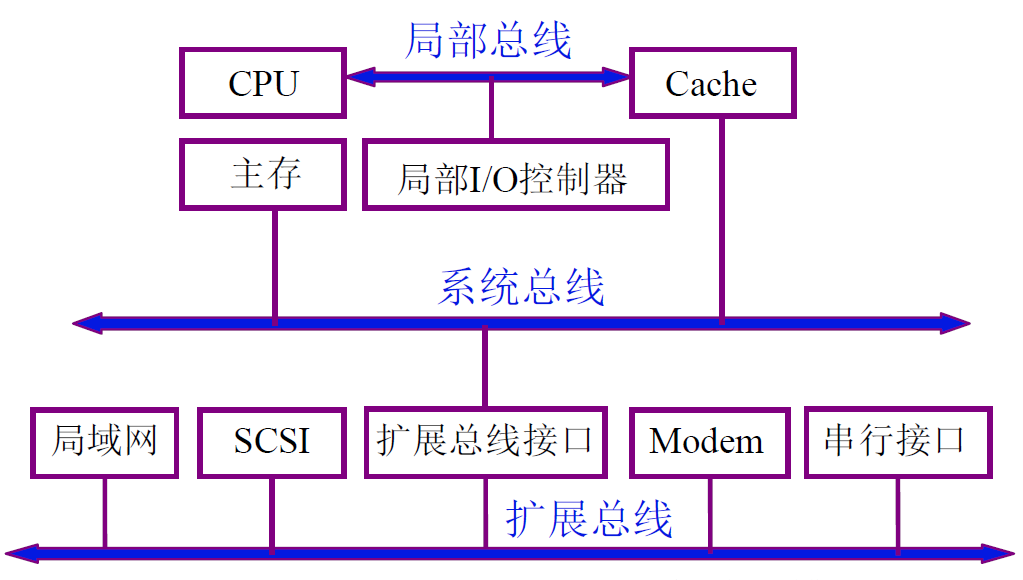

三总线结构的又一形式(简单了解,非重点)

CPU与主存的传输速率差距越来越大,所以在它们之间增加了Cache作为缓存,所以增加 局部总线 ;

另外还有 扩展总线 ,通过扩展总线接口与系统总线相连,其他接口与I/O设备相连实现扩展。

④ 四总线结构(简单了解,非重点)

在 三总线结构的又一形式 的结构中,多种不同传输速率的设备都连接到了扩展总线,这是会影响外部设备的工作效率。

所以又增加了==高速总线,==负责哪些高速设备的传输。低速设备还是连接原来的扩展总线,系统效率得到进一步提升!

小结

6.1.4 总线的性能指标

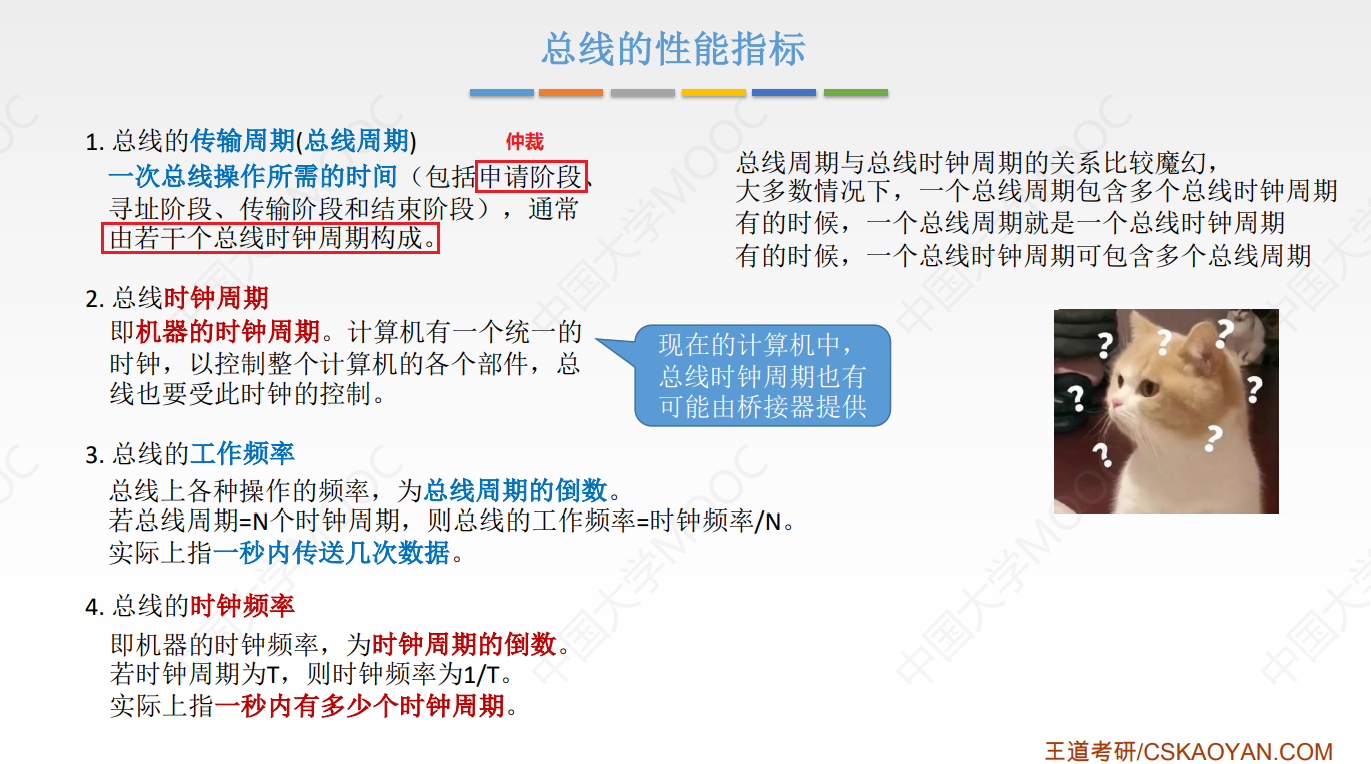

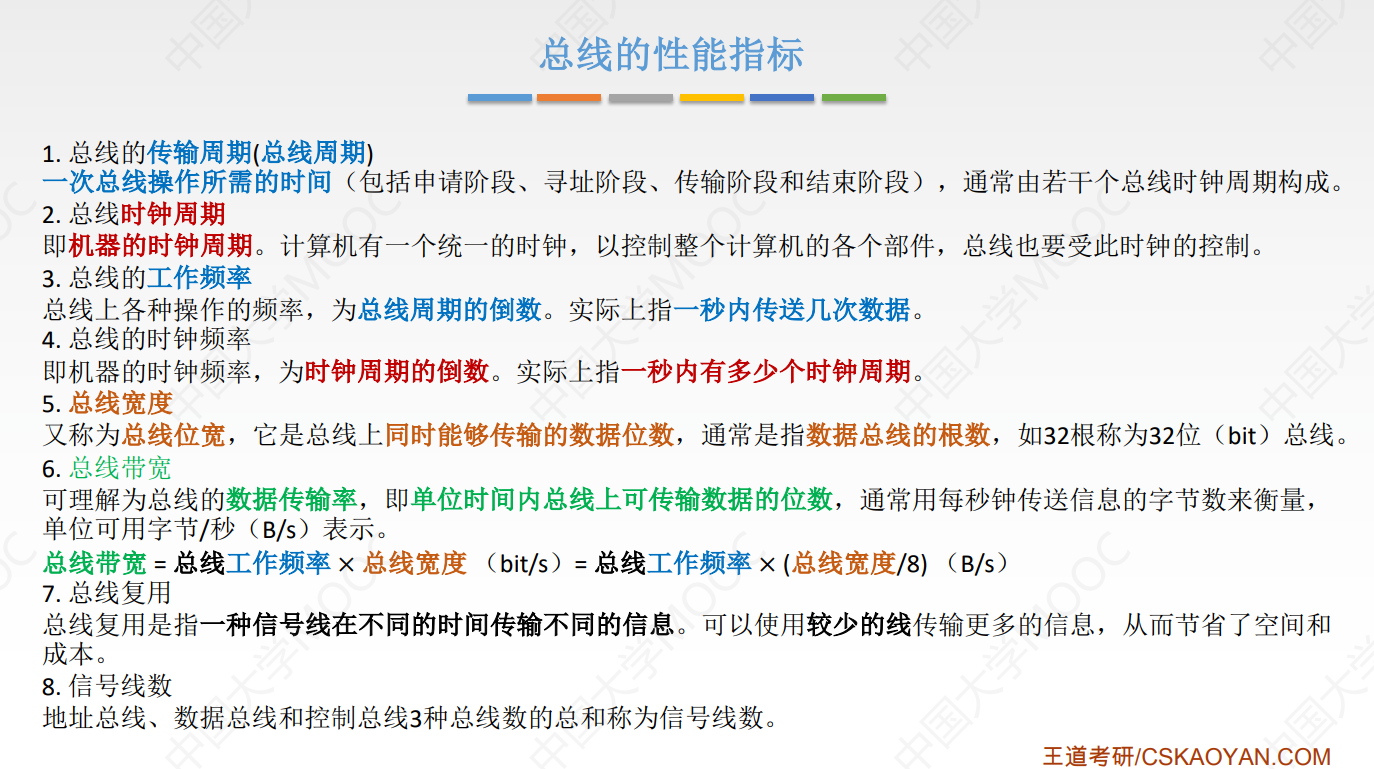

① 总线的传输周期 (总线周期)

② 总线时钟周期

③ 总线的工作频率

④ 总线的时钟频率

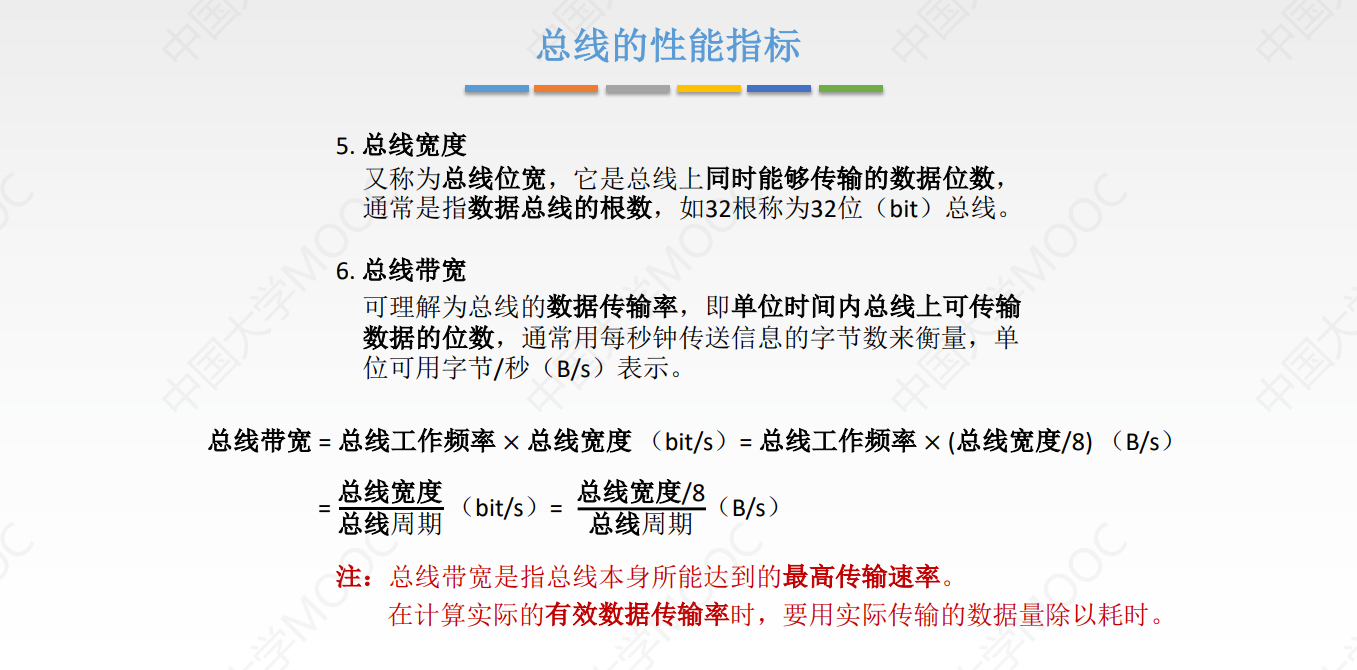

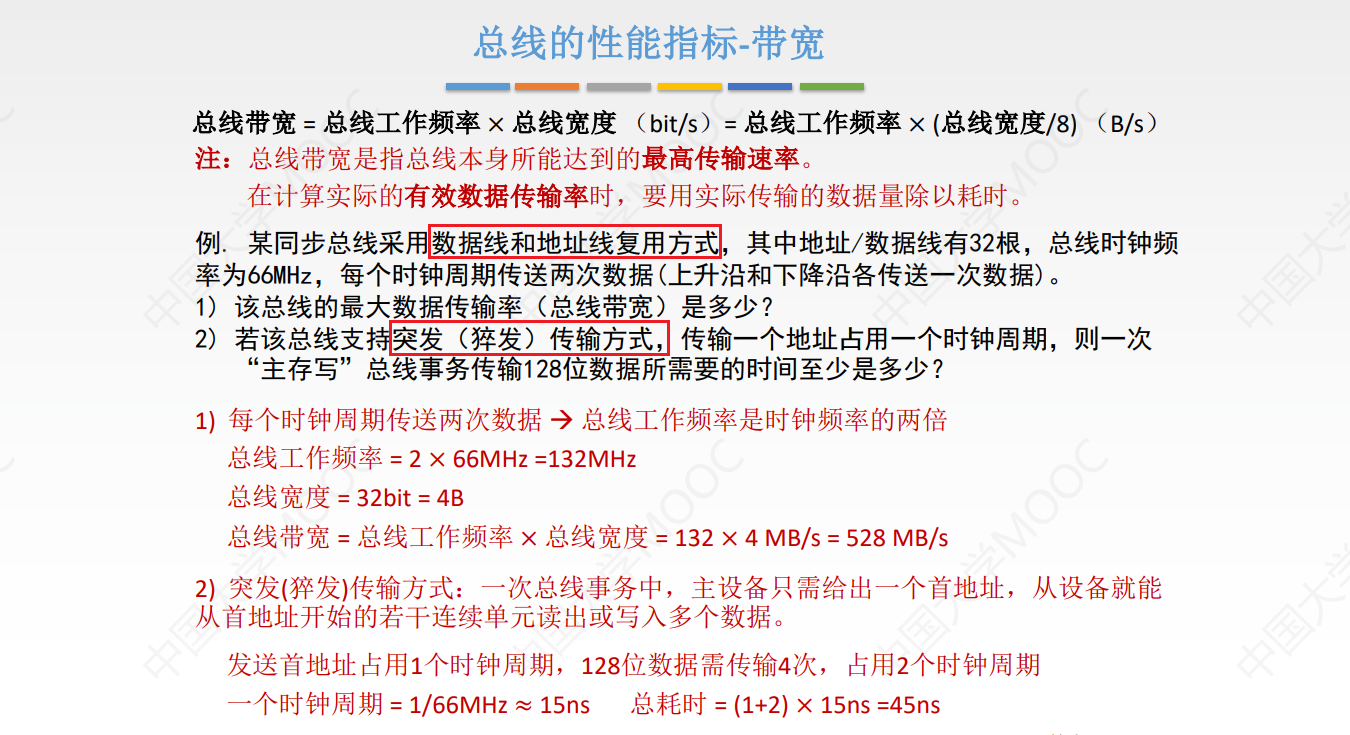

⑤ 总线宽度

总线位宽,指 数据线的根数;

⑥ 总线带宽 (标准传输率)

指每秒传输的最大字节数;

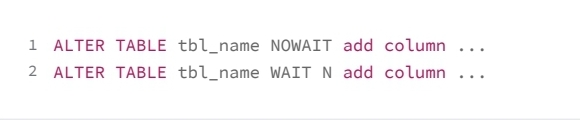

数据线和地址线复用 :分时使用同一组总线;

突发传输方式 :传送一次地址,之后可以连续读出(或写入)这个地址之后的多个数据;

串行总线和并行总线的总线带宽

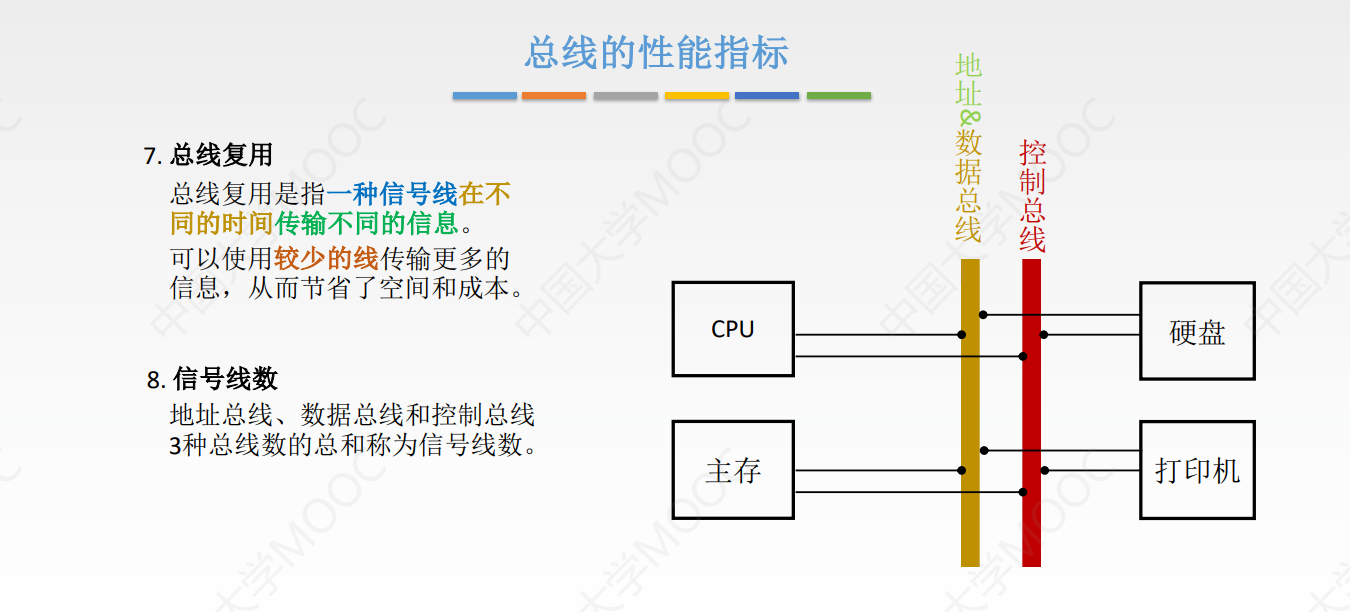

⑦ 总线复用

地址线 与 数据线 复用;

⑧ 信号线数

地址线、数据线和控制线的数量总和;

小结

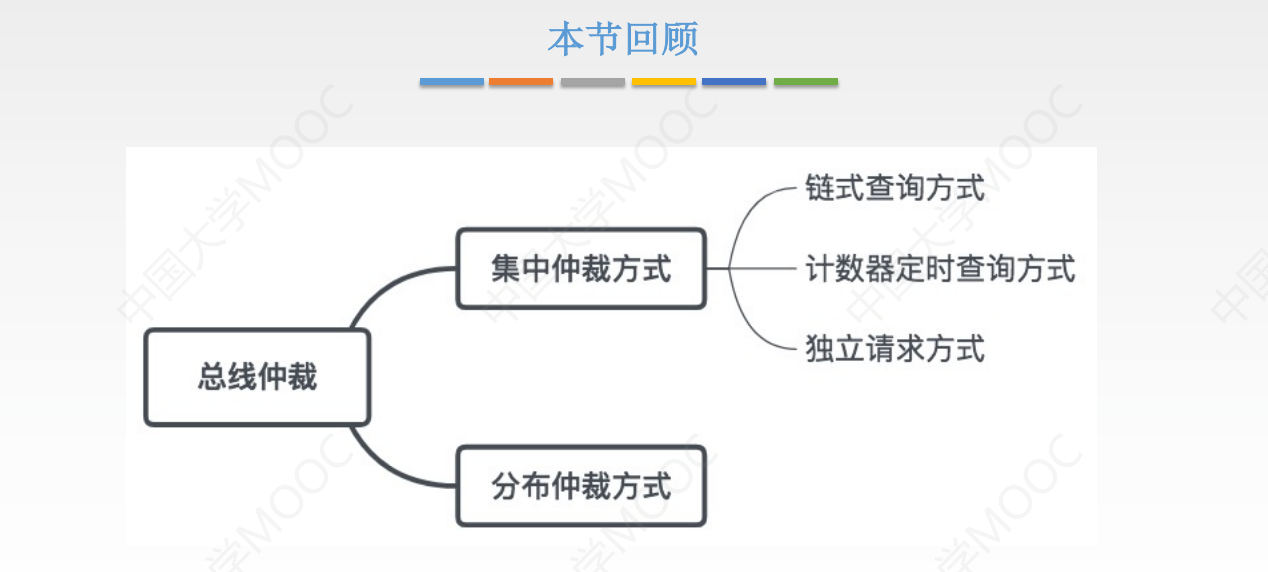

6.2 总线判优控制 *

总线上连接的多个设备,在数据传输时就需要面对多种控制问题,本节重点研究以下两个问题:

- 总线判优控制: 总线仲裁

- 总线通信控制:总线操作和定时

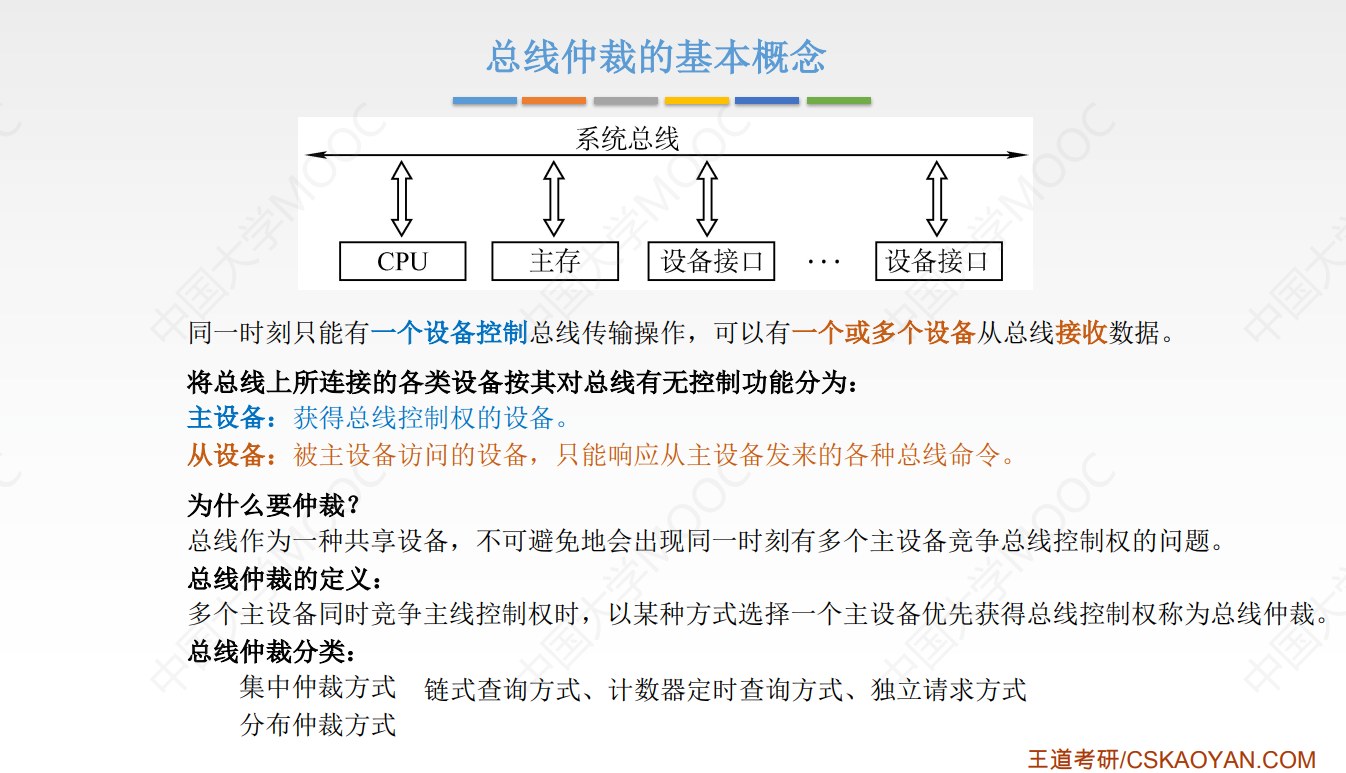

1. 总线仲裁的基本概念

==主设备(模块):==对总线有 控制权

==从设备(模块):==响应 从主设备发来的总线命令

==总线判优控制方式:==集中式(将控制逻辑集中在一处)、分布式(将控制逻辑分散在与总线连接的各个部件或设备上)

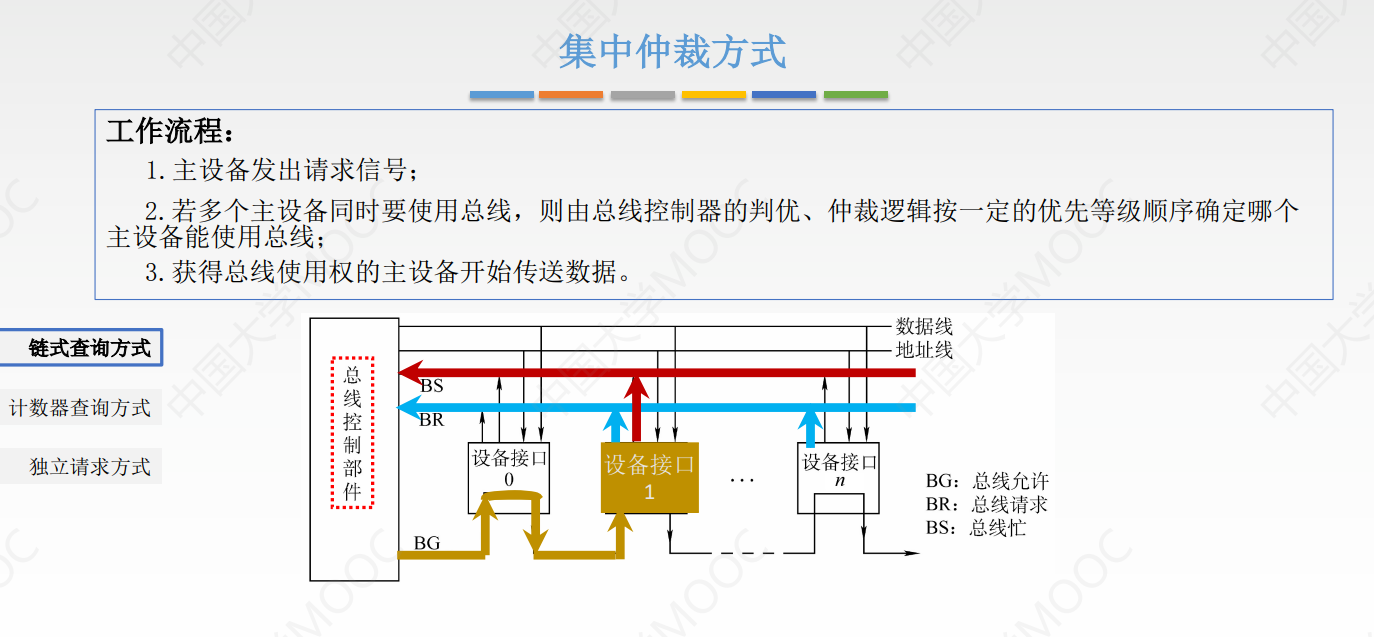

2. 集中仲裁方式

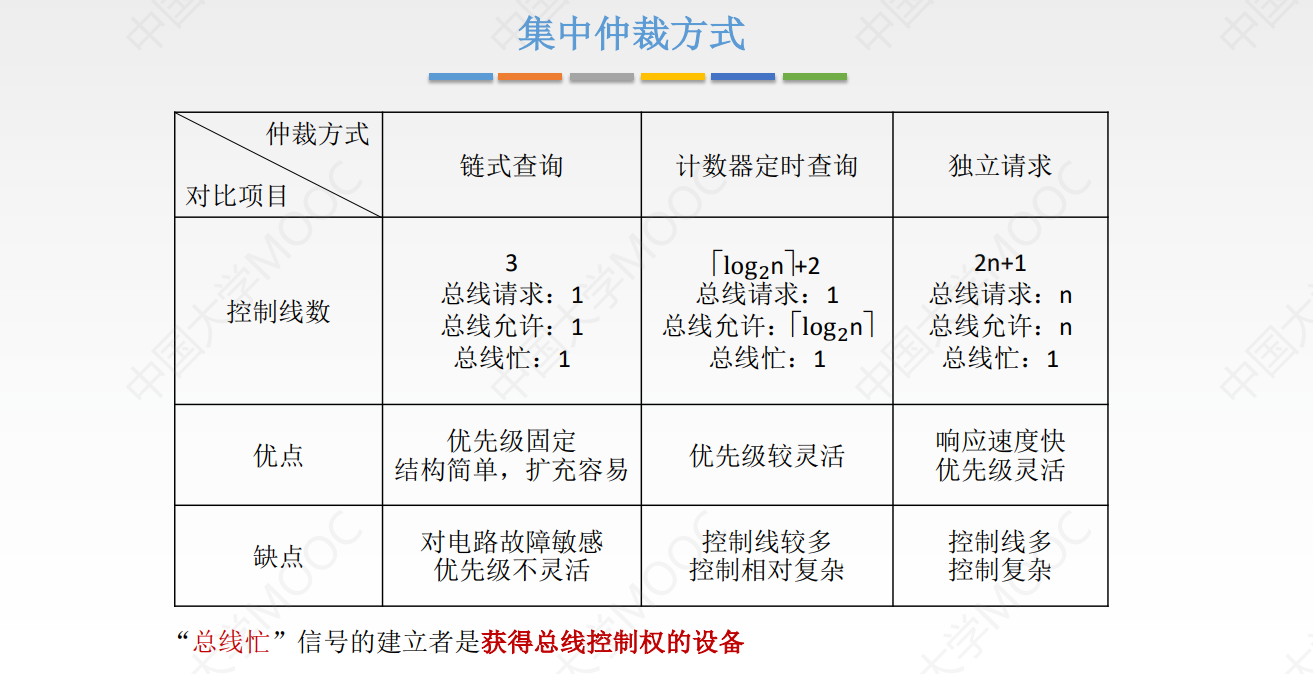

① 链式查询方法

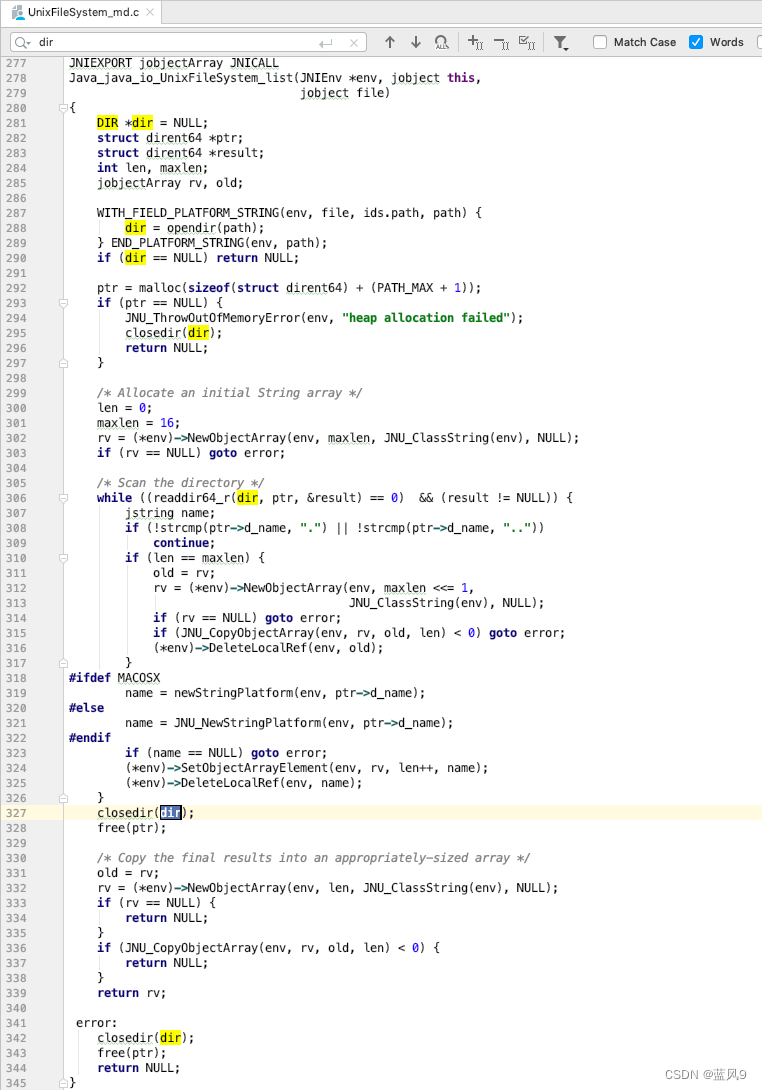

下图三条线用于总线控制,设备通过 BR总线请求线 发出总线占用请求;

如果每个设备占用总线,就使用 BS=1总线忙 进行声明;BG是总线授权线;

其中总线同意信号BG是串行连接一个个I/O接口(逐个),当遇到接口有总线请求,就不继续往下传了。

特点:

- 结构简单易实现,易扩充设备;

- 串行导致对电路故障敏感,并且 优先级低(离控制部件远)的部件很难获得请求 ;

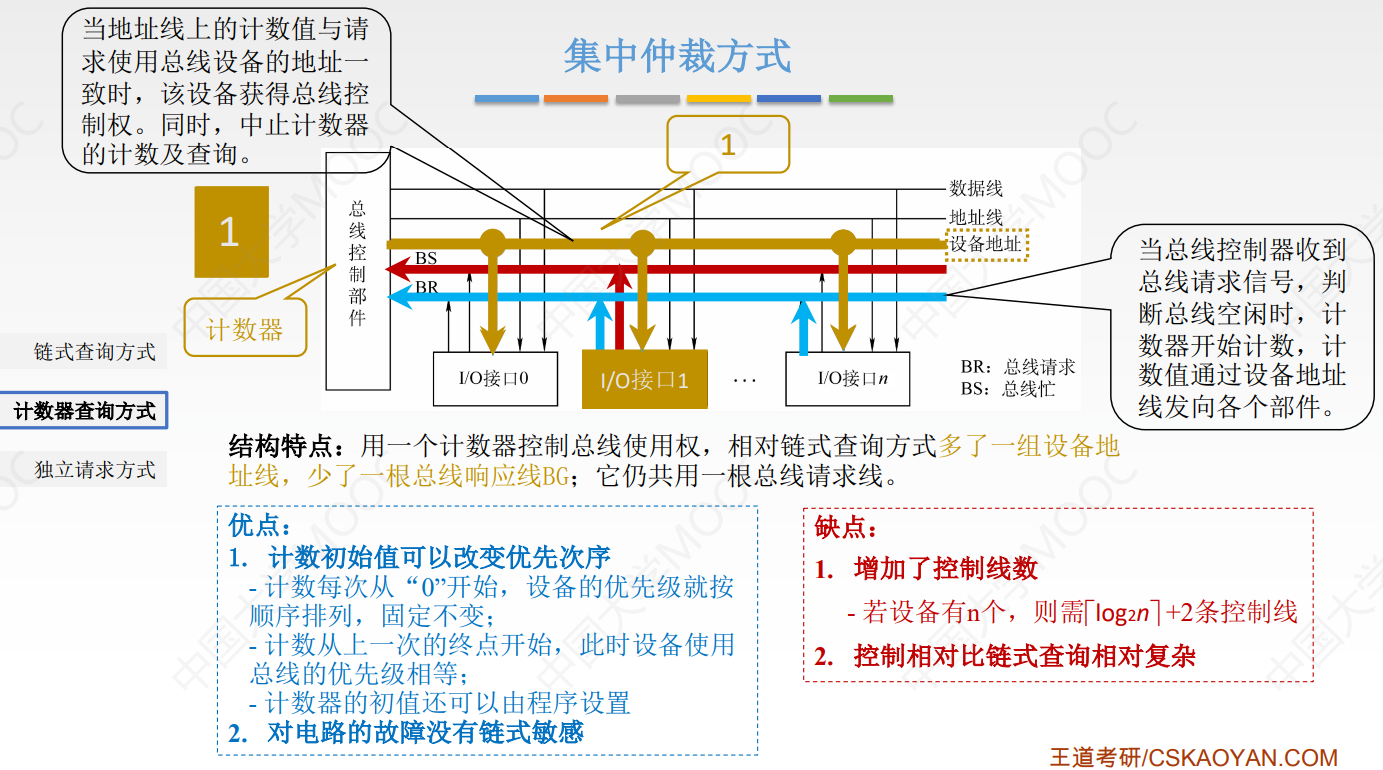

② 计数器定时查询方式

与 链式查询方法 相比,多了设备地址线,少了总线同意线BG;

设备地址线上传输的地址是计数器给出的,通过这个地址来查找某个设备是否发出占用请求;

特点:设备优先级设置灵活,对电路问题不敏感了;但增加了设备地址线,控制变复杂了;

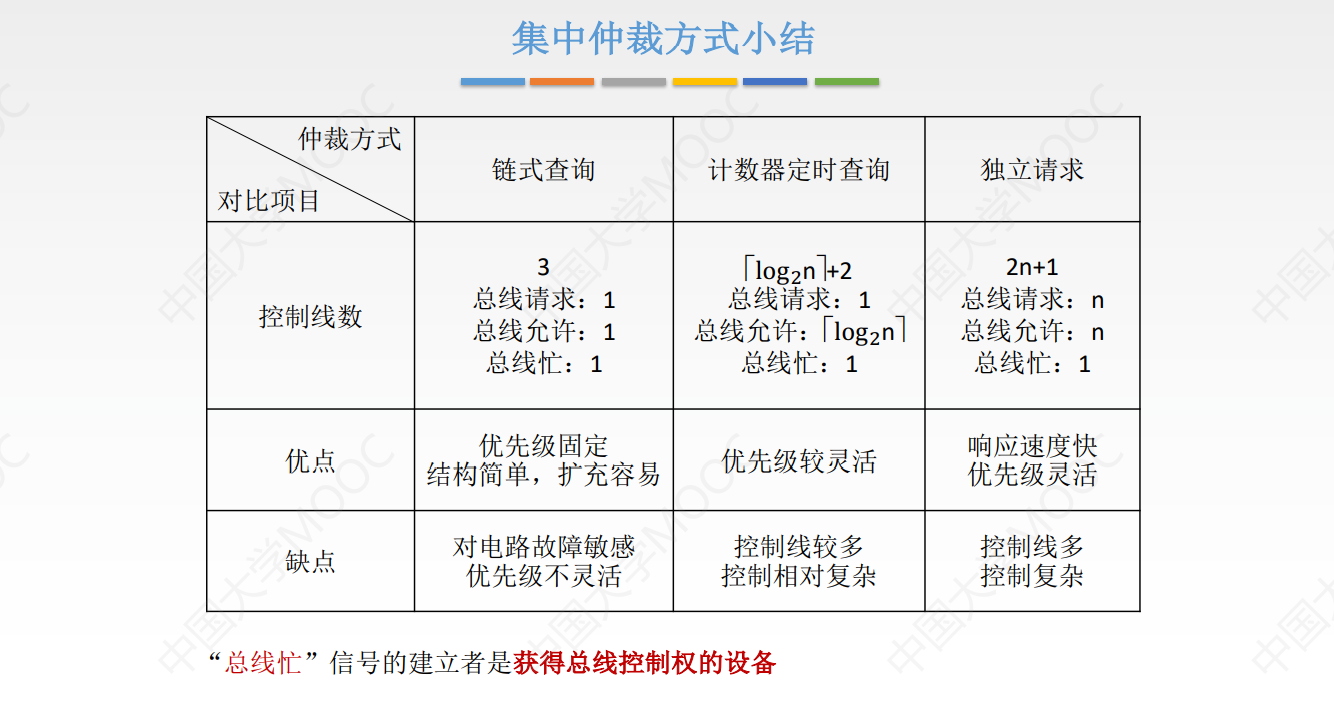

③ 独立请求方式

每个设备均有一对 总线请求线BRi 和 总线同意线BGi ;

总线控制部件有一排队电路,可以根据优先级确定响应那一台设备的请求;

特点:响应速度快,优先次序控制灵活。但控制线数量多,总线控制复杂;

三种集中控制方式小结

链式查询仅使用 两根线 确定总线使用权属于哪个设备;

计数器查询使用 log2n 根线;

独立请求方式使用 2n 根线;

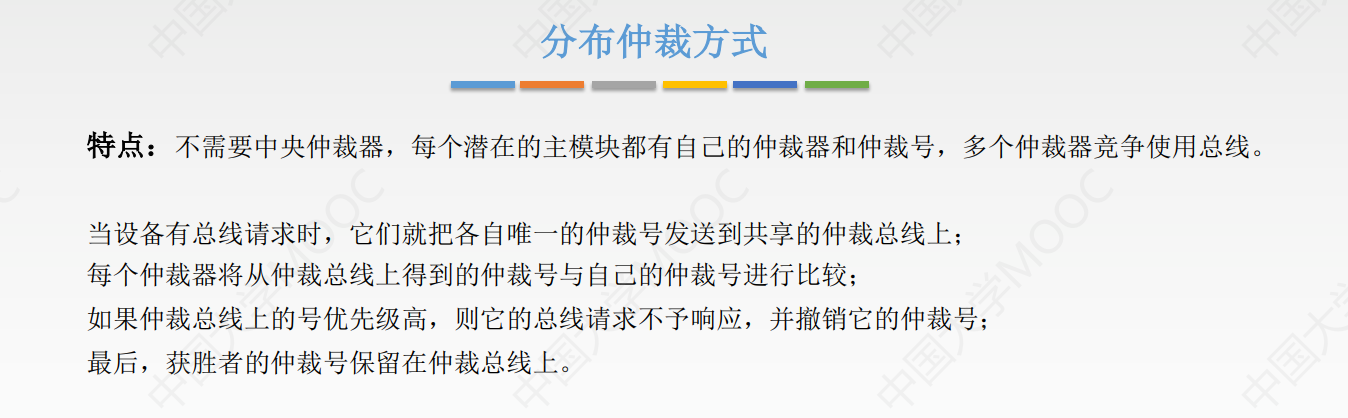

3. 分布仲裁方式

小结

6.3 总线通信控制

1. 总线通信控制的目的

解决通信双方 协调配合 问题;

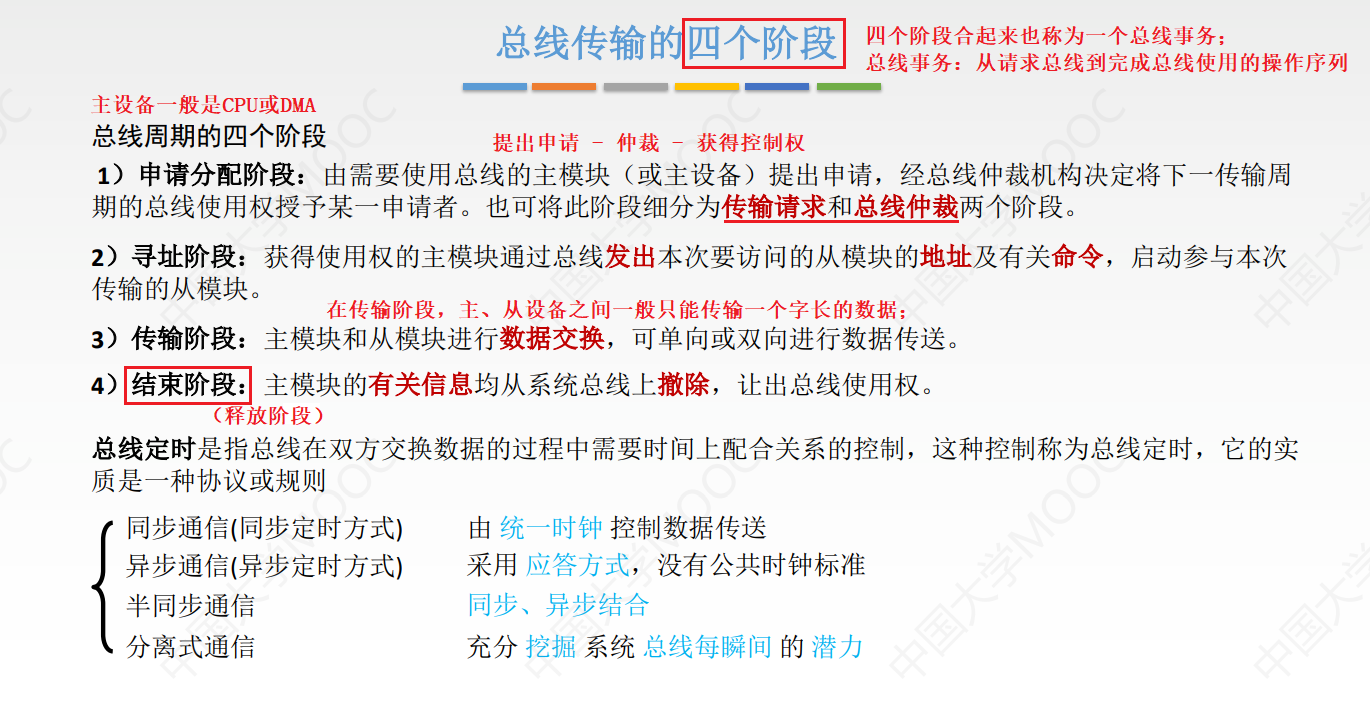

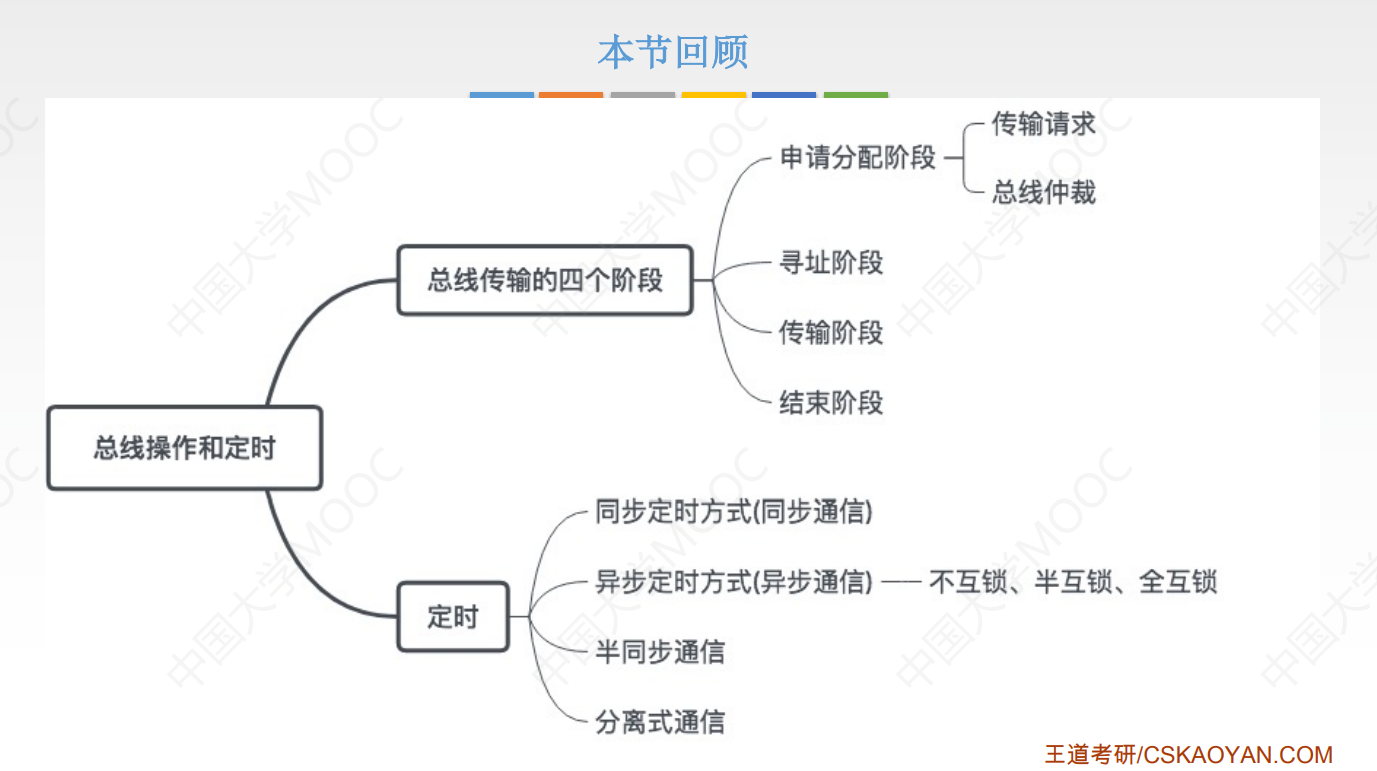

2. 总线传输周期 (总线事务)

总线传输周期是指 主设备与从设备完成一个完整可靠的通讯(总线操作)使用的时间 ,分成四个阶段;

【补充】

突发 (猝发) 传送方式 能够进行连续成组数据的传送,

其 寻址阶段 发送的是连续数据单元的首地址,在 传输阶段 传送多个连续单元的数据,每个时钟周期可以传送一个字长的信息 ,但是不释放总线,直到一组数据全部传送完毕后,再释放总线。

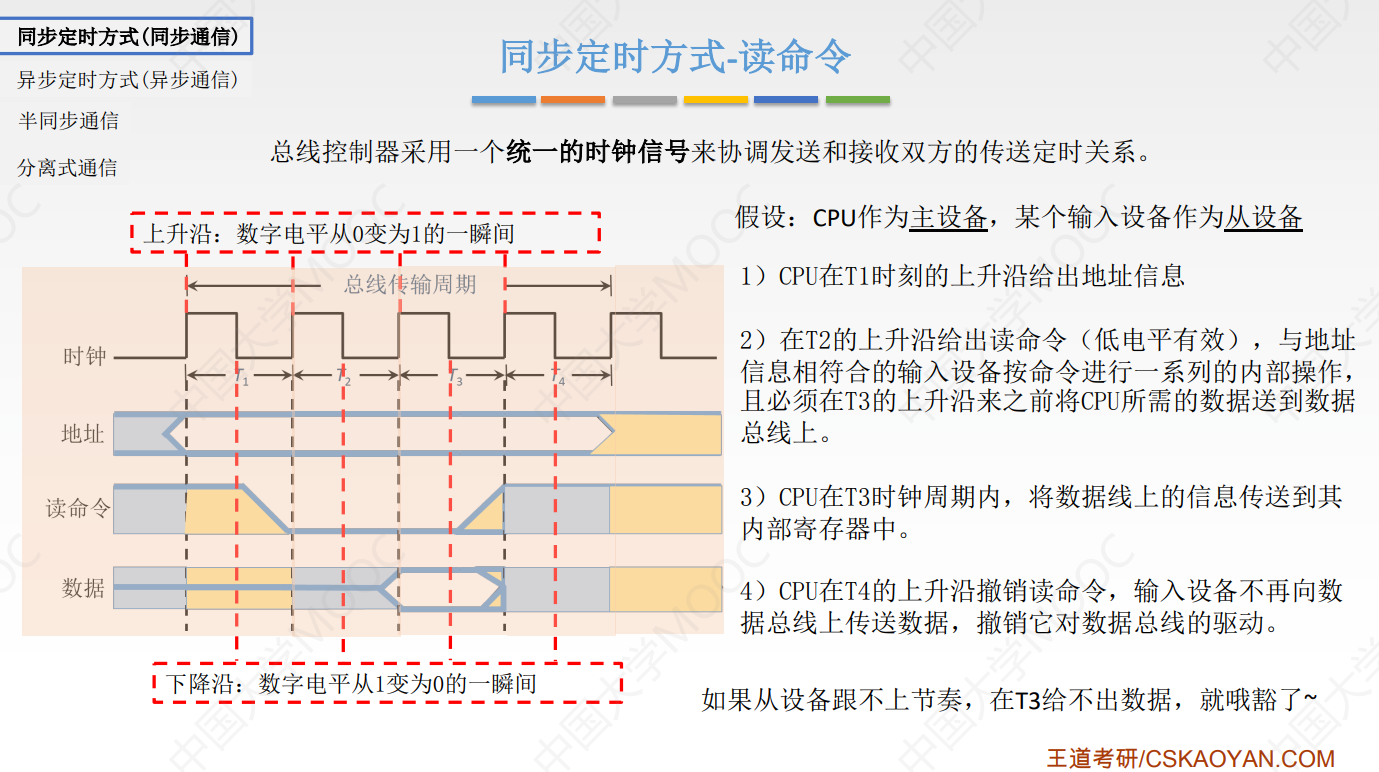

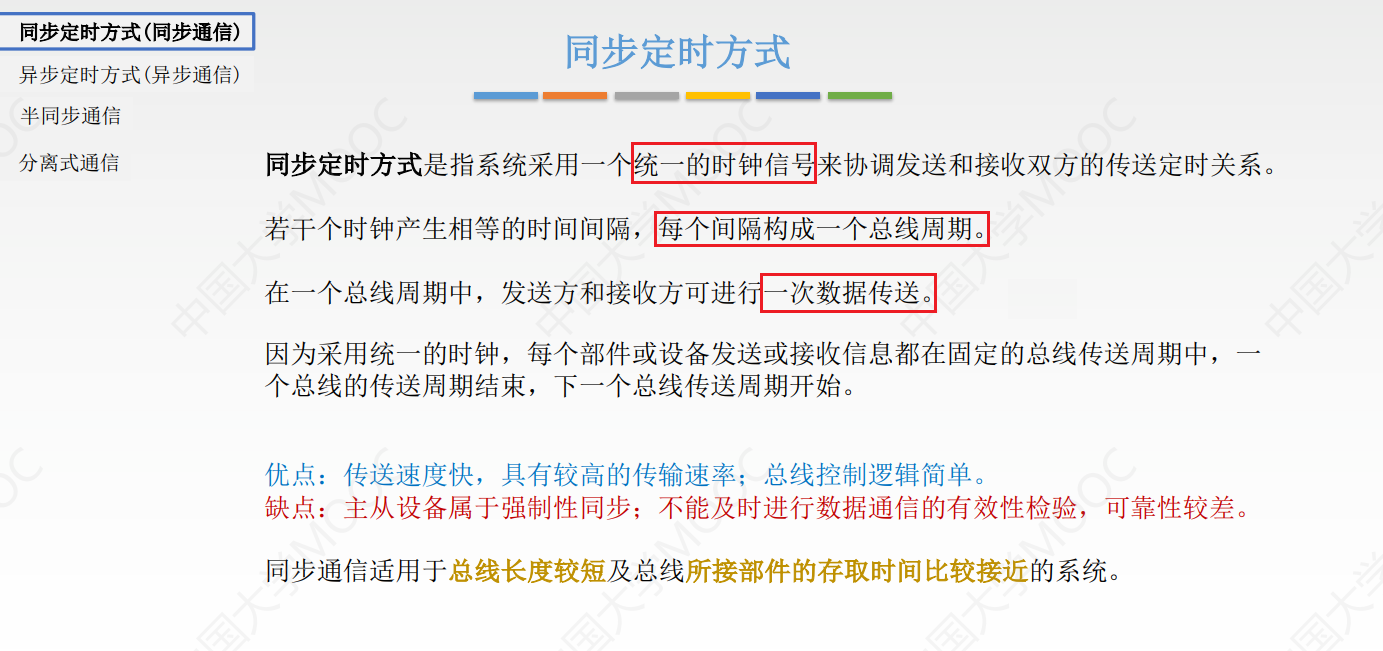

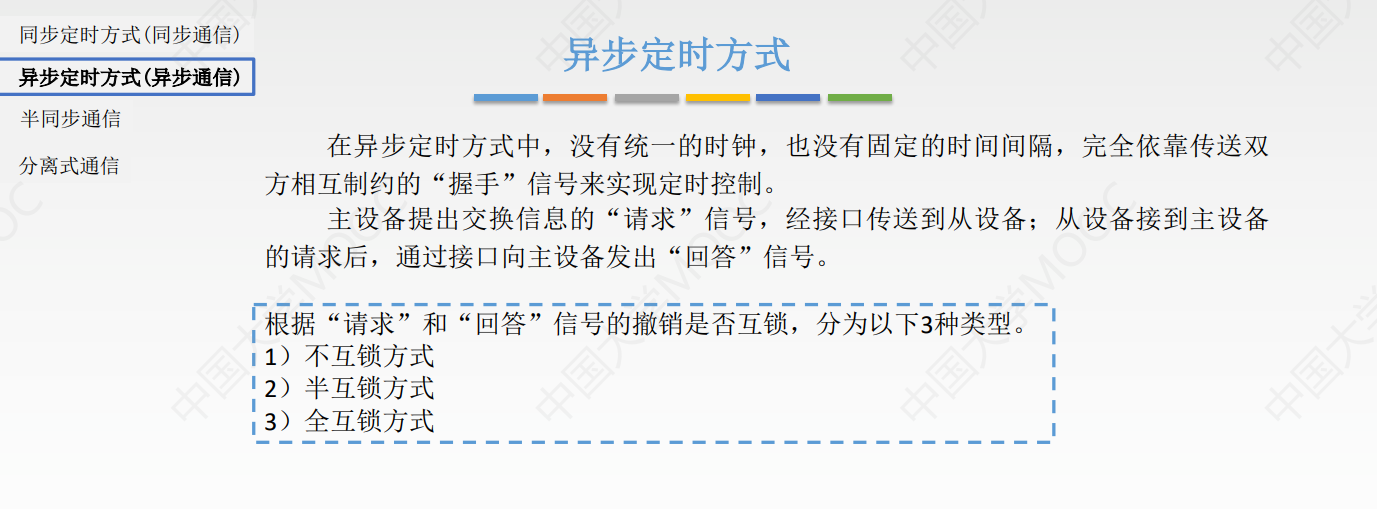

3. 总线通信 (总线定时) 的四种方式

① 同步定时方式 (同步通信)

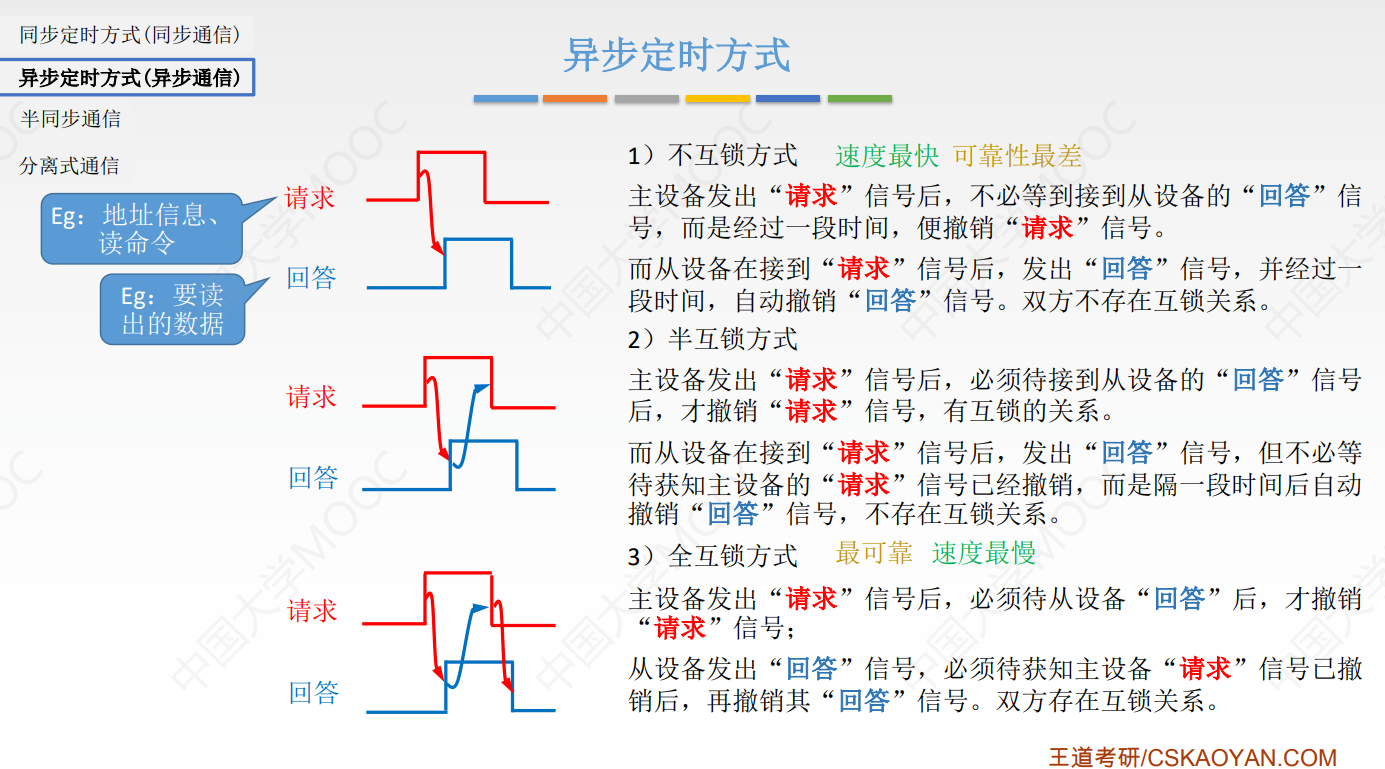

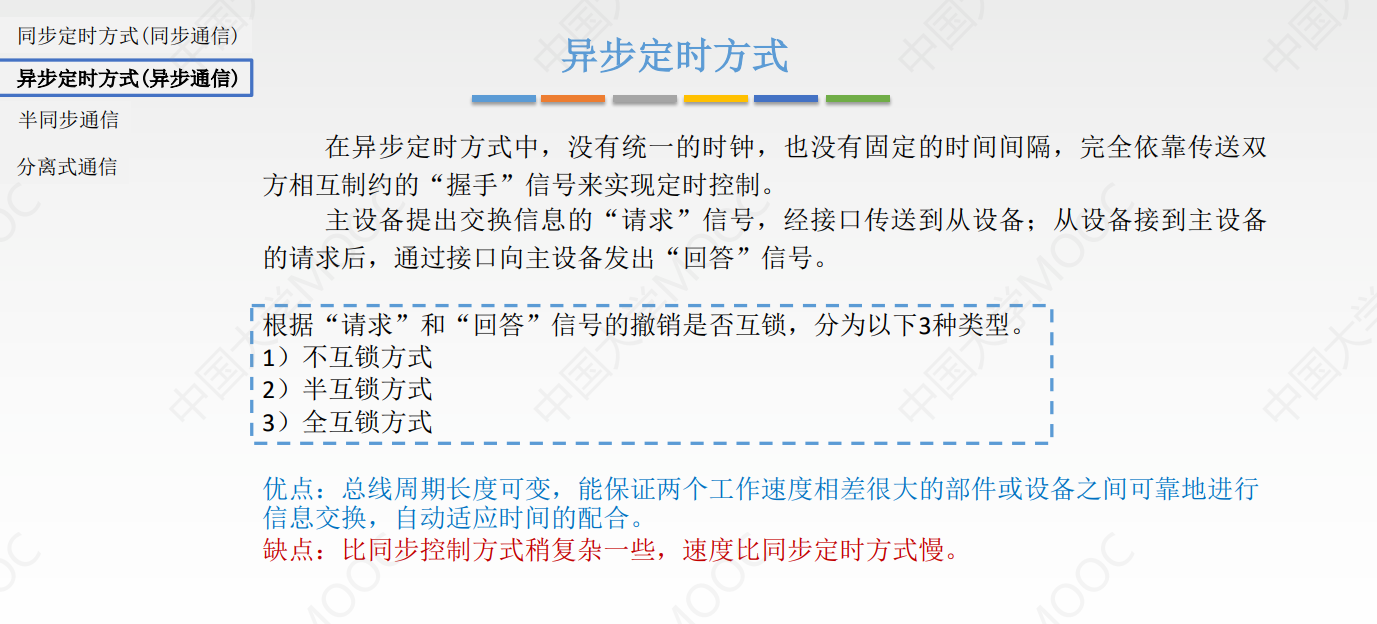

② 异步定时方式 (异步通信)

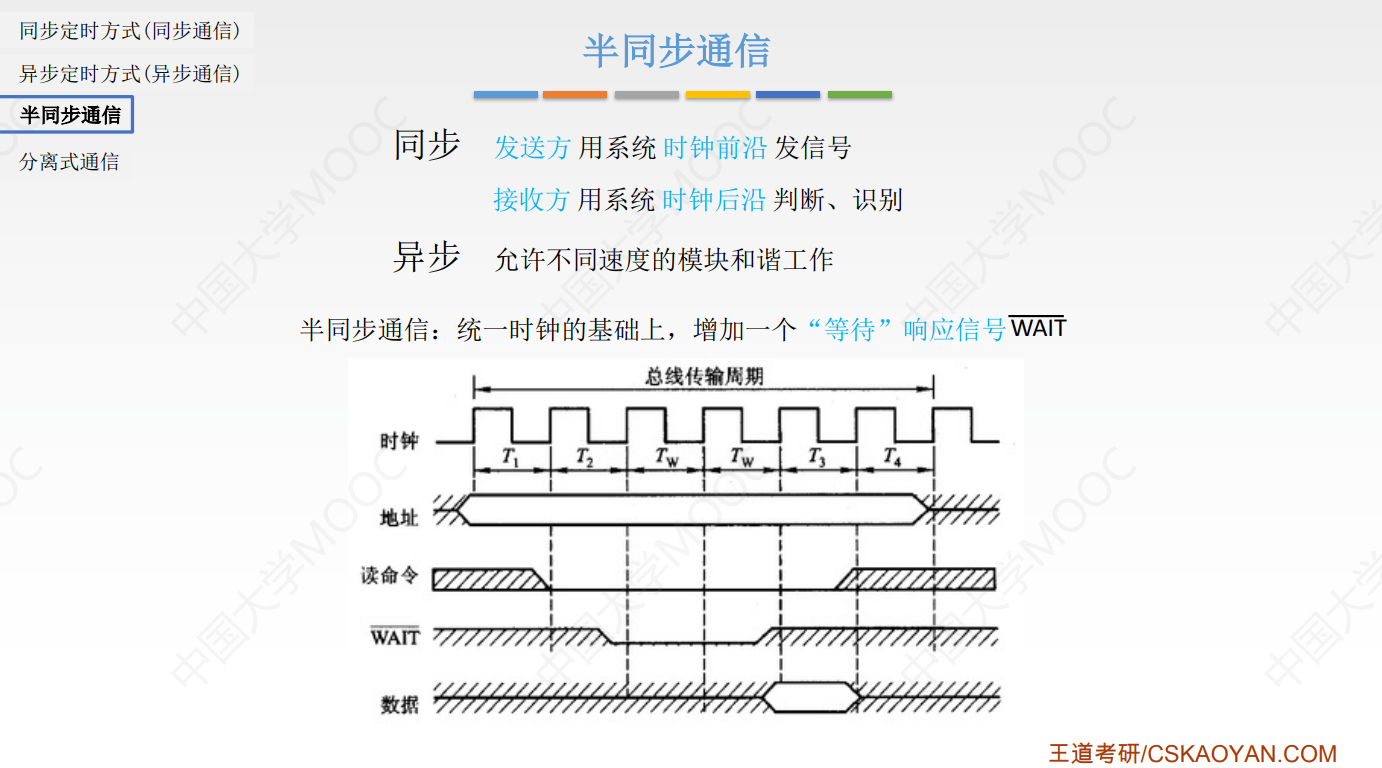

③ 半同步通信

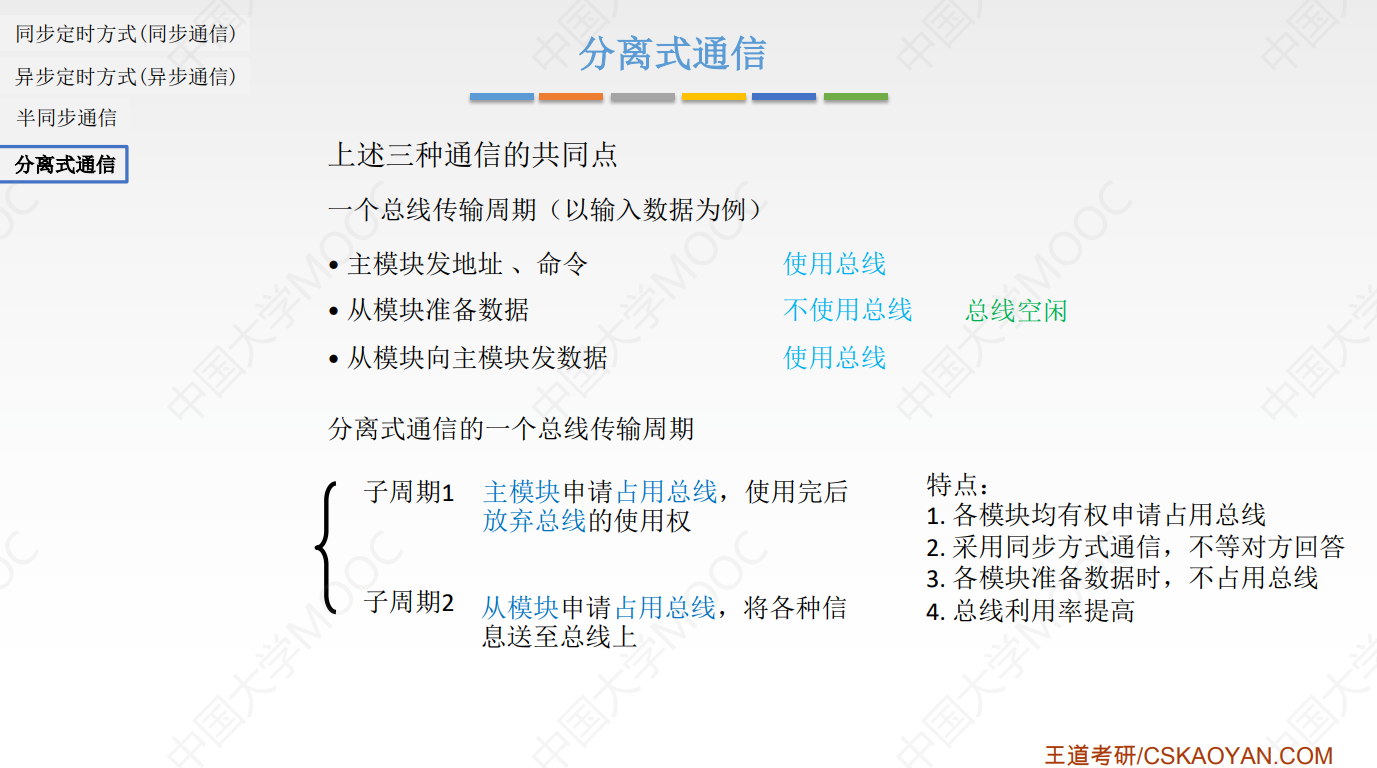

④ 分离式通信

小结

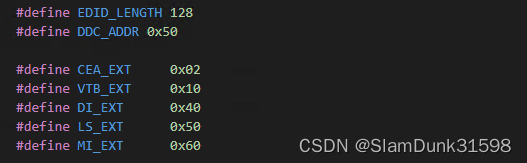

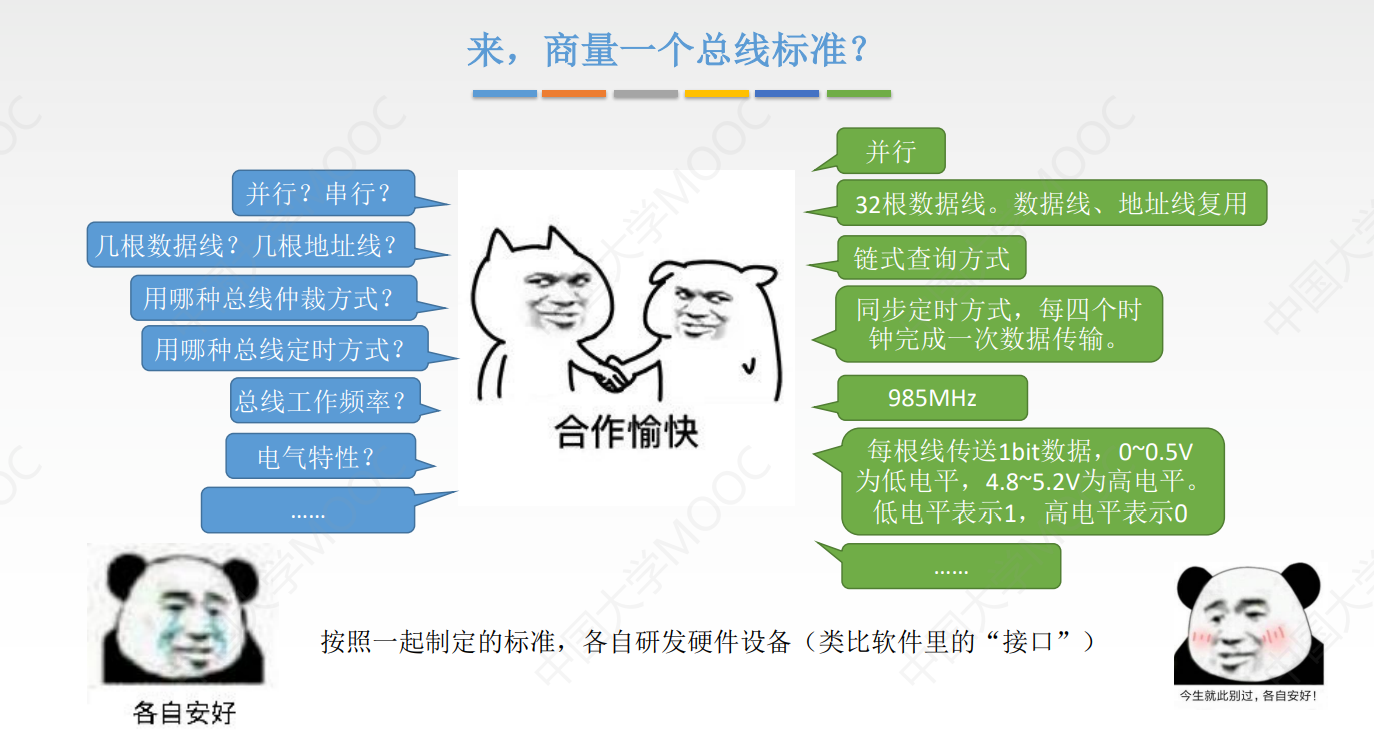

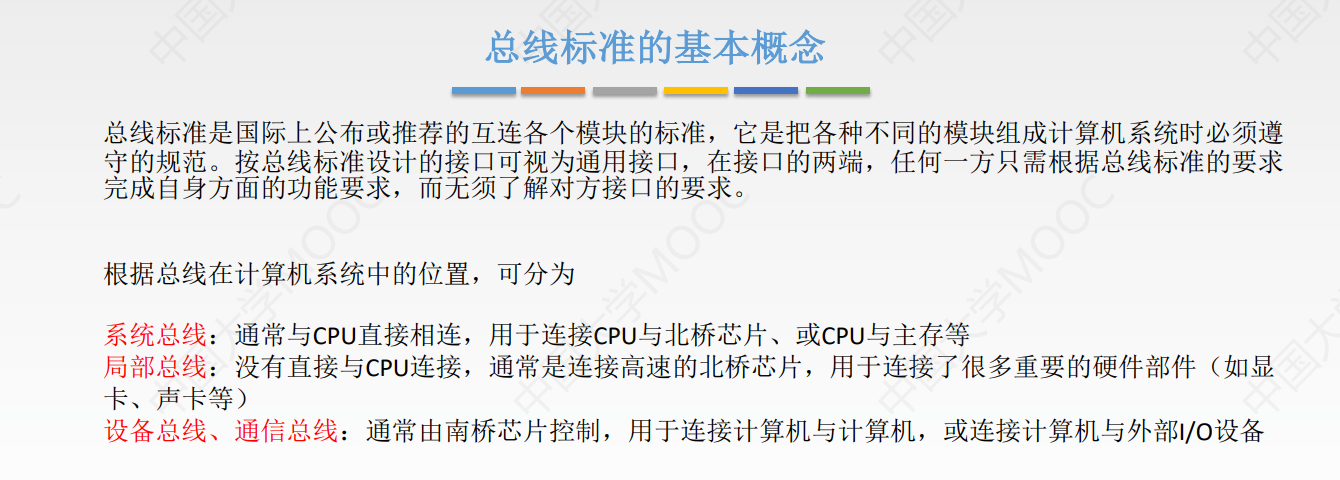

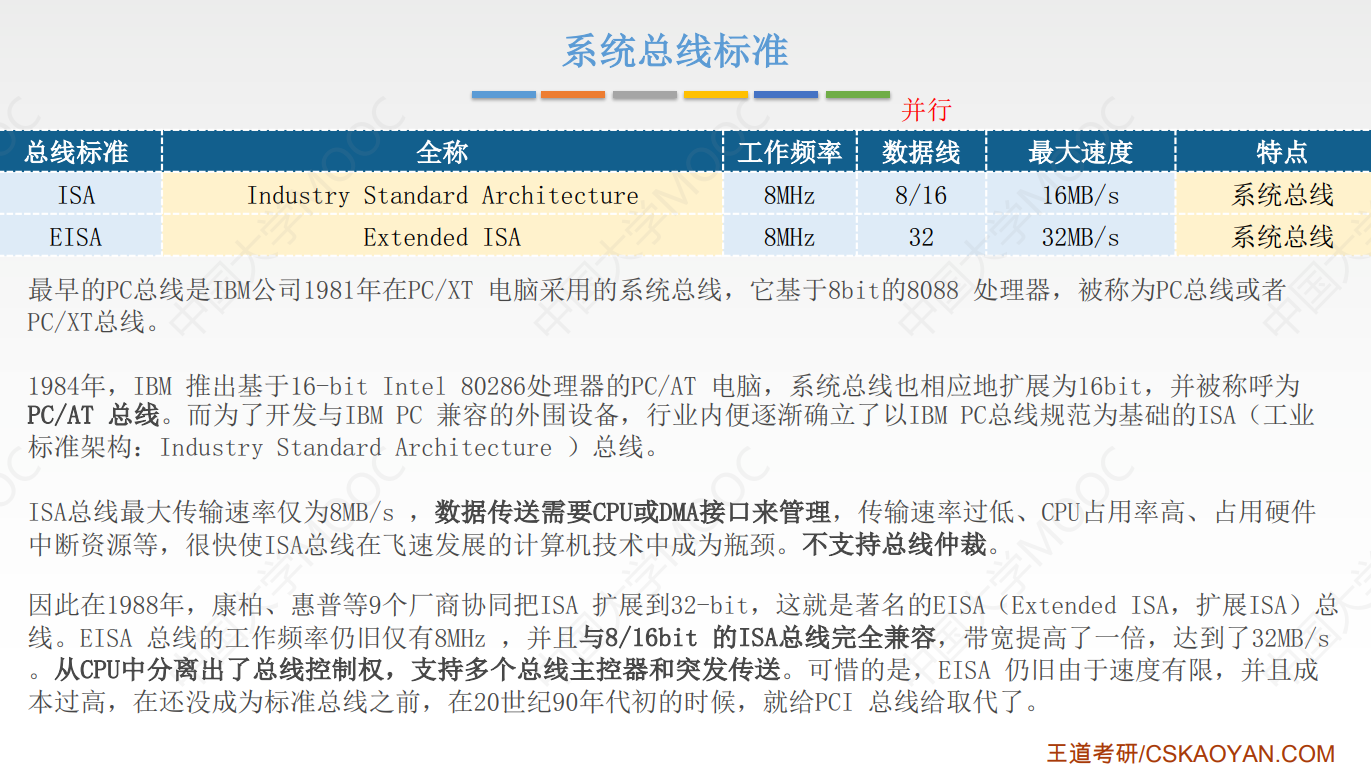

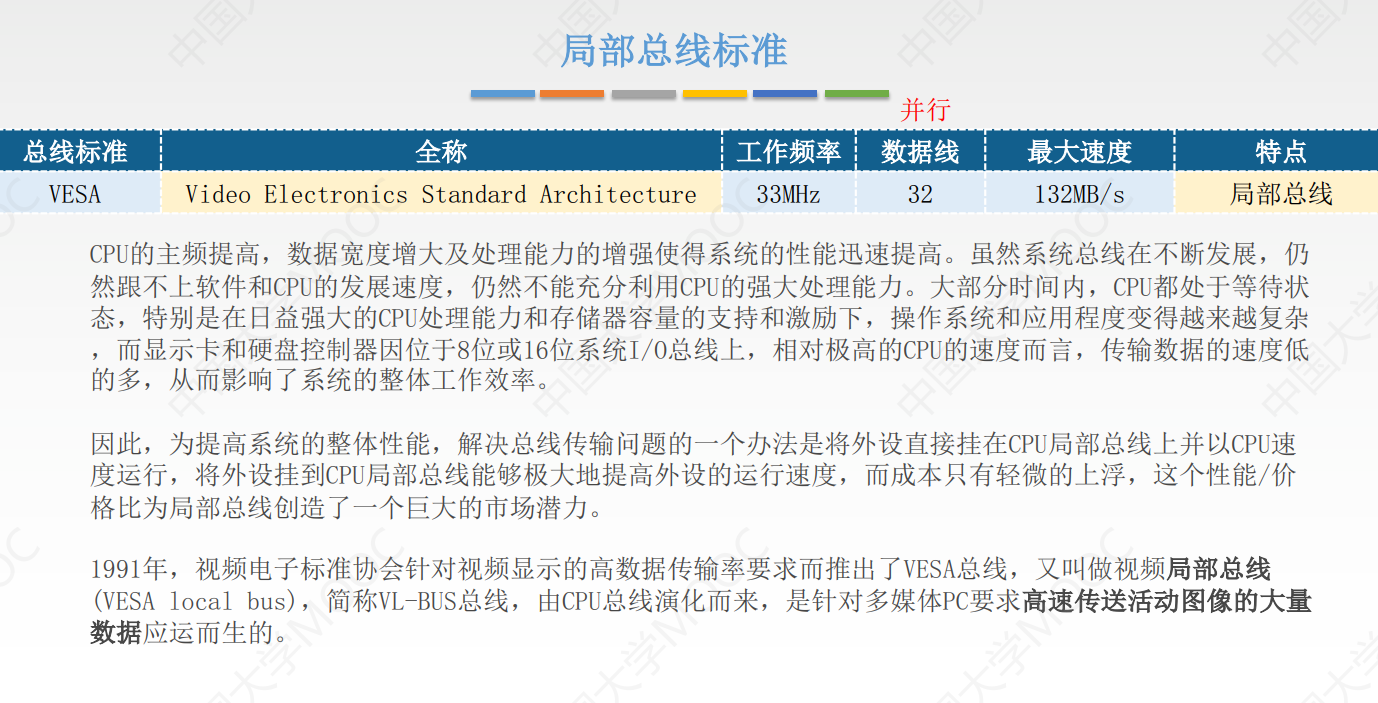

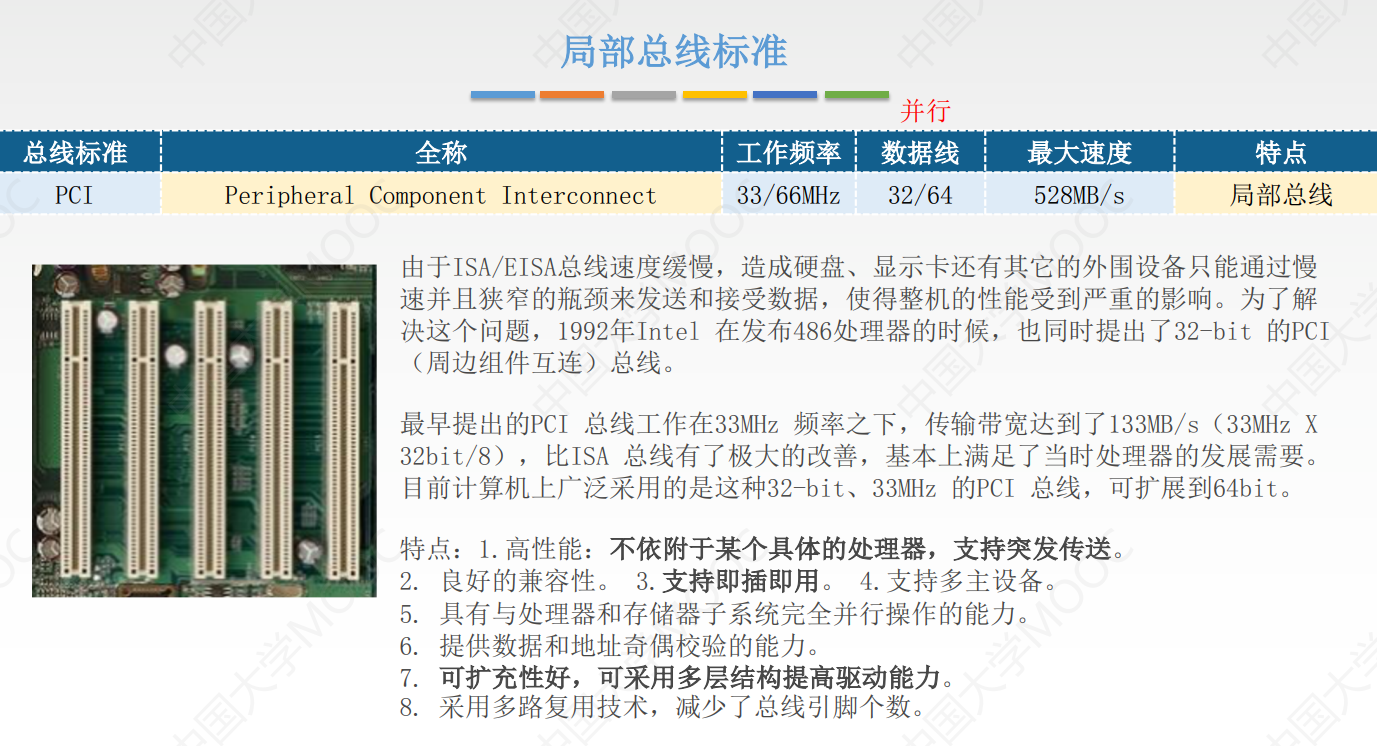

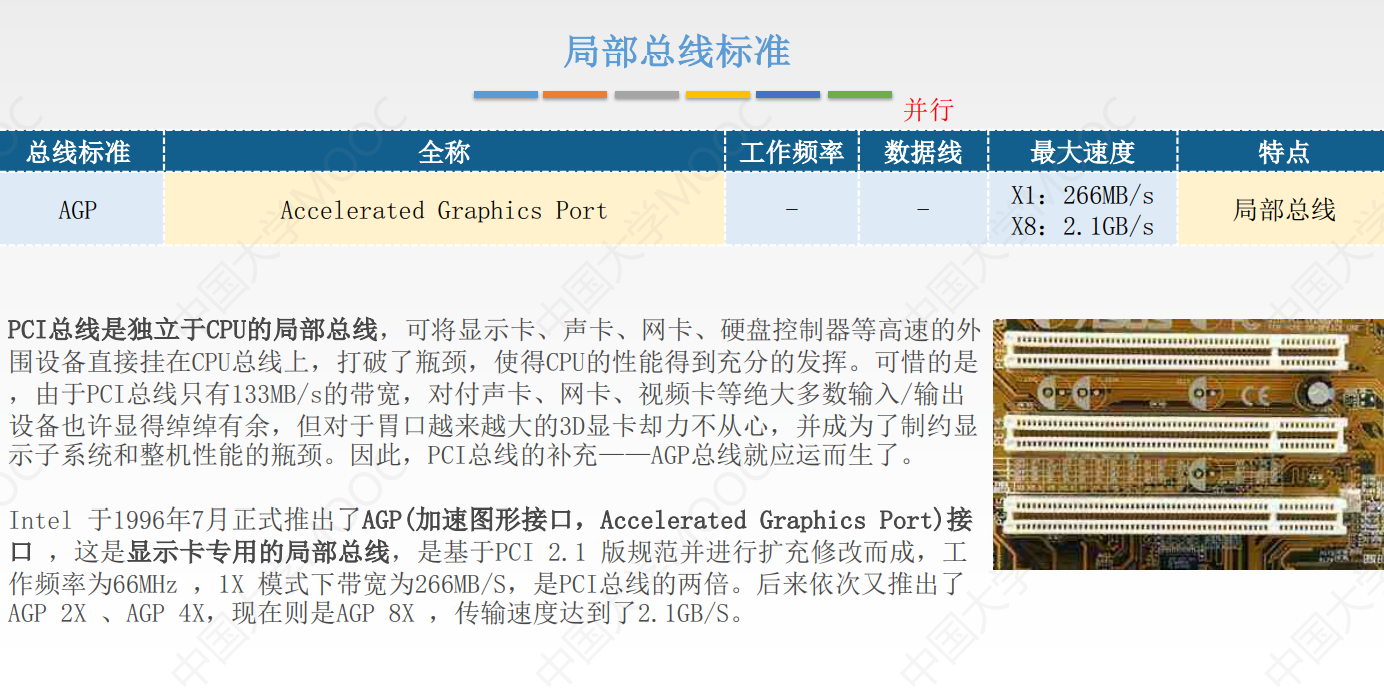

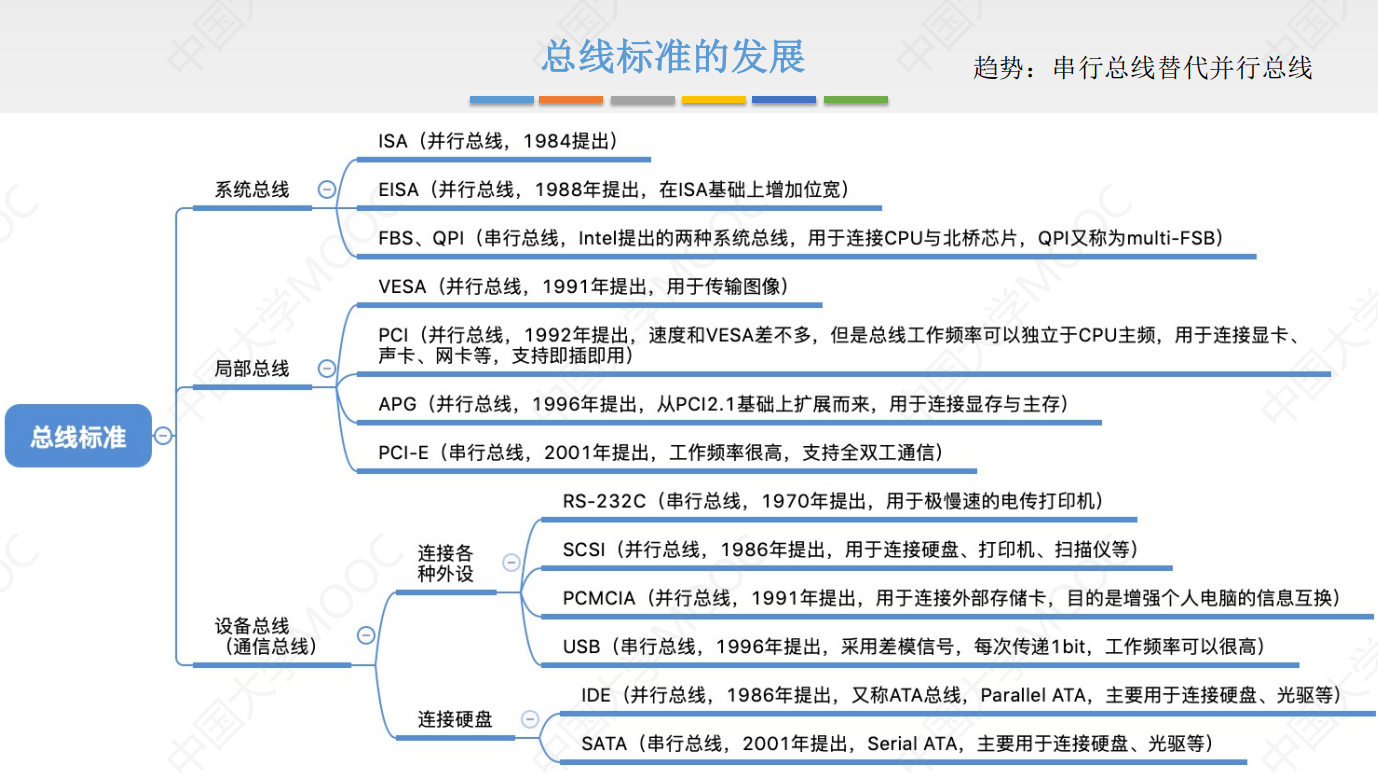

6.4 总线标准 *

1. 总线标准的基本概念

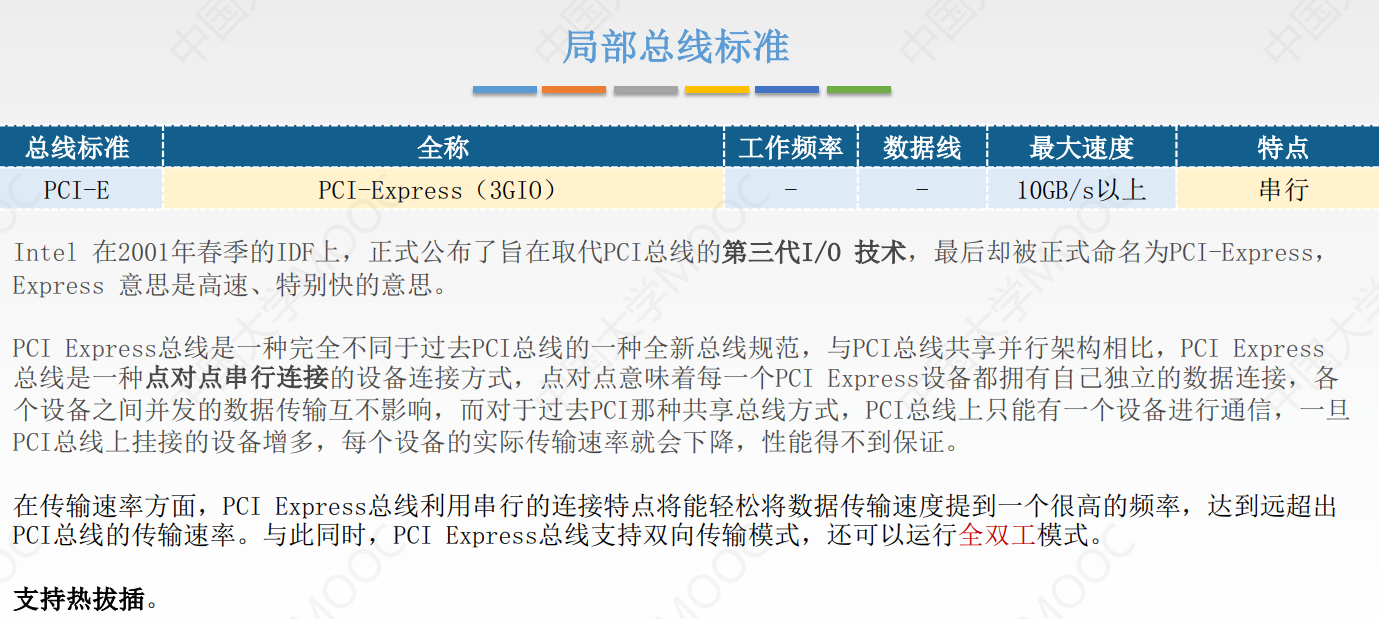

2. 局部总线标准

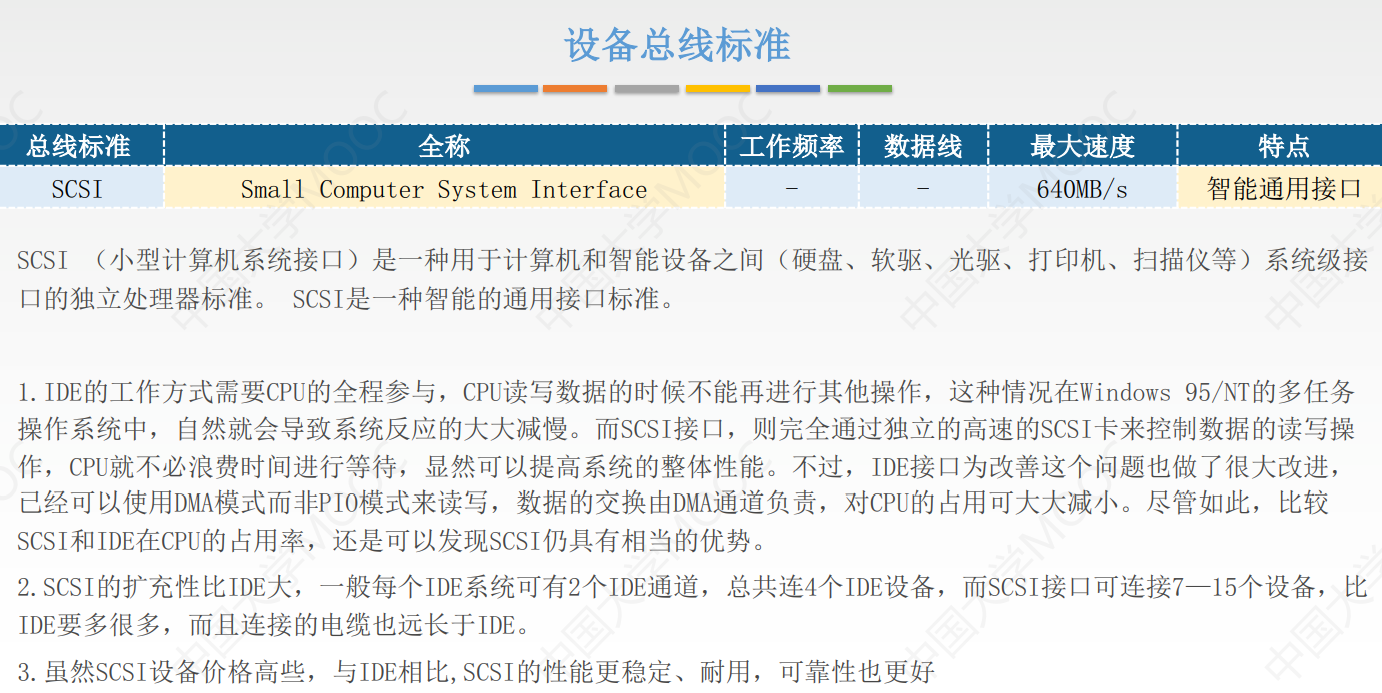

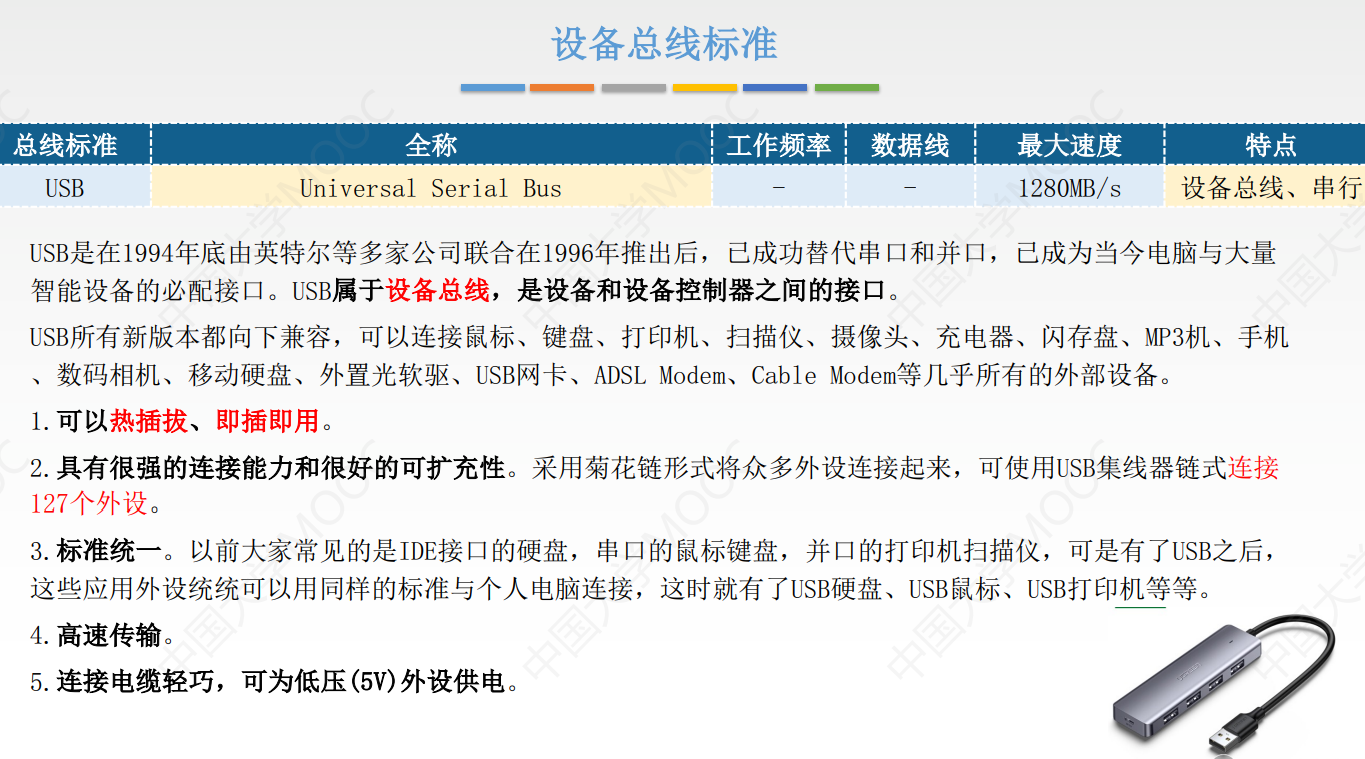

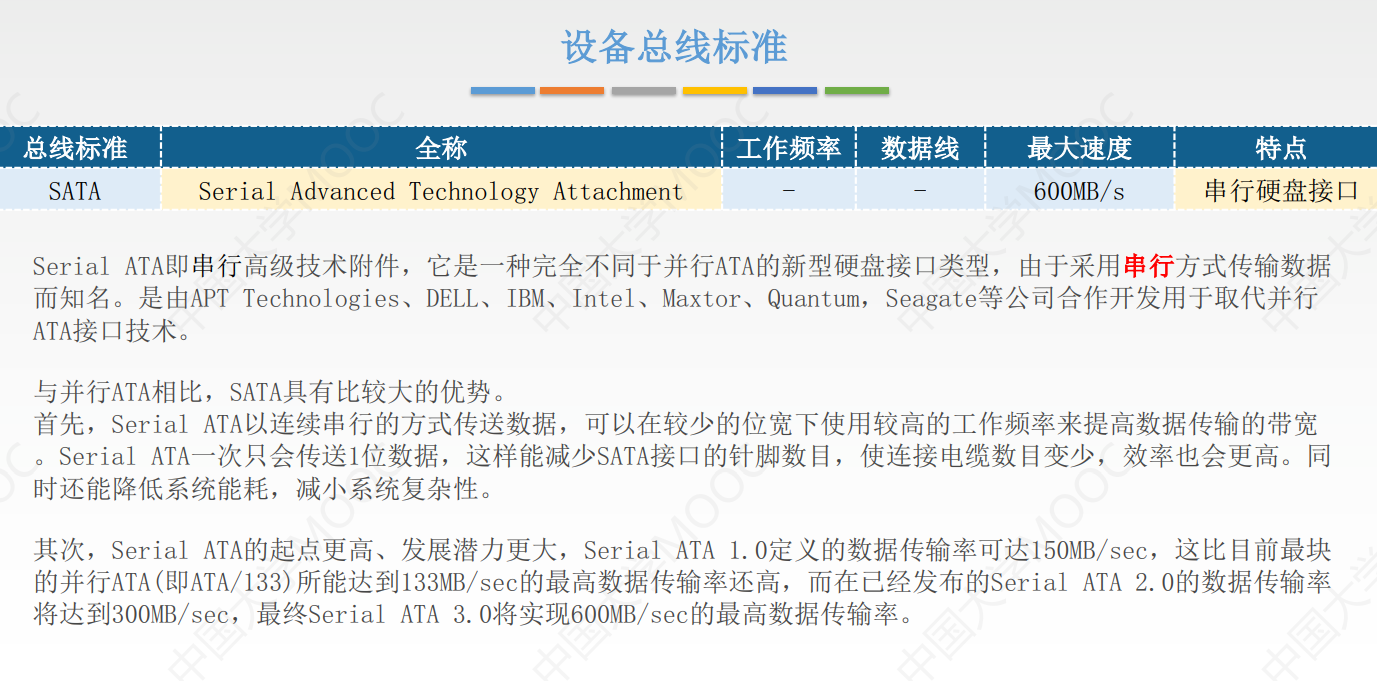

3. 设备总线标准

小结

6.5 常见问题和易混淆点

1. 同一个总线不能既采用同步方式又采用异步方式通信吗?

半同步通信总线可以;

这类总线既保留了同步通信的特点,又能采用异步应答方式连接速度相差较大的设备;

通过在异步总线中引入时钟信号,其就绪和应答等信号都在时钟的上升沿或下降沿有效,而不受其他时间的信号干扰;

例如,某个采用半同步方式的总线总是从某个时钟开始,在每个时钟到来时,采样Wait信号,若无效,则说明数据未准备好,下个时钟到来时,再采样Wait信号,直到检测到有效,再去数据线上取数据;PCI总线也是一种半同步总线,它的所有事件都在时钟下降沿同步,总线设备在时钟开始的上升沿采样总线信号;

2. 一个总线在某一时刻可以有多对主从设备进行通信吗?

不可以

在某个总线周期内,总线上只有一个主设备控制总线,选择一个从设备与之进行通信(即一对一的关系),或对所有设备进行广播通信(即一对多的关系);

所以一个总线在某一时刻不能有多对主从设备进行通信,否则会发生数据冲突;

1) 引入总线结构有什么好处 ?

答:引入总线结构主要有以下优点:

① 简化了系统结构,便于系统设计制造;

② 大大减少了连线数目,便于布线,减小体积,提高系统的可靠性;

③ 便于接口设计,所有与总线连接的设备均采用类似的接口;

④ 便于系统的扩充、更新与灵活配置,易于实现系统的模块化;

⑤ 便于设备的软件设计,所有接口的软件对不同的接口地址进行操作;

⑥ 便于故障诊断和维修,同时也能降低成本;

2) 引入总线结构会导致什么问题 ?如何解决 ?

答:

引入总线后,总线上的各个设备分时共享同一总线,当总线上多个设备同时要求使用总线时就会导致总线的冲突;

为解决多个主设备同时竞争总线控制权的问题,应当采用总线仲裁部件,以某种方式选择一个主设备优先获得总线控制权,只有获得了总线控制权的设备才能开始数据传送;