1、逻辑电路:组合逻辑单路、时序逻辑电路。根据电路是否有存储功能判断。

2、组合逻辑电路

指该电路在任一时刻的输出,仅取决于该时刻的输入信号,而与输入信号作用前电路的状态无关。一般由门电路组成,不含记忆元器件,输入与输出之间无反馈。

常见的组合逻辑电路有译码器和多路选择器等。

真值表

对于有n个输入的逻辑电路,对应的真值表有2^n种输入组合,每一种输入组合表示一组输入状态集,分别对应一个确定的输出。

真值表能够完全描述任何一种组合逻辑函数,但是表的大小随着输入个数的增加呈指数增长,而且不过清晰。

布尔代数:3中典型的操作符:OR、AND和NOT。

门电路:与门、或门和非门。

通常在信号的输入或输出端加入一个“。”表示对输入/输出信号取非。常见的两种反向门电路为NOR和NAND,它们分别对应或门、与门的取非。NOR和NAND的门电路称为全能门电路,因为任何一种逻辑函数都可以用这种门电路得以实现。

译码器(解码器)

译码器是一种多输入多输出的组合逻辑电路。与译码器对应的是编码器,它实现的是译码器的逆变功能。

数据选择器(多路开关)和数据分配器(多路分配器)

数据选择器是以“与或”门或“与或非”门为主的电路。它可以在选择信号的作用下,从多个输入通道中选择某一个通道的数据作为输出。常见的数据选择器有二选一、四选一、八选一、十六选一。

数据选择器除了选择输入信号,还可实现任意组合逻辑函数。2n个数据输入的多路开关可实现n+1个变量的逻辑函数。

数据分配器有一个输入端和多个输出端,将一个输入端的信号送至多个输出端中的某一个,简称DMUX,作用与MUX正好相反。

3、时序逻辑电路

指电路任一时刻的输出不仅与该时刻的输入有关,而且还与该时刻电路的状态有关。因此,时序逻辑电路中必须包含记忆元器件。

常见的时序逻辑电路有寄存器和计数器等。

时钟信号:决定逻辑单元中的状态何时更新。

触发器:电位触发、边沿触发、主-从触发等方式。

电位触发:常用它组成暂存器。

当触发器的同步控制信号E为约定电平时,触发器接收输入数据,此时输入数据D的任何变化都会在输出Q端得到反映;

当触发器的同步控制信号E为非约定电平时,触发器状态保持不变。

边沿触发:常用的正边沿触发器是D触发器。

时钟脉冲CP的某一约定跳变到来时,触发器接收输入数据。

在时钟脉冲CP=1和CP=0期间以及非CP约定跳变到来时,触发器不接受数据。

寄存器与移位器

寄存器用来接收信息、寄存信息或传送信息,通常采用并行输入-并行输出的方式。

由于一个触发器仅能寄存一位二进制代码,所以要寄存n位进制代码,就需要具备n个触发器。

正边沿触发器-D触发器:寄存器的各位在同一时刻(CP上身沿)接收信息。

锁存器:寄存器通过高电平触发接收信息。作用是把一些短暂的信号锁存起来,以达到时间上的扩展。

移位寄存器的工作方式:串行输入-串行输出、串行输入-并行输出、并行输入-串行输出。

4、数字集成电路:双极型集成电路、金属氧化物半导体(MOS)集成电路。根据开关元件不同判断。

5、双极型集成电路

采用晶体管作为开关元件,管内参与导电的有电子和空穴两种极性的载流子。

常见双极型集成电路:

晶体管-晶体管逻辑电路(TTL)、二极管-三极管逻辑电路(DTL)、高阈值逻辑电路(HTL)、发射机耦合逻辑电路(ECL)、集成注入逻辑电路(IL)等。

ECL电路中的三极管工作在非饱和状态,工作速度快、输出阻抗低、带负载能力强、电路内部开关噪声低、使用方便灵活等。缺点是噪声容限低、电路功耗大、输出电平的稳定性较差。

目前ECL电路主要用于高速、超高速数字系统。

6、金属氧化物半导体(MOS,单极型集成电路)

采用绝缘栅极效应晶体管作为开关元件,管内参与导电的只有电子或空穴极性的载流子。

PMOS管集成电路:问世较早,速度低,现已很少使用。

NMOS管集成电路:工作速度稍高,且直流电源电压较低,现仍在使用。

CMOS(由PMOS管和NMOS管构成的互补MOS集成电路):静态功耗极低,工作速度较高,抗干扰能力强,广泛使用。

7、可编程逻辑器件

现场可编程逻辑器件(FPLD)、现场可编程门阵列(FPGA)、复杂可编程逻辑器件(CPLD)。

8、嵌入式微处理器

冯诺依曼结构:地址和数据共用。

哈佛结构:地址和数据不共用。

ARM采用哈佛结构,是一种RISC体系结构的微处理器。

DSP(数字信号处理技术)采用哈佛结构,具有专门的硬件乘法器,广泛采用流水线操作,提供特殊的指令,可以用来快速地实现各种数字信号处理算法。

9、微处理器的异常:中断、陷阱、故障、中止

| 类别 | 原因 | 异步/同步 | 返回行为 |

| 中断 | 来自I/O设备的信号 | 异步 | 总是返回到下一条指令 |

| 陷阱 | 有意的异常 | 同步 | 总是返回到下一条指令 |

| 故障 | 潜在可恢复的错误 | 同步 | 可能返回到当前指令 |

| 中止 | 不可恢复的错误 | 同步 | 不会返回 |

陷阱:有意的异常,是执行一条指令的结果。用途是用户程序与内核之间提供接口,称为系统调用。

10、中断

硬中断由硬件产生,例如磁盘、网卡、键盘、时钟等。每个设备或设备集都有自己的IRQ(中断请求)。

软中断是一组静态定义的下半部分接口,可以在所有的处理器上同时执行,即使两个类型相同也可以。但是一个软中断不会抢占另一个软中断,唯一可以抢占软中断的是硬中断。

可屏蔽中断和不可屏蔽中断都属于外部中断,是由外部中断源引起的。

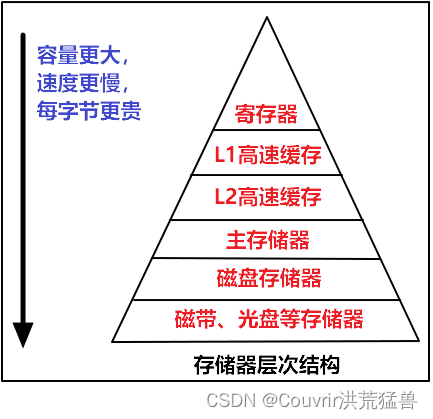

11、存储器层次结构

Cache-主存可构成Cache存储系统,主存-磁盘可构成虚拟存储系统。

内存管理单元(MMU)

操作系统常用MMU隔离系统内核与应用程序以及应用程序与应用程序。防止应用程序破坏操作系统和其它应用程序的代码和数据,防止应用程序对硬件的直接访问。

内存保护:防止地址越界、防止操作越权。