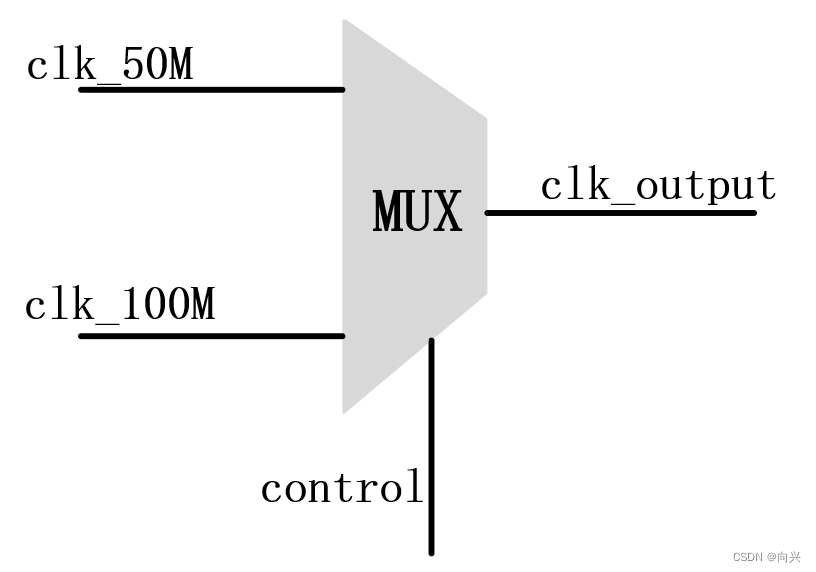

Verilog 实现无毛刺时钟切换电路,RTL代码设计+testbench代码测试,波形前仿真

news2026/2/14 13:43:17

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处:http://www.coloradmin.cn/o/31080.html

如若内容造成侵权/违法违规/事实不符,请联系多彩编程网进行投诉反馈,一经查实,立即删除!相关文章

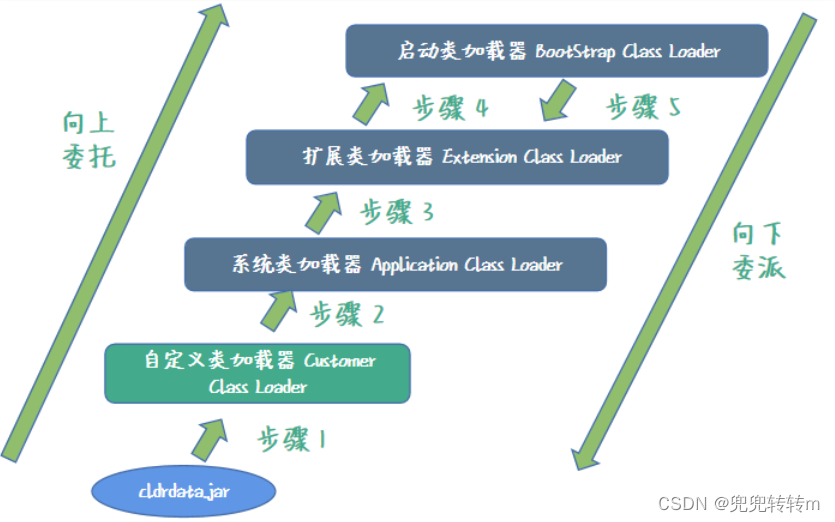

JVM 双亲委派模型

一言以蔽之,向上委托,向下委派。

向上委托:如果一个类加载器收到了类加载请求,它并不会自己先去加载,而是把这个请求委托给父类的加载器去执行,如果父类加载器还存在其父类加载器,则进一步向上…

家居建材如何在线管理订单?数商云采购系统实现订单发收货、退换货流程化管控

新时代的流程化业务,利用信息互通的时效性,提高员工执行力,提升市场竞争力,在悄无声息地促进企业发展。订单管理作为企业客户关系管理的有效延伸,能更好的把个性化、差异化服务有机的融入到客户管理中去,能…

220kV降压变电所电气部分初步设计33号

目录

1 绪论 5 1.1 概述 5 1.2 本次设计内容 5 1.3 本次设计任务 5 2 变电站总体分析 6 2.1变电所总体分析 6 2.2主变压器选择 7 3 电气主接线选择 10 3.1 电气主接线的概念 10 3.2 电气主接…

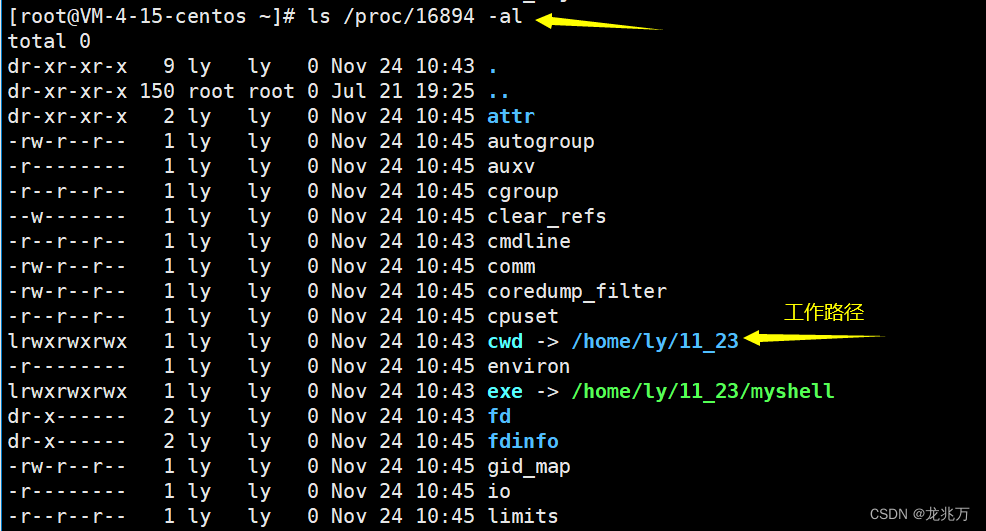

Linux —— 进程控制

1.进程控制的四个概念

进程控制分为四类,分别是:

进程创建进程终止进程等待进程替换

2.进程创建

2.1初识fork

fork的作用是通过拷贝当前进程创建一个子进程,这两个进程的区别在于PID不同(还有一些资源、统计量也不同,但PID是我…

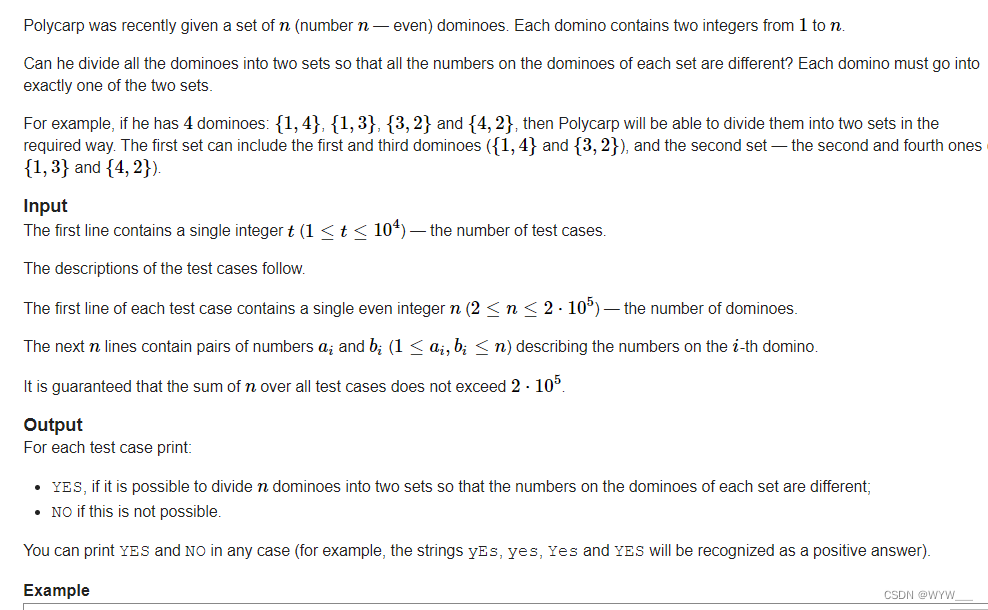

E. Split Into Two Sets(染色法判断二分图)

Problem - 1702E - Codeforces 波利卡普最近得到了一组n(数字n-偶数)的骨牌。每块多米诺骨牌包含1到n的两个整数。

他能把所有的骨牌分成两组,使每组骨牌上的数字都不一样吗?每张多米诺骨牌必须正好进入两组中的一组。

例如&…

7种主流数据分析软件比较及经典教材推荐

前言

STATA

软件优点:Stata以其简单易懂和功能强大受到初学者和高级用户的普遍欢迎。使用时可以每次只输入一个命令,也可以通过一个Stata程序一次输入多个命令。这样的话即使发生错误,也较容易找出并加以修改。尽管Stata的数据管理能力没有…

智慧点餐系统源码 扫码点餐小程序源码

🍓🍓文末获取联系🍓🍓 JAVAUniappMySQLWinForm 系统功能介绍

1、单/多门店自由切换;

2、扫码(桌号)点餐;

3、多规格商品;

4、手动/自动接单;

5、自助&am…

MyBatis-Plus标准数据层开发

1. 标准CRUD使用

对于标准的CRUD功能都有哪些以及MP都提供了哪些方法可以使用呢?

我们先来看张表:

功能自定义接口MP接口新增boolean save(T t)int insert(T t)删除boolean delete(int id)int deleteById(Serializeble id)修改boolean update(T t)int…

系统分析与设计 复习

文章目录系统分析与设计 复习第 1 章 系统分析与设计概述系统特性DevOps第 2 章 系统规划**系统规划步骤**规划模型诺兰模型**CMM 模型**系统规划方法战略集合转换法 SST关键成功因素法 CSF企业资源规划法 BSPCSB 三者联系和区别第 3 章系统分析系统分析概述业务流程图系统流程…

【微电网优化】萤火虫算法求解微电网优化问题【含Matlab源码 2146期】

⛄一、萤火虫算法求解微电网经济优化问题简介

利用迭代搜索法、剔除劣势策略法、逆推归纳法和最大最小优化方法[7,8,9]等均可实现博弈均衡点的求解。但当维数较大时, 这些方法可能存在搜索速度、路径和精度上的问题。萤火虫优化算法[10]由于其原理简单、参数少、易于实现、具有…

Maven中依赖无法导入的终极解决方案

maven依赖无法引入的问题解决 修改maven配置 添加阿里云的设置 阿里云云效maven官方配置指南 创建自己的maven库 jdk的导入设置 阿里云仓库官网 仓库服务 (aliyun.com) jar包下载所在位置 在命令终端进行jar包的引入 mvn install:install-file -Dfilejar包所在路径…

【SQLite】二、SQLite 和 HeidiSQL 的安装

作者主页:Designer 小郑 作者简介:浙江某公司软件工程师,负责开发管理公司OA、CRM业务系统,全栈领域优质创作者,CSDN学院、蓝桥云课认证讲师,开发过20余个前后端分离实战项目,主要发展方向为Vue…

生物素标记试剂:(1458576-00-5,1802908-00-4)Biotin-PEG4-alkyne,Dde-生物素-四聚乙二醇-炔

一、Biotin-PEG4-alkyne

【中文名称】生物素-四聚乙二醇-炔,生物素-四聚乙二醇-丙炔基 【英文名称】 Biotin-PEG4-alkyne 【CAS】1458576-00-5 【分子式】C21H35N3O6S 【分子量】457.58 【纯度】95% 【外观】 淡黄色或白色固体 (具体由其分子量大小决定…

web前端网页制作课作业:用DIV+CSS技术设计的静态网站【四大名著】中国传统文化主题题材设计

🎉精彩专栏推荐 💭文末获取联系 ✍️ 作者简介: 一个热爱把逻辑思维转变为代码的技术博主 💂 作者主页: 【主页——🚀获取更多优质源码】 🎓 web前端期末大作业: 【📚毕设项目精品实战案例 (10…

深入ftrace uprobe原理和功能介绍

上一章我们学习了,kprobe 可以实现动态内核的注入,基于中断的方法在任意指令中插入追踪代码,并且通过 pre_handler/post_handler去接收回调。另一个 kprobe 的同族是 kretprobe,只不过是针对函数级别的内核监控,根据用…

Arduino开发实例-RCWL0516微波雷达传感器驱动

RCWL0516微波雷达传感器驱动

接近感应是入侵警报、电灯开关以及其他家庭和工业自动化应用的常见应用。 电子工业中使用了多种接近检测方法。 最常见的方法是使用 PIR 传感器,它可以感应由温暖的身体引起的环境红外辐射的变化。 其他常见的方法包括使用反射的超声波或光束,其…

关于 SAP HANA 数据库的死锁问题(deadlock)

一个朋友在我的知识星球里提问: hana数据库发生死锁后,会自动解开吗?还是会等着自动超时后报错。 笔者在 15 年的 SAP 开发生涯中对 HANA 数据库接触得比较少,这里只能根据网络上搜索出的一些材料来回答。

首先,如果是…

卷出头了,终于学完阿里架构师推荐 413 页微服务分布式架构基础与实战笔记

时间飞逝,转眼间毕业七年多,从事 Java 开发也六年了。我在想,也是时候将自己的 Java 整理成一套体系。 这一次的知识体系面试题涉及到 Java 知识部分、性能优化、微服务、并发编程、开源框架、分布式等多个方面的知识点。 写这一套 Java 面试…

可视化大屏--响应式适配解决方案flexible.js

响应式适配解决方案flexible.js 最近公司开了第二个项目,是一个可视化大屏。 那么,在可视化大屏的基础上,我们肯定是要适配所有的屏幕设备,不能出现一换电脑,样式就紊乱的情况。 so,我们也不需要自己写媒体查询了&…