全部学习汇总: GreyZhang/g_tricore_architecture: some learning note about tricore architecture. (github.com)

中断一直是我想了解关注的一个功能模块,因为感觉不同的芯片上这部分的设计差异比较大。而这部分也跟我们嵌入式软件的设计模式直接相关。

1. 在TriCore内核中,中断服务的提供者可能有两个:CPU或者DMA通道。

2. 中断发生之后,ICU会利用SRPN(服务请求优先级编号)来判断,看一下哪一个请求会胜出。之后,胜出者设置为PENDING状态,然后与当前正在发生的中断进行优先级的比较看是否需要进行中断切换。

3. ICU的中断控制寄存器可以禁用以及使能全局中断,结合上面的描述来看,当前正在进行中的中断应该是禁不掉的,其相关的ISR还会继续进行。那么,PENDING状态的会是什么处理结果呢?单纯从结构上看,这个还是看不出来。

4. 从接下来的描述可以看得出来,我前面的疑问有了明确的答案。总结来说,那就是中断的切换需要考虑全局的中断使能。只有在全局中断使能的时候才会进行中断的切换。

5. 从可以阻断中断发生的几种条件来看,其实中断可以有相同的优先级出现,最简单的一个就是同一个中断出现了多次响应。

6. 如果CPU正在执行一个多周期的指令或者CPU正在修改ICR寄存器都是可以阻止中断发生的。

1. 进入到中断之后会开启管理员模式,这样就可以对所有的外设进行操作。

2. 从寄存器的调用层级限制可以看出来,中断的嵌套最多是支持64层的。

3. 在进入到中断服务之后,会开启对全局寄存器的写入保护。

4. 如果在中断服务发生的时候,不开启中断使能,那么应该不会出现中断的嵌套。

5. BISR指令比较特殊,可以保存被中断服务优先级的上下文低区。

1. ISR可以通过FRE退出;退出的时候,硬件会进行一个上下文保护,保存中断优先级以及中断使能标志。

2. ISR的入口在中断向量表中,位置由中断优先级来决定。

3. 中断发生之后,CPU根据中断优先级计算出来一个中断向量表中的位置,之后加载到PC寄存器。

4. BIV,中断向量表的基地址。可以通过BIV的修改来支持多个中断向量表的切换。

5. 限量表中的向量间距可以是8字节或者32字节,由BIV寄存器中的VSS来决定。

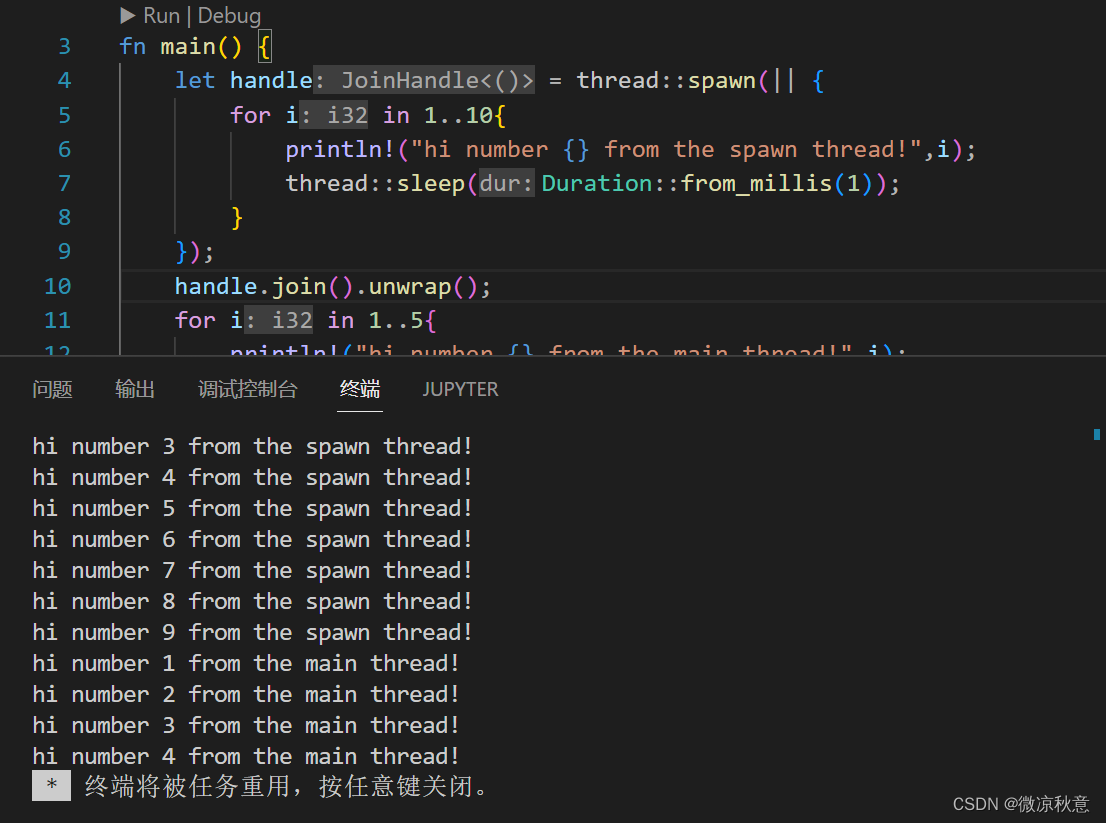

1. 这里给出来了8字节以及32字节的间距下的软件解析方式。

2. 如果中断ISR处理程序很小,可以在相关向量表代码中存储,否则要跨过所有向量跳转。

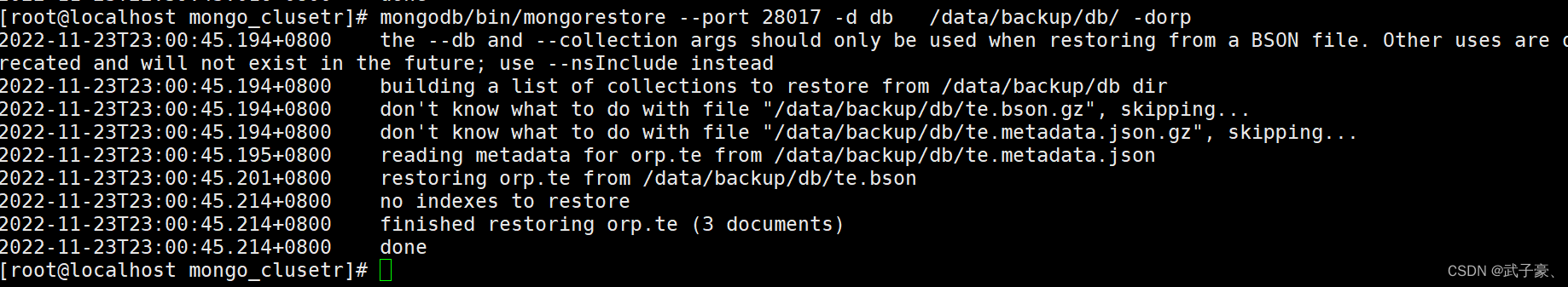

1. 这里的描述在其他的地方已经看到过,但是有点记不清,这里的默认地址是否在MCU的有效地址范围之内。

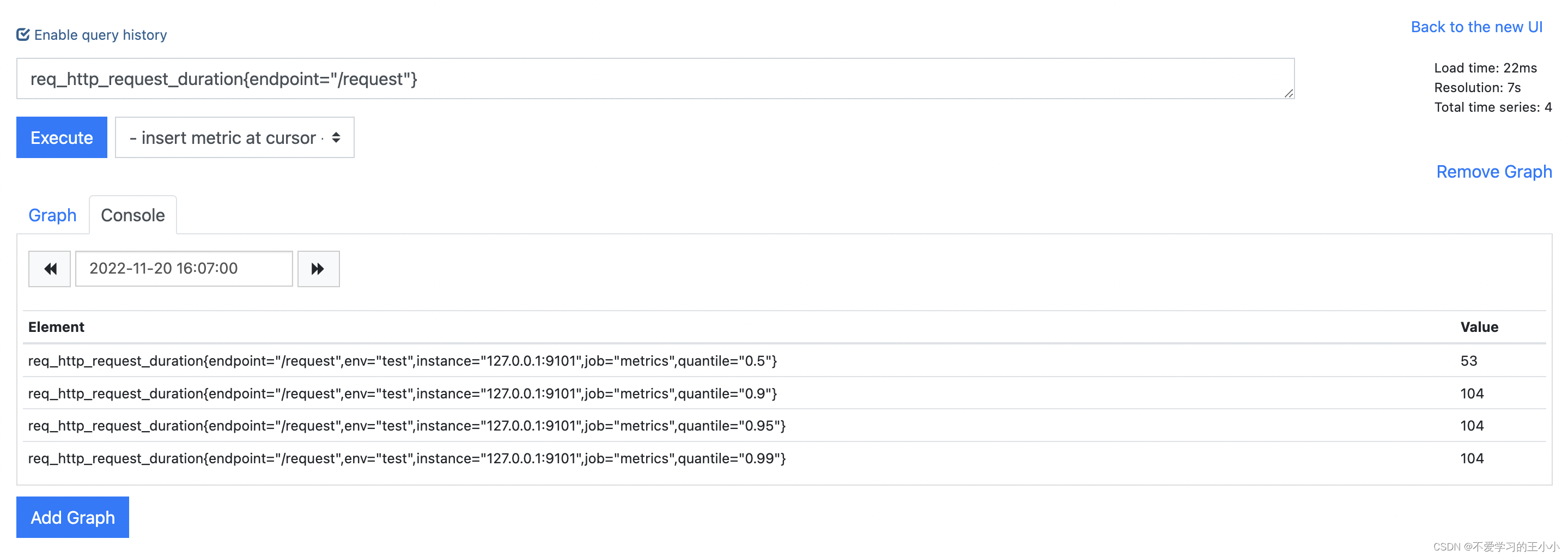

2. 从上面的图中可以看出来,如果有的中断向量没有用到,相应的空间可以给其他的ISR存储代码用。

1. 如果一个ISR跨了多个向量空间,那么被跨过的优先级就不能够在用了。但是,似乎这个只是限制了一个中断服务的提供方,对于DMA来说还是可以继续用的。

2. 中断优先组中的中断不能够相互中断,实现的方式其实是控制当前优先级的寄存器数值。然而,实现中断优先级组,只能够是支持连续的优先级。

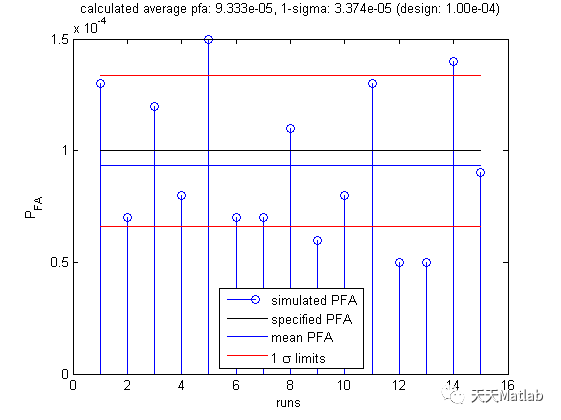

1. 结合这里的图,可以更好地理解中断优先级组的概念。

2. 从上面的描述看,这个优先级的高低其实是跟优先级的数值正相关的。数字越大,优先级越高。

1. 可以让一个中断支持两种优先级,拆分的时候需要有两个向量元素。这个中断ISR被拆分,拆分的阶段比较明确但是也是比较难考虑的。因为它本身是在执行的过程中发生了优先级的变化,而变化之后,由于架构本身的设计自然还得跳转到另一块向量区域。

2. 如果让一个中断源支持两个优先级,相对来说简单,只需要在向量中增加两个优先级的入口即可。

1. 中断的优先级是直接绑定中断向量运行实体的。

2. 相同的中断采用不同的优先级,要有不同的Vector Entry,不管是ISR拆分还是直接两套ISR。

3. 在创建向量表的时候需要考虑一个中断采用不同优先级的情况。

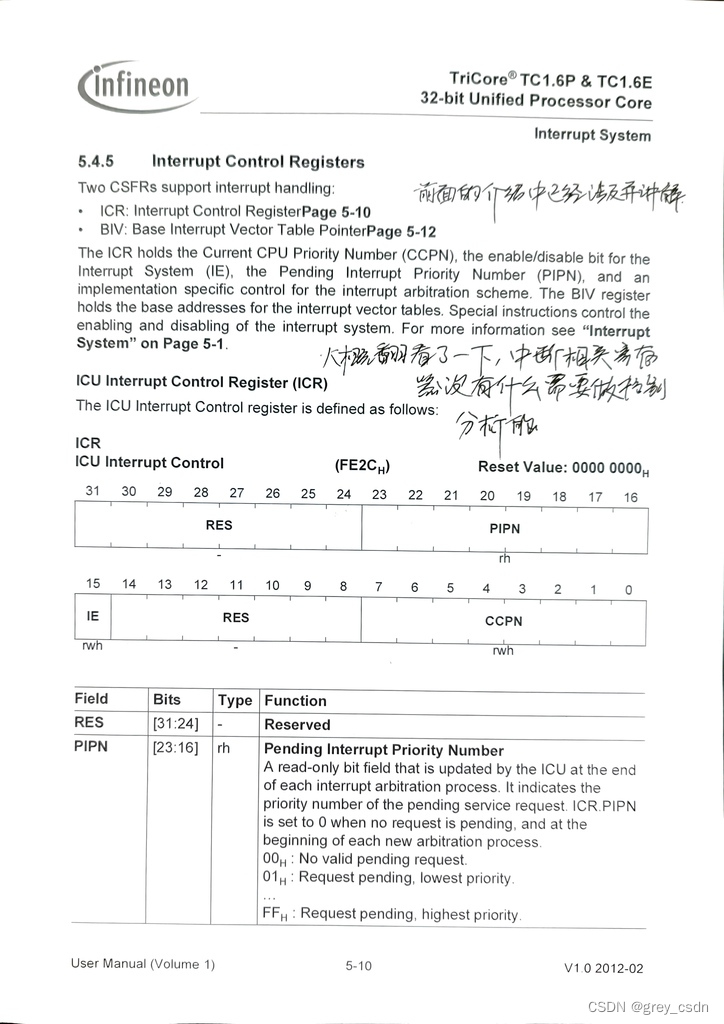

中断相关的寄存器其实没有太多需要关注的,在基本的中断系统介绍的时候穿插介绍了比较重要的部分。这里我就不再专门进行笔记梳理了。