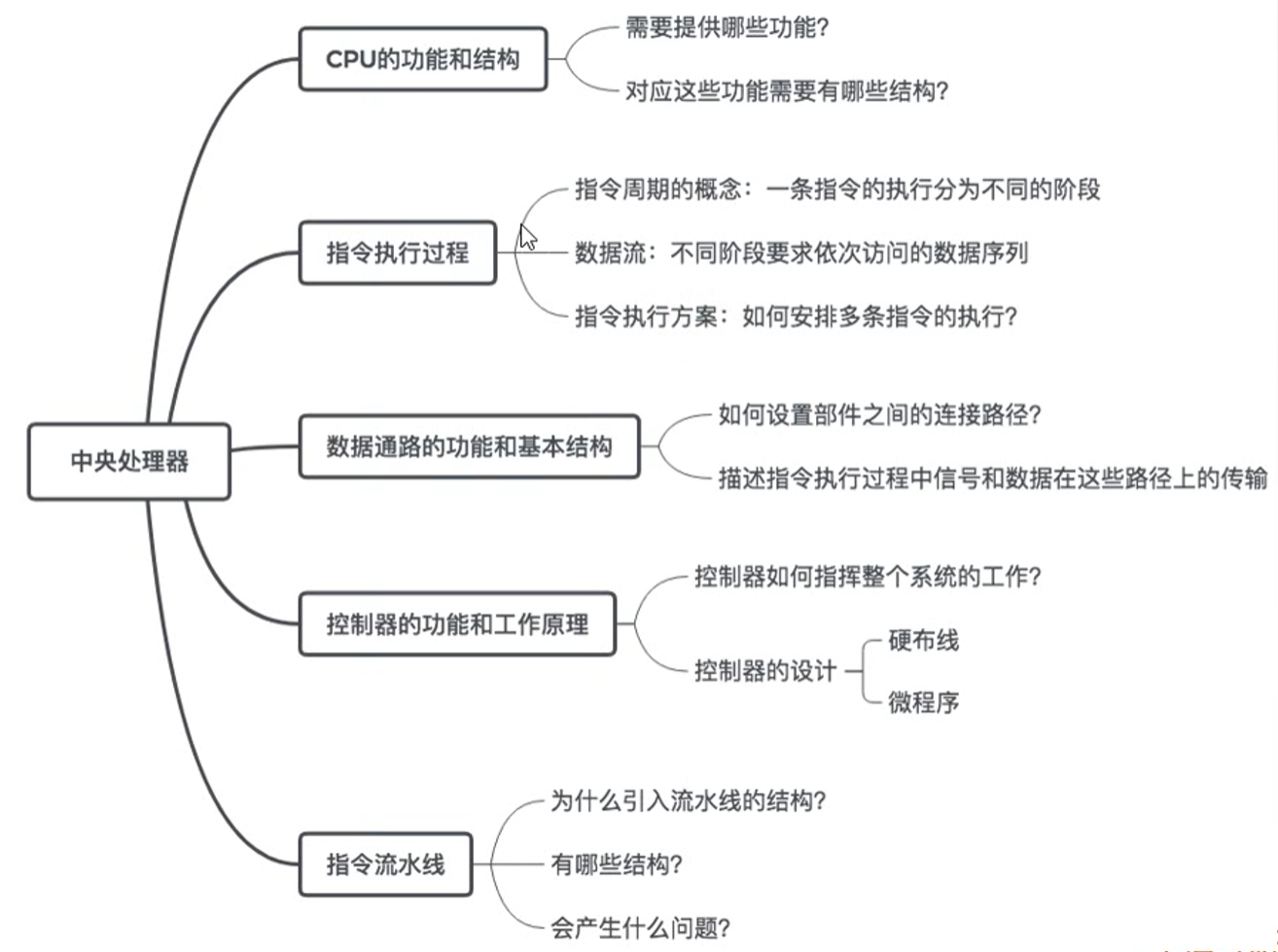

5.2 指令周期的数据流

5.2.1 指令周期

-

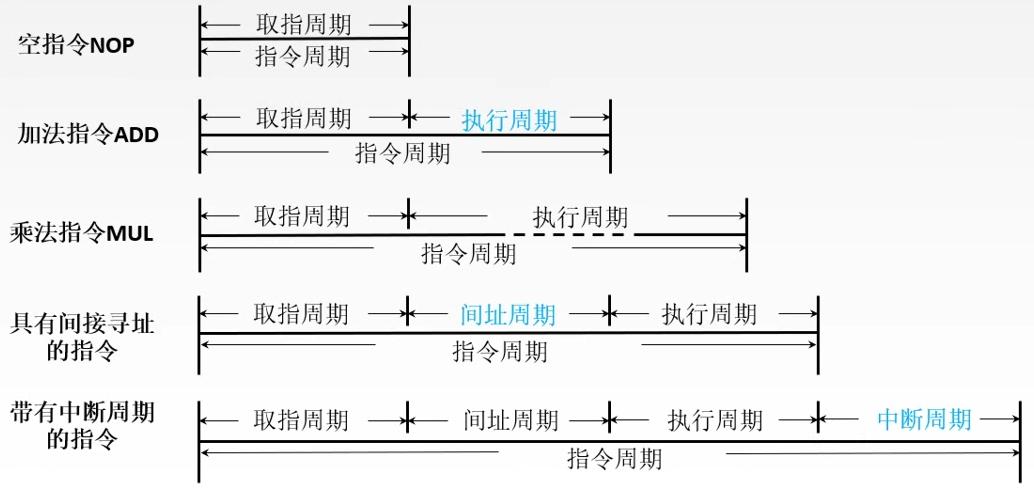

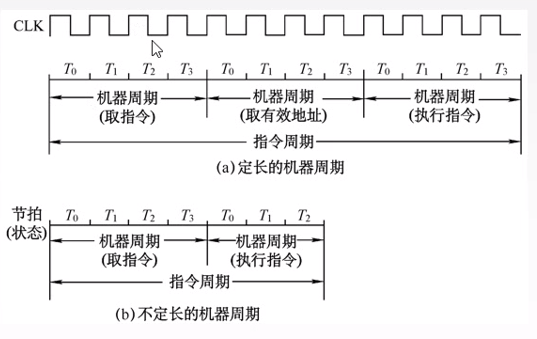

指令周期:CPU从主存中每取出并执行一条指令所需的全部时间。

-

指令周期:常常用若干机器周期来表示,机器周期又叫CPU周期。

-

一个机器周期又包含若干时钟周期(也称为节拍、T周期或CPU时钟周期,它是CPU操作的最基本单位,一个节拍,CPU完成最基本的操作。

可以发现每个指令周期内机器周期可以不等,每个机器周期内节拍数也可以不等。

每个指令需要完成的功能不同那么,就需要不同的指令周期,不同的节拍数

-

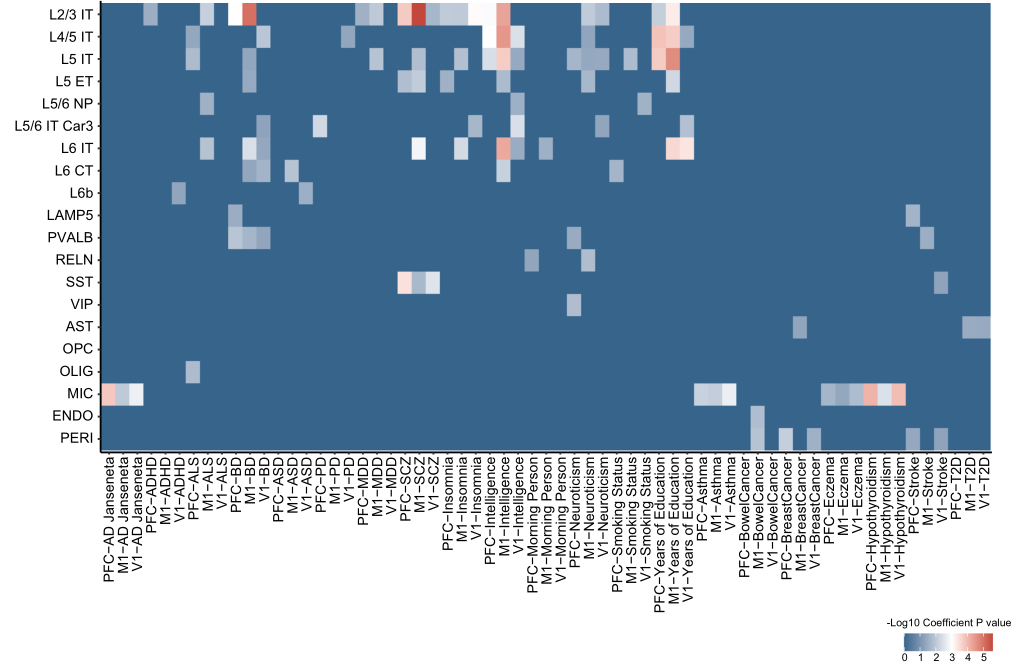

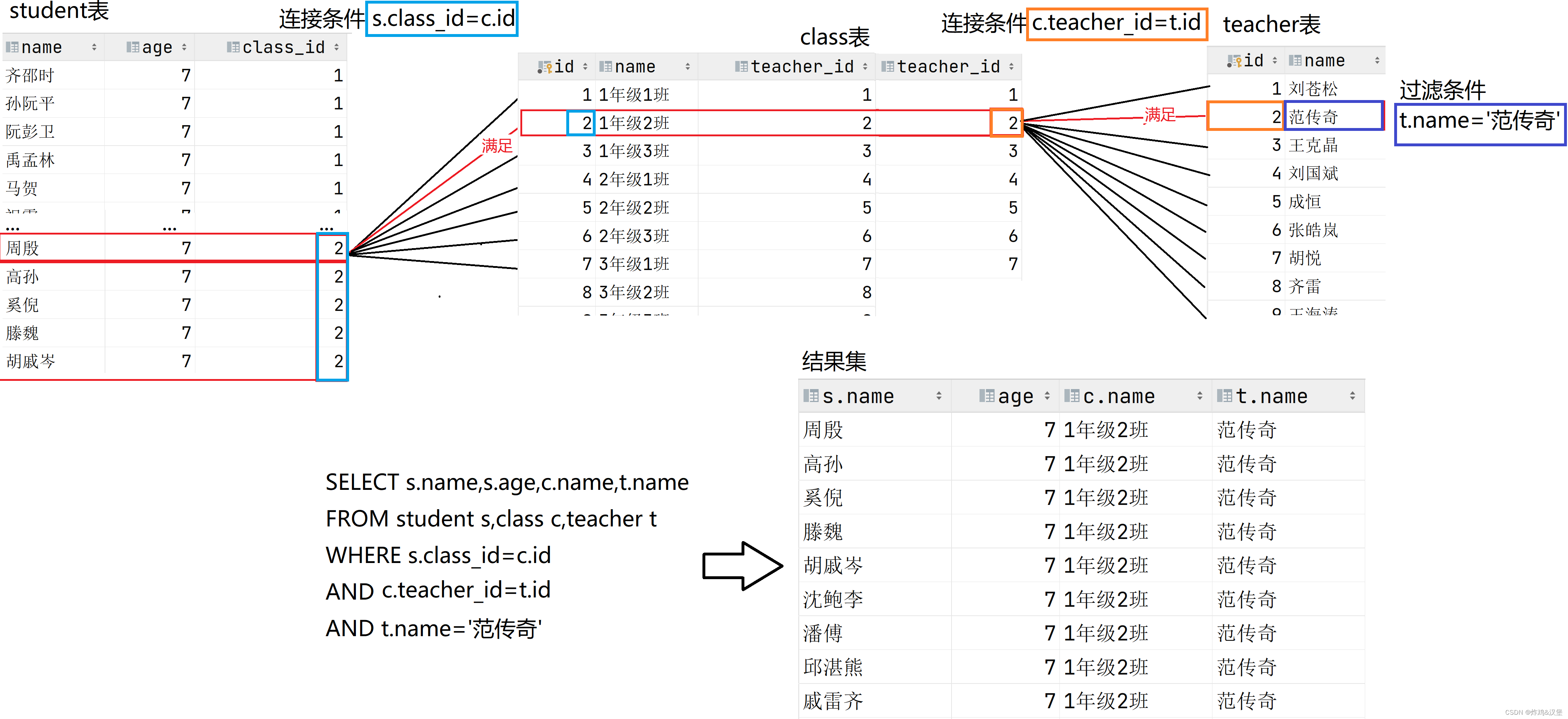

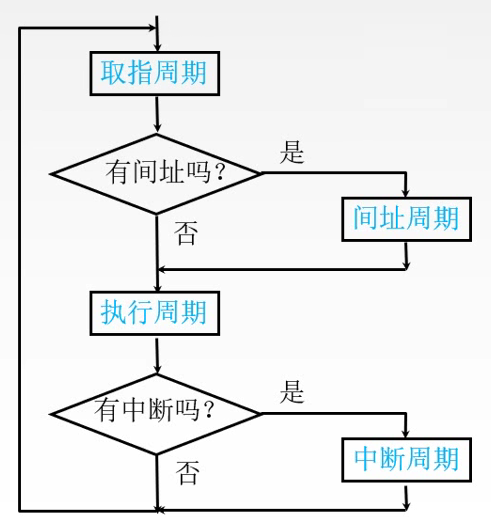

指令周期流程

通过对指令判断,来满足不同指令所需的不同指令周期

四个工作周期都有CPU访存操作,只是访存的目的不同。取指周期是为了取指令,间址周期是为了取有效地址,执行周期是为了取操作数,中断周期是为了保存程序断点。

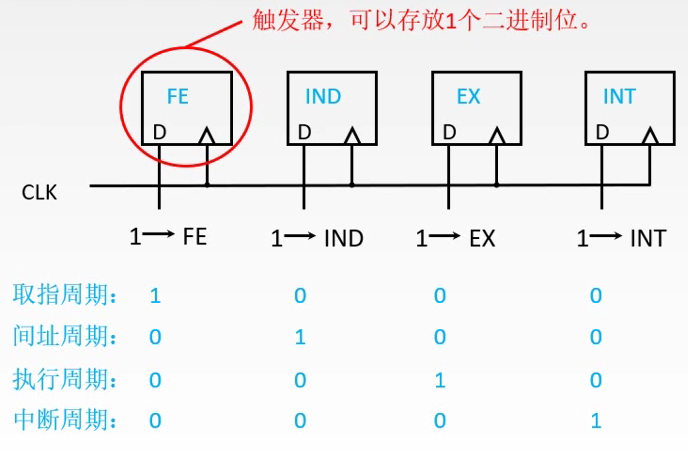

那么系统如何判断当前处于哪一个周期呢,答案是使用四个触发器对应不同的周期。

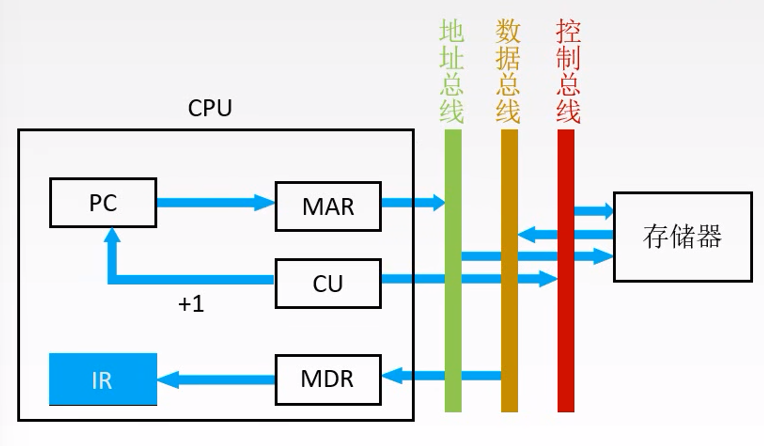

5.2.2 指令周期的数据流-取指周期

- 当前指令地址送至存储器地址寄存器,记做:(PC)→ MAR

- 由CU发出控制信号,经控制总线传到主存,这里是读信号,记做:1→R

- 存储器将MAR所指主存中的内容经数据总线送入MDR,记做:M(MAR)→MDR(M表示存储器,将存储器MAR位置数据放入MDR)

- 将MDR中的内容(此时是指令)送入IR,记做:(MDR)→IR

- CU发出控制信号,形成下一条指令地址,记做:(PC)+1 →PC

下面是工作流程,根据上面的步骤找出下方相应的箭头,体会取指周期(在这个周期内PC开始存放的是当前指令的地址,结束时存放的是下一条指令的地址)

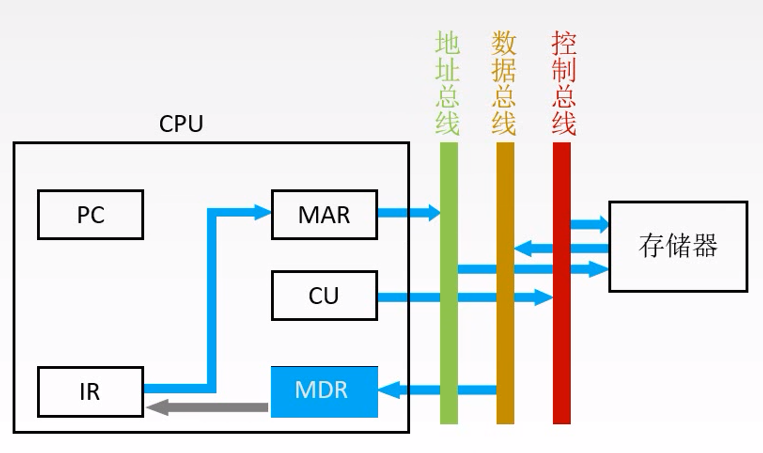

5.2.3 指令周期的数据流-间址周期

- 将指令的地址码送入MAR,记做:Ad(IR)→> MAR或Ad(MDR)→ MAR(此时MDR中存储的依旧是指令,但多数使用的是第一种表示形式)

- CU发出控制信号,启动主存做读操作,记做:1→R

- 将MAR所指主存中的内容经数据总线送入MDR,记做:M(MAR)→MDR

- 将有效地址送至指令的地址码字段,记做:MDR→ Ad(IR)。但有些系统就不会放到指令寄存器中,而是直接存储在存储器数据寄存器中,直接下一步当做有效地址寻址。(所以第四步不同的系统操作是不一样的)

5.2.4 指令周期的数据流-执行周期

执行周期的任务是根据IR中的指令字的操作码和操作数通过ALU操作产生执行结果。不同指令的执行周期操作不同,因此没有统一的数据流向。

5.2.5 指令周期的数据流-中断周期

中断:暂停当前任务去完成其他任务。为了能够恢复当前任务,需要保存断点。一般使用堆栈来保存断点,这里用SP表示栈顶地址,假设SP指向栈顶元素,进栈操作是先修改指针,后存入数据。

-

CU控制将SP减1,修改后的地址送入MAR(主存中选择一段空间作为堆栈,是高地址向低地址扩增的,所以入栈sp减,出栈sp加)

本质上是将断点存入某个存储单元,假设其地址为a,故可记做:a →MAR

-

CU发出控制信号,启动主存做写操作,记做: 1→w

-

将断点(PC内容)送入MDR,通过数据总线放入存储器中,记做:(PC)→MDR

-

CU控制将中断服务程序的入口地址(由向量地址形成部件产生)送入PC,记做:向量地址→PC

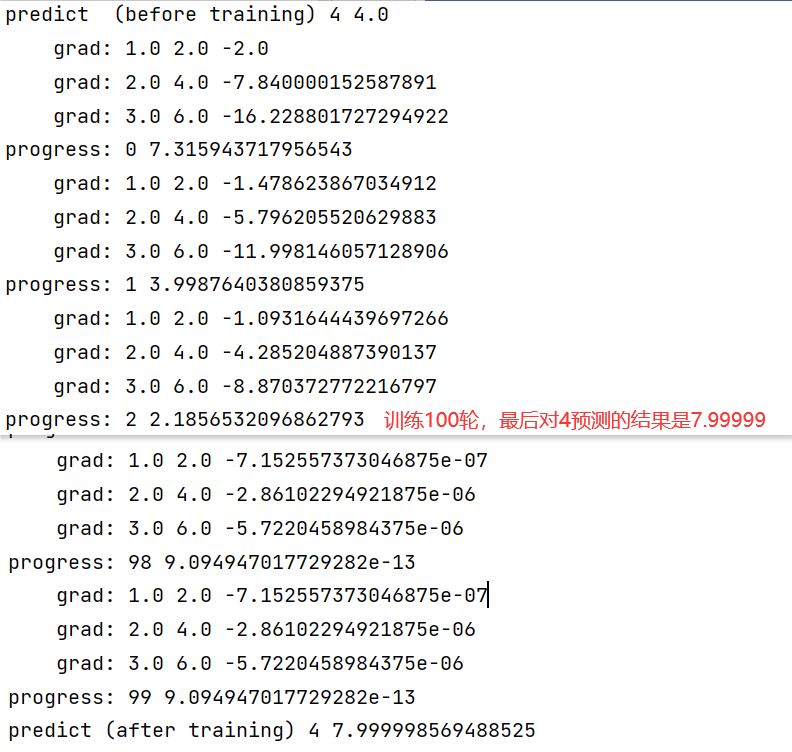

5.2.6 指令执行方案

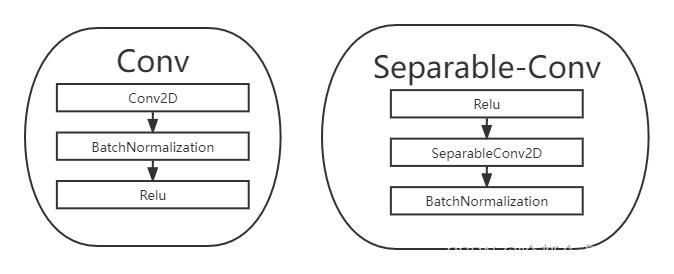

方案一:单指令周期

对所有指令都选用相同的执行时间来完成。指令之间串行执行;(一条指令执行完,下一条指令继续)指令周期取决于执行时间最长的指令的执行时间。

对于那些本来可以在更短时间内完成的指令,要使用这个较长的周期来完成,会降低整个系统的运行速度。

方案二:多指令周期

对不同类型的指令选用不同的执行步骤来完成。指令之间串行执行;(一条指令执行完,下一条指令继续)可选用不同个数的时钟周期来完成不同指令的执行过程。需要更复杂的硬件设计。

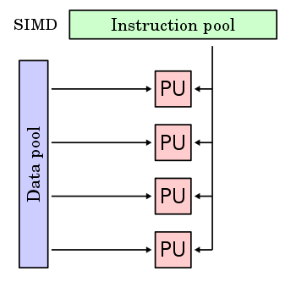

方案三:流水线方案(之后回详细讲解)

在每一个时钟周期启动一条指令,尽量让多条指令同时运行,但各自处在不同的执行步骤中。指令之间并行执行。(利用指令在不同的指令周期使用的硬件资源不同)